## MAX16990/MAX16992

# 36V, 2.5MHz Automotive Boost/ SEPIC Controllers

## **General Description**

The MAX16990/MAX16992 are high-performance, current-mode PWM controllers with 4 $\mu$ A (typ) shutdown current for wide input voltage range boost/SEPIC converters. The 4.5V to 36V input operating voltage range makes these devices ideal in automotive applications, such as front-end "preboost" or "SEPIC" power supplies and for the first boost stage in high-power LED lighting applications. An internal low-dropout regulator (PVL regulator) with a 5V output voltage enables the MAX16990/MAX16992 to operate directly from an automotive battery input. The input operating range can be extended to as low as 2.5V when the converter output is applied to the SUP input.

There are multiple versions of the devices offering one or more of the following functions: a synchronization output (SYNCO) for two-phase operation, an overvoltage protection function using a separate input pin (OVP), and a reference input pin (REFIN) to allow on-the-fly output voltage adjustment.

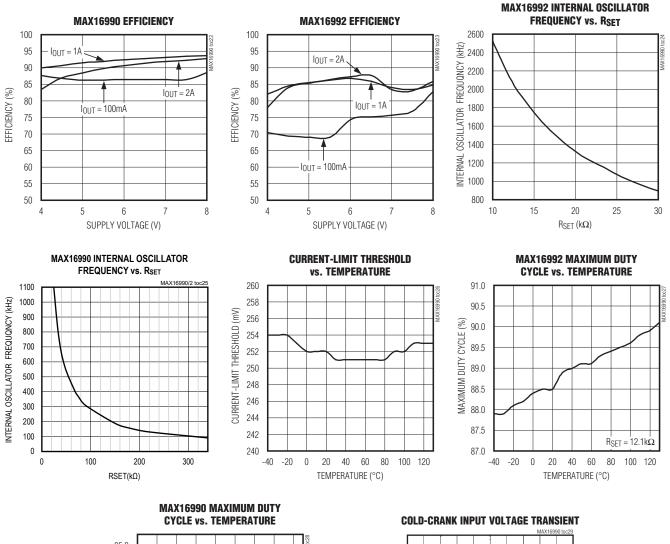

The MAX16990 and MAX16992 operate in different frequency ranges. All versions can be synchronized to an external master clock using the FSET/SYNC input.

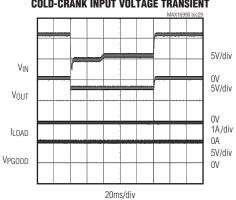

In addition, the MAX16990/MAX16992 have a factory-programmable spread-spectrum option. Both devices are available in compact 12-pin TQFN and 10-pin  $\mu$ MAX® packages.

## **Applications**

- Automotive LED Lighting

- Automotive Audio/Navigation Systems

- Dashboards

Ordering Information appears at end of data sheet.

μΜΑΧ is a registered trademark of Maxim Integrated Products, Inc.

## **Benefits and Features**

- Minimized Radio Interference with 2.5MHz Switching Frequency Above the AM Radio Band

- Space-Efficient Solution Design with Minimized External Components

- 100kHz to 1MHz (MAX16990) and 1MHz to 2.5MHz (MAX16992) Switching-Frequency Ranges

- 12-Pin TQFN (3mm x 3mm) and 10-Pin μMAX Packages

- Spread Spectrum Simplifies EMI Management Design

- Flexibility with Available Configurations for Boost, SEPIC, and Multiphase Applications

- Adjustable Slope Compensation

- · Current-Mode Control

- Internal Soft-Start (9ms)

- Protection Features Support Robust Automotive Applications

- Operating Voltage Range Down to 4.5V (2.5V or Lower in Bootstrapped Mode), Immune to Load-Dump Transient Voltages Up to 42V

- PGOOD Output and Hiccup Mode for Enhanced System Protection

- · Overtemperature Shutdown

- -40°C to +125°C Operation

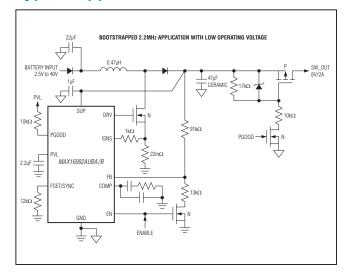

# **Typical Application Circuit**

## MAX16990/MAX16992

# 36V, 2.5MHz Automotive Boost/ SEPIC Controllers

# **Absolute Maximum Ratings**

| EN, SUP, OVP, FB to GND0.3V to +42V                   |

|-------------------------------------------------------|

| DRV, SYNCO, FSET/SYNC, COMP,                          |

| PGOOD, ISNS, REFIN to GND0.3V to (VPVL + 0.3V)        |

| PVL to GND0.3V to 6V                                  |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

| μMAX on SLB (derate 10.3mW/°C above +70°C)825mW       |

| μMAX on MLB (derate 12.9mW/°C above +70°C)1031mW      |

| TQFN on SLB (derate 13.2mW/°C above +70°C)1053mW      |

| TQFN on MLB (derate 21.32mW/°C above +70°C)1705mW     |

| Operating Temperature Range       | 40°C to +125°C |

|-----------------------------------|----------------|

| Maximum Junction Temperature      | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

|                                   |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Thermal Characteristics (Note 1)**

| μMAX (Single-Layer Board)                                 |        |

|-----------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) | 97°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )    | .5°C/W |

| μMAX (Four-Layer Board)                                   |        |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) | 78°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )    | .5°C/W |

| TQFN (Single-Layer Board)                              |          |

|--------------------------------------------------------|----------|

| Junction-to-Ambient Thermal Resistance $(\theta_{JA})$ | 76°C/W   |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 11°C/W   |

| TQFN (Four-Layer Board)                                |          |

| Junction-to-Ambient Thermal Resistance $(\theta_{JA})$ | 46.9°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 5.27°C/W |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maximintegrated.com/thermal-tutorial**.

## **Electrical Characteristics**

$(V_{SUP} = 14V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                              | SYMBOL            | СО                         | MIN      | TYP | MAX  | UNITS |                         |

|----------------------------------------|-------------------|----------------------------|----------|-----|------|-------|-------------------------|

| POWER SUPPLY                           |                   |                            |          |     |      |       |                         |

| SUP Operating Supply Range             | V <sub>SUP</sub>  |                            |          | 4.5 |      | 36    | V                       |

| SLID Supply Current in Operation       | I                 | V <sub>FB</sub> = 1.1V, no | MAX16990 |     | 0.75 | 1.3   | mA                      |

| SUP Supply Current in Operation        | Icc               | switching                  | MAX16992 |     | 1.25 | 2     | IIIA                    |

| SUP Supply Current in Shutdown         | I <sub>SHDN</sub> | V <sub>EN</sub> = 0V       |          |     | 4    | 7     | μA                      |

| OVP Threshold Voltage                  | V <sub>OVP</sub>  | OVP rising                 |          | 105 | 110  | 115   | % of<br>V <sub>FB</sub> |

| OVP Threshold Voltage<br>Hysteresis    | V <sub>OVPH</sub> |                            |          |     | 2.5  |       | % of<br>V <sub>FB</sub> |

| OVP Input Current                      | I <sub>OVP</sub>  |                            |          | -1  |      | +1    | μA                      |

| PVL REGULATOR                          |                   |                            |          | ·   |      |       |                         |

| PVL Output Voltage                     | V <sub>PVL</sub>  |                            |          | 4.7 | 5    | 5.3   | V                       |

| PVL Undervoltage Lockout               | V <sub>UV</sub>   | SUP rising                 |          | 3.8 | 4    | 4.3   | V                       |

| PVL Undervoltage-Lockout<br>Hysteresis | V <sub>UVH</sub>  |                            |          |     | 0.4  |       | V                       |

# **Electrical Characteristics (continued)**

$(V_{SUP} = 14V, T_A = T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                         | SYMBOL             | COND                             | ITIONS                  | MIN   | TYP  | MAX   | UNITS                   |

|---------------------------------------------------|--------------------|----------------------------------|-------------------------|-------|------|-------|-------------------------|

| OSCILLATOR                                        |                    |                                  |                         |       |      |       |                         |

| Outitable of Francisco                            |                    | $R_{FSET} = 69k\Omega$           |                         | 360   | 400  | 440   | 1.11=                   |

| Switching Frequency                               | fsw                | R <sub>FSET</sub> = 12kΩ         |                         |       |      | 2400  | kHz                     |

| Spread-Spectrum Spreading Factor                  | SS                 | B, D, and F versions             |                         |       | Q6   |       | % of<br>f <sub>SW</sub> |

| Contraction Francisco Decision                    | · ·                | When set with                    | MAX16990                | 100   |      | 1000  |                         |

| Switching Frequency Range                         | f <sub>SWR</sub>   | resistor on pin                  | MAX16992                | 1000  |      | 2500  | kHz                     |

| ESET/SVNC Frequency Bongs                         | f                  | Using external                   | MAX16990                | 220   |      | 1000  | k∐⇒                     |

| FSET/SYNC Frequency Range                         | fsync              | SYNC signal                      | MAX16992                | 1000  |      | 2500  | kHz                     |

| FSET Regulation Voltage                           | V <sub>FSET</sub>  | 12kΩ < R <sub>FSET</sub> < 69kΩ  | Ω                       |       | 0.9  |       | V                       |

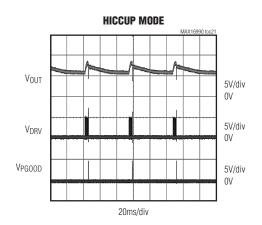

| Soft-Start Time                                   | t <sub>SS</sub>    | Internally set                   |                         | 6     | 9    | 12    | ms                      |

| Hiccup Period                                     | tHICCUP            |                                  |                         |       | 55   |       | ms                      |

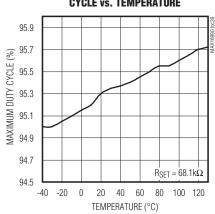

| Marrian Duty Ovels                                | DC                 | MAX16990, R <sub>FSET</sub> =    | 69kΩ                    | 93    |      |       | 0/                      |

| Maximum Duty Cycle                                | DC <sub>MAX</sub>  | MAX16992, R <sub>FSET</sub> =    | 12kΩ                    | 85    |      |       | %                       |

| Minimum On-Time                                   | t <sub>ON</sub>    |                                  |                         | 50    | 80   | 110   | ns                      |

| THERMAL SHUTDOWN                                  |                    |                                  |                         |       |      |       |                         |

| Thermal-Shutdown Temperature                      | TS                 | Temperature rising               |                         |       | 165  |       | °C                      |

| Thermal-Shutdown Hysteresis                       | T <sub>H</sub>     |                                  |                         |       | 10   |       | °C                      |

| GATE DRIVERS                                      |                    |                                  |                         |       |      |       |                         |

| DRV Pullup Resistance                             | R <sub>DRVH</sub>  | I <sub>DRV</sub> = 100mA         |                         |       | 3    | 5.5   | Ω                       |

| DRV Pulldown Resistance                           | R <sub>DRVL</sub>  | I <sub>DRV</sub> = -100mA        |                         |       | 1.4  | 2.5   | Ω                       |

| DDV Outset Deels Ousset                           |                    | Sourcing, C <sub>DRV</sub> = 10r | nF                      |       | 0.75 |       | ^                       |

| DRV Output Peak Current                           | I <sub>DRV</sub>   | Sinking, C <sub>DRV</sub> = 10nF | =                       |       | 1    |       | Α                       |

| REGULATION/CURRENT SENSE                          |                    |                                  |                         |       |      |       | ,                       |

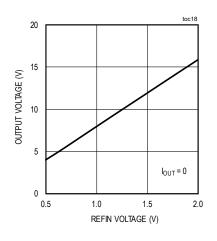

|                                                   |                    | V <sub>REFIN</sub> = VPVL        | Across full line, load, | 0.99  | 1    | 1.01  |                         |

| FB Regulation Voltage                             | V <sub>FB</sub>    | V <sub>REFIN</sub> = 2V          | and temperature         | 1.98  | 2    | 2.02  | V                       |

|                                                   |                    | V <sub>REFIN</sub> = 0.5V        | range                   | 0.495 | 0.5  | 0.505 |                         |

| FB Input Current                                  | I <sub>FB</sub>    |                                  |                         | -0.5  |      | +0.5  | μA                      |

| ISNS Threshold                                    |                    |                                  |                         | 212   | 250  | 288   | mV                      |

| ISNS Leading-Edge Blanking                        |                    | MAX16990                         |                         | 60    |      | F-2   |                         |

| Time                                              | <sup>t</sup> BLANK | MAX16992                         |                         |       | 40   |       | ns                      |

| Current-Sense Gain                                | A <sub>VI</sub>    |                                  |                         | 8     |      | V/V   |                         |

| Peak Slope Compensation<br>Current-Ramp Magnitude |                    | Added to ISNS input              |                         | 40    | 50   | 60    | μΑ                      |

| DOOOD Three-ball                                  | .,                 | Percentage of final              | Rising                  | 85    | 90   | 95    | 0.1                     |

| PGOOD Threshold                                   | V <sub>PG</sub>    | value                            | Falling                 | 80    | 85   | 90    | %                       |

# **Electrical Characteristics (continued)**

$(V_{SUP} = 14V, T_A = T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                             | SYMBOL            | CONDITIONS                                  | MIN                    | TYP                    | MAX                    | UNITS |

|---------------------------------------|-------------------|---------------------------------------------|------------------------|------------------------|------------------------|-------|

| ERROR AMPLIFIER                       |                   |                                             |                        |                        |                        |       |

| REFIN Input Voltage Range             |                   |                                             | 0.5                    |                        | 2                      | V     |

| REFIN Threshold for 1V FB Regulation  |                   |                                             | V <sub>PVL</sub> - 0.8 | V <sub>PVL</sub> - 0.4 | V <sub>PVL</sub> - 0.1 | V     |

| Error-Amplifier gm                    | A <sub>VEA</sub>  |                                             |                        | 700                    |                        | μS    |

| Error-Amplifier Output Impedance      | R <sub>OEA</sub>  |                                             |                        | 50                     |                        | МΩ    |

| COMP Output Current                   | I <sub>COMP</sub> |                                             |                        | 140                    |                        | μA    |

| COMP Clamp Voltage                    |                   |                                             | 2.7                    | 3                      | 3.3                    | V     |

| LOGIC-LEVEL INPUTS/OUTPUTS            | 3                 |                                             |                        |                        |                        |       |

| PGOOD/SYNCO Output Leakage<br>Current |                   | V <sub>PGOOD</sub> /V <sub>SYNCO</sub> = 5V |                        | 0.5                    |                        | μA    |

| PGOOD/SYNCO Output Low<br>Level       |                   | Sinking 1mA                                 |                        |                        | 0.4                    | V     |

| EN High Input Threshold               |                   | EN rising                                   | 1.7                    |                        |                        | V     |

| EN Low Input Threshold                |                   |                                             |                        |                        | 1.2                    | V     |

| FSET/SYNC High Input<br>Threshold     |                   |                                             | 2.5                    |                        |                        | V     |

| FSET/SYNC Low Input Threshold         |                   |                                             |                        |                        | 1                      | V     |

| EN and REFIN Input Current            |                   |                                             | -1                     |                        | +1                     | μA    |

Note 2: All devices 100% production tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

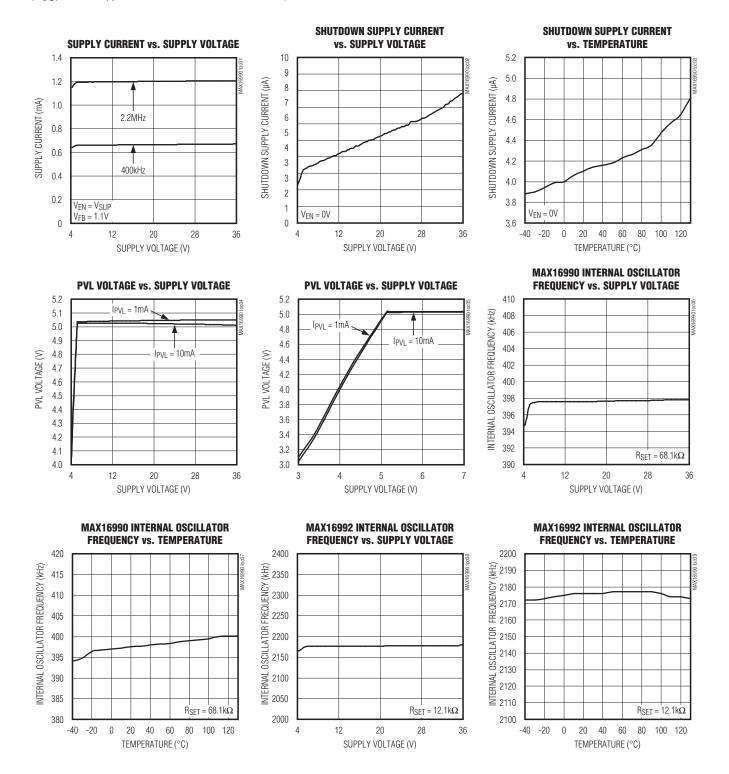

## **Typical Operating Characteristics**

( $V_{SUP}$  = 14V,  $T_A$  = +25°C, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

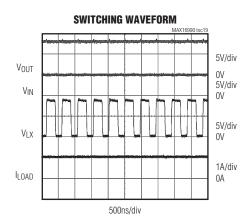

$(V_{SUP} = 14V, T_A = +25^{\circ}C, unless otherwise noted.)$

# 36V, 2.5MHz Automotive Boost/ SEPIC Controllers

# **Typical Operating Characteristics (continued)**

$(V_{SUP} = 14V, T_A = +25^{\circ}C, unless otherwise noted.)$

# VSUP 5V/div OV 5V/div OV 1A/div (AC-COUPLED) 1A/div OA

#### **OUTPUT VOLTAGE vs. REFIN VOLTAGE**

# **Typical Operating Characteristics (continued)**

( $V_{SUP}$  = 14V,  $T_A$  = +25°C, unless otherwise noted.)

# **Pin Configurations**

# **Pin Descriptions**

| MAX16990AUBA/B,<br>MAX16992AUBA/B<br>μΜΑΧ-ΕΡ | MAX16990ATCC/D,<br>MAX16992ATCC/D | MAX16990ATCE/F,<br>MAX16992ATCE/F | NAME | FUNCTION                                                                                                                                                                                                                     |

|----------------------------------------------|-----------------------------------|-----------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                            | 1 1 1                             | 1 1 1                             | SUP  | Power-Supply Input. Place a bypass capacitor of at least 1µF between this pin and ground.                                                                                                                                    |

| 2                                            | 3                                 | 3                                 | EN   | Active-High Enable Input. This input is high-voltage-capable or can alternatively be driven from a logic-level signal.                                                                                                       |

| 3                                            | 2                                 | 2                                 | GND  | Ground Connection                                                                                                                                                                                                            |

| 4                                            | 4                                 | 4                                 | DRV  | Drive Output for Gate of nMOS Boost Switch. The nominal voltage swing of this output is between PVL and GND.                                                                                                                 |

| 5                                            | 5                                 | 5                                 | PVL  | Output of 5V Internal Regulator. Connect a ceramic capacitor of at least 2.2µF from this pin to ground, placing it as close as possible to the pin.                                                                          |

| 6                                            | 6                                 | 6                                 | ISNS | Current-Sense Input to Regulator. Connect a sense resistor between the source of the external switching FET and GND. Then connect another resistor between ISNS and the source of the FET for slope compensation adjustment. |

# **Pin Descriptions (continued)**

| MAX16990AUBA/B,<br>MAX16992AUBA/B | MAX16990ATCC/D,<br>MAX16992ATCC/D | MAX16990ATCE/F,<br>MAX16992ATCE/F | NAME          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|-----------------------------------|-----------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| μMAX-EP                           | TQFN-EP                           | TQFN-EP                           |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| _                                 | _                                 | 7                                 | SYNCO         | Open-Drain Synchronization Output. SYNCO outputs a square-wave signal which is 180° out-of-phase with the device's operational clock. Connect a pullup resistor from this pin to PVL or to a 5V or lower supply when used.                                                                                                                                                                                                                                                                         |

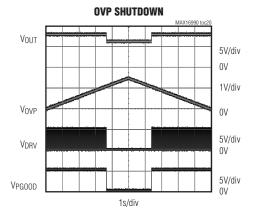

| _                                 | 7                                 | _                                 | OVP           | Overvoltage Protection Input. When this pin goes above 110% of the FB regulation voltage, all switching is disabled. Operation resumes normally when OVP drops below 107.5% of the FB regulation point. Connect a resistor divider between the output, OVP, and GND to set the overvoltage protection level.                                                                                                                                                                                       |

| _                                 | 8                                 | 8                                 | REFIN         | Reference Input. When using the internal reference, connect REFIN to PVL. Otherwise, drive this pin with an external voltage between 0.5V and 2V to set the boost output voltage.                                                                                                                                                                                                                                                                                                                  |

| 7                                 | 9                                 | 9                                 | PGOOD         | Open-Drain Power-Good Output. Connect a resistor from this pin to PVL or to another voltage less than or equal to 5V. PGOOD goes high after soft-start when the output exceeds 90% of its final value. When EN is low, PGOOD is also low. After soft-start is complete, if PGOOD goes low and 16 consecutive current-limit cycles occur, the devices enter hiccup mode and a new soft-start is initiated after a delay of 44ms.                                                                    |

| 8                                 | 10                                | 10                                | FSET/<br>SYNC | Frequency Set/Synchronization. To set a switching frequency between 100kHz and 1000kHz (MAX16990) or between 1000kHz and 2500kHz (MAX16992), connect a resistor from this pin to GND. To synchronize the converter, connect a logic signal in the range 220kHz to 1000kHz (MAX16990) or 1000kHz to 2500kHz (MAX16992) to this input. The external n-channel MOSFET is turned on (i.e., DRV goes high) after a short delay (60ns for 2.2MHz operation, 125ns for 400kHz) when SYNC transitions low. |

| 9                                 | 11                                | 11                                | COMP          | Output of Error Amplifier. Connect the compensation network between COMP and GND.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10                                | 12                                | 12                                | FB            | Boost Converter Feedback. This pin is regulated to 1V when REFIN is tied to PVL or otherwise regulated to REFIN during boost operation. Connect a resistor divider between the boost output, the FB pin, and GND to set the boost output voltage. In a two-phase converter, connect the FB pin of the slave IC to PVL.                                                                                                                                                                             |

# **Pin Descriptions (continued)**

| MAX16990AUBA/B,<br>MAX16992AUBA/B<br>μMAX-EP | MAX16990ATCC/D,<br>MAX16992ATCC/D<br>TQFN-EP | MAX16990ATCE/F,<br>MAX16992ATCE/F<br>TQFN-EP | NAME | FUNCTION                                                                                                                                                   |

|----------------------------------------------|----------------------------------------------|----------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _                                            | _                                            | _                                            | EP   | Exposed Pad. Internally connected to GND. Connect to a large ground plane to maximize thermal performance. Not intended as an electrical connection point. |

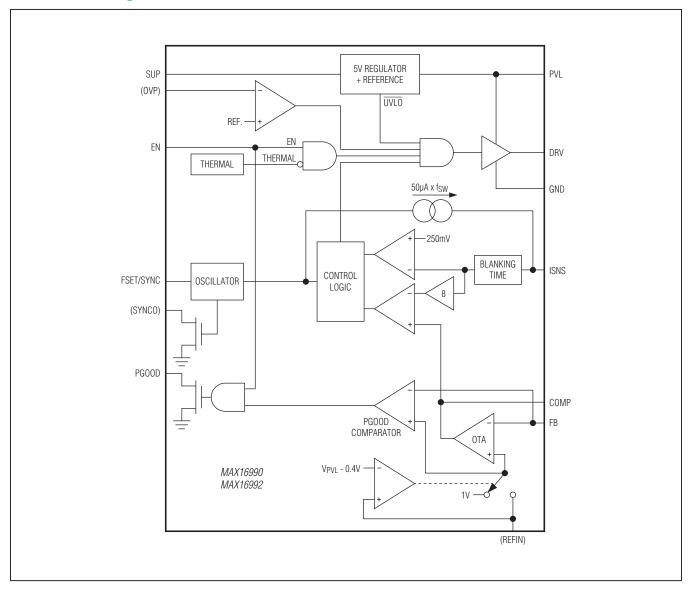

# **Functional Diagram**

## **Detailed Description**

The MAX16990/MAX16992 are high-performance, current-mode PWM controllers for wide input voltage range boost/SEPIC converters. The input operating voltage range of 4.5V to 36V makes these devices ideal in automotive applications such as for front-end "preboost" or "SEPIC" power supplies and for the first boost stage in high-power LED lighting applications. An internal low-dropout regulator (PVL regulator) with an output voltage of 5V enables the devices to operate directly from an automotive battery input. The input operating range can be as low as 2.5V when the converter output supplies the SUP input.

The input undervoltage lockout (UVLO) circuit monitors the PVL voltage and turns off the converter when the voltage drops below 3.6V (typ). An external resistor programs the switching frequency in two ranges from 100kHz to 1000kHz (MAX16990) or between 1000kHz and 2500kHz (MAX16992). The FSET/SYNC input can also be used for synchronization to an external clock. The SYNC pulse width should be greater than 70ns.

Inductor current information is obtained by means of an external sense resistor connected from the source of the external n-channel MOSFET to GND.

The devices include an internal transconductance error amplifier with 1% accurate reference. At startup, the internal reference is ramped in a time of 9ms to obtain soft-start.

The devices also include protection features such as hiccup mode and thermal shutdown, as well as an optional overvoltage-detection circuit (OVP pin, C and D versions).

## **Current-Mode Control Loop**

The MAX16990/MAX16992 offers peak current-mode control operation for best load-step performance and simpler compensation. The inherent feed-forward characteristic is especially useful in automotive applications where the input voltage changes quickly during cold-crank and load-dump conditions. While the current-mode architecture offers many advantages, there are some shortcomings. In high duty-cycle operation, subharmonic oscillations can occur. To avoid this, the device offers programmable slope compensation using a single resistor between the ISNS pin and the current-sense resistor. To avoid premature turn-off at the beginning of the on-cycle, the current-limit and PWM comparator inputs have leading-edge blanking.

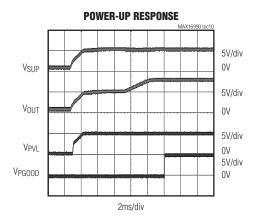

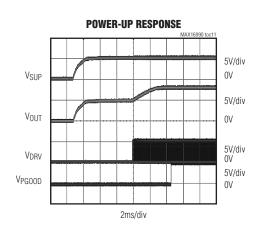

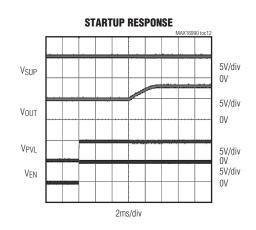

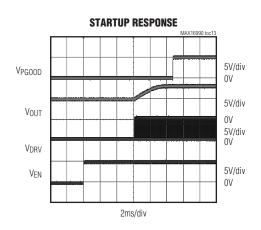

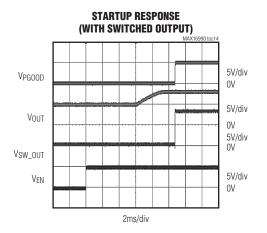

#### Startup Operation/UVLO/EN

The devices feature undervoltage lockout on the PVL-regulator and turn on the converter once PVL rises above 4V. The internal UVLO circuit has about 400mV hysteresis to avoid chattering during turn-on. Once the converter is operating and if SUP is fed from the output, the converter input voltage can drop below 4.5V. This feature allows operation at cold-crank voltages as low as 2.5V or even lower with careful selection of external components. The EN input can be used to disable the device and reduce the standby current to less than 4µA (typ).

#### Soft-Start

The devices are provided with an internal soft-start time of 9ms. At startup, after voltage is applied and the UVLO threshold is reached, the device enters soft-start. During soft-start, the reference voltage ramps linearly to its final value in 9ms.

#### Oscillator Frequency/External Synchronization/ Spread Spectrum

Use an external resistor at FSET/SYNC to program the MAX16990 internal oscillator frequency from 100kHz to 1MHz and the MAX16992 frequency between 1MHz and 2.5MHz. See TOCs 24 and 25 in the <u>Typical Operating Characteristics</u> section for resistor selection.

The SYNCO output is a 180° phase-shifted version of the internal clock, and can be used to synchronize other converters in the system or to implement a two-phase boost converter with a second MAX16990/MAX16992. The advantages of a two-phase boost topology are lower input and output ripple and simpler thermal management as the power dissipation is spread over more components. See the <u>Multiphase Operation</u> section for further details.

The devices can be synchronized using an external clock at the FSET/SYNC input. A falling clock edge on FSET/SYNC turns on the external MOSFET by driving DRV high after a short delay.

The B, D, and F versions of the devices have spread-spectrum oscillators. In these parts, the internal oscillator frequency is varied dynamically  $\pm 6\%$  around the switching frequency. Spread spectrum can improve system EMI performance by reducing the height of peaks due to the switching frequency and its harmonics in the spectrum. The SYNCO output includes spread-spectrum modulation when the internal oscillator is used on the B, D, and F versions. Spread spectrum is not active when an external clock is applied to the FSET/SYNC pin.

#### n-Channel MOSFET Driver

DRV drives the gate of an external n-channel MOSFET. The driver is powered by the internal regulator (PVL), which provides approximately 5V. This makes both the devices suitable for use with logic-level MOSFETs. DRV can source 750mA and sink 1000mA peak current. The average current sourced by DRV depends on the switching frequency and total gate charge of the external MOSFET (see the *Power Dissipation* section).

## **Error Amplifier**

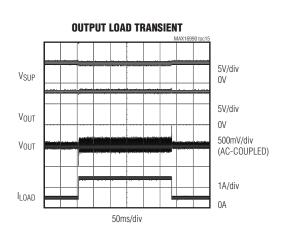

The devices include an internal transconductance error amplifier. The noninverting input of the error amplifier is connected to the internal 1V reference and feedback is provided at the inverting input. High 700 $\mu S$  open-loop transconductance and  $50M\Omega$  output impedance allow good closed-loop bandwidth and transient response. Moreover, the source and sink current capability of  $140\,\mu A$  provides fast error correction during output load transients.

## **Slope Compensation**

The devices use an internal current-ramp generator for slope compensation. The internal ramp signal resets at the beginning of each cycle and slews at a typical rate of  $50\mu A$  x f<sub>SW</sub>. The amount of slope compensation needed depends on the slope of the current ramp in the inductor. See the <u>Current-Sense Resistor Selection and Setting Slope Compensation</u> section for further information.

#### **Current Limit**

The current-sense resistor (R<sub>CS</sub>) connected between the source of the MOSFET and ground sets the current limit. The ISNS input has a voltage trip level (V<sub>CS</sub>) of 250mV. When the voltage produced by the current in the inductor exceeds the current-limit comparator threshold, the MOSFET driver (DRV) quickly terminates the on-cycle. In some cases, a short time-constant RC filter could be required to filter out the leading-edge spike on the sense waveform in addition to the internal blanking time. The amplitude and width of the leading edge spike depends on the gate capacitance, drain capacitance, and switching speed (MOSFET turn-on time).

## **Hiccup Operation**

The devices incorporate a hiccup mode to protect the external power components when there is an output short-circuit. If PGOOD is low (i.e., the output voltage is less than 85% of its set value) and there are 16 consecutive current-limit events, switching is stopped. There is then a waiting period of 44ms before the device tries to

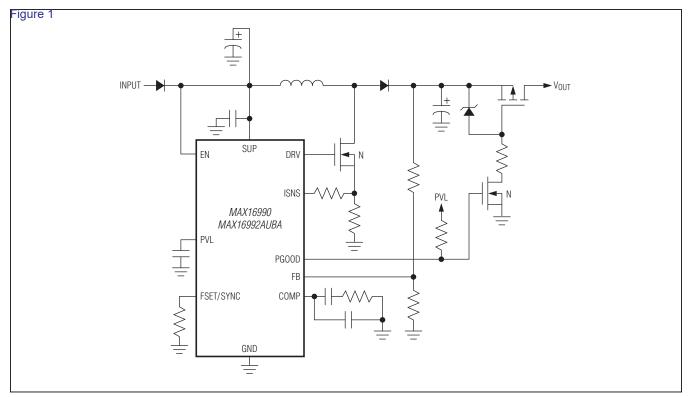

restart by initiating a soft-start. Note that a short-circuit on the output places considerable stress on all the power components even with hiccup mode, so that careful component selection is important if this condition is encountered. For more complete protection against output short-circuits, a series pMOS switch driven from PGOOD through a level-shifter can be employed (see Figure 1).

## **Applications Information**

## **Inductor Selection**

Using the following equation, calculate the minimum inductor value so that the converter remains in continuous mode operation at minimum output current (I<sub>OMIN</sub>):

$$L_{MIN} = (V_{IN}^2 \times D \times \eta)/(2 \times f_{SW} \times V_{OUT} \times I_{OMIN})$$

where:

$$D = (V_{OUT} + V_D - V_{IN})/(V_{OUT} + V_D - V_{DS})$$

and:

I<sub>OMIN</sub> is between 10% and 25% of I<sub>OUT</sub>

A higher value of  $I_{OMIN}$  reduces the required inductance, but it increases the peak and RMS currents in the switching MOSFET and inductor. Select  $I_{OMIN}$  between 10% to 25% of the full load current.  $V_D$  is the forward voltage drop of the external Schottky diode, D is the duty cycle, and  $V_{DS}$  is the voltage drop across the external switch. Select an inductor with low DC resistance and with a saturation current ( $I_{SAT}$ ) rating higher than the peak switch current limit of the converter.

## **Input and Output Capacitors**

The input current to a boost converter is almost continuous and the RMS ripple current at the input capacitor is low. Calculate the minimum input capacitor value and maximum ESR using the following equations:

$$C_{IN} = DI_L \times D/(4 \times f_{SW} \times DV_Q)$$

$ESR_{MAX} = DV_{ESR}/DI_L$

where DI<sub>I</sub> =  $((V_{IN} - V_{DS}) \times D)/(L \times f_{SW})$ .

$V_{DS}$  is the total voltage drop across the external MOSFET plus the voltage drop across the inductor ESR.  $DI_L$  is peak-to-peak inductor ripple current as calculated above.  $DV_Q$  is the portion of input ripple due to the capacitor discharge and  $DV_{ESR}$  is the contribution due to ESR of the capacitor. Assume the input capacitor ripple contribution due to ESR ( $DV_{ESR}$ ) and capacitor discharge ( $DV_Q$ ) are equal when using a combination of ceramic and aluminium capacitors. During the converter turn-on, a large current is drawn from the input source,

Figure 1. Application with Output Short-Circuit Protection

especially at high output-to-input differential. The devices have an internal soft-start, but a larger input capacitor than calculated above could be necessary to avoid chattering due to finite hysteresis during turn-on.

In a boost converter, the output capacitor supplies the load current when the main switch is on. The required output capacitance is high, especially at lower duty cycles. Also, the output capacitor ESR needs to be low enough to minimize the voltage drop due to ESR while supporting the load current. Use the following equations to calculate the output capacitor for a specified output ripple. All ripple values are peak-to-peak.

$$\begin{aligned} & \mathsf{ESR} = \mathsf{DV}_{\mathsf{ESR}} / \mathsf{I}_{\mathsf{OUT}} \\ & \mathsf{C}_{\mathsf{OUT}} = (\mathsf{I}_{\mathsf{OUT}} \times \mathsf{D}_{\mathsf{MAX}}) / (\mathsf{DV}_{\mathsf{Q}} \times \mathsf{f}_{\mathsf{SW}}) \end{aligned}$$

where  $I_{OUT}$  is the output current,  $DV_Q$  is the portion of the ripple due to the capacitor discharge, and  $DV_{ESR}$  is the ripple contribution due to the ESR of the capacitor.  $D_{MAX}$  is the maximum duty cycle (i.e., the duty cycle at the minimum input voltage). Use a combination of low-ESR

ceramic and high-value, low-cost aluminium capacitors for lower output ripple and noise.

# **Current-Sense Resistor Selection and Setting Slope Compensation**

Set the current-limit threshold 20% higher than the peak switch current at the rated output power and minimum input voltage. Use the following equation to calculate an initial value for  $R_{CS}$ :

$$R_{CS} = 0.2/\{1.2 \times [((V_{OUT} \times I_{OUT})/\eta)/V_{INMIN} + 0.5 \times ((V_{OUT} - V_{INMIN})/V_{OUT}) \times (V_{INMIN}/(f_{SW} \times L))]\}$$

where  $\eta$  is the estimated efficiency of the converter (use 0.85 as an initial value or consult the graph in the <u>Typical Operating Characteristics</u> section);  $V_{OUT}$  and  $I_{OUT}$  are the output voltage and current, respectively;  $V_{INMIN}$  is the minimum value of the input voltage;  $f_{SW}$  is the switching frequency; and L is the minimum value of the chosen inductor.

The devices use an internal ramp generator for slope compensation to stabilize the current loop when operating at duty cycles above 50%. The amount of slope

## 36V, 2.5MHz Automotive Boost/ SEPIC Controllers

compensation required depends on the down-slope of the inductor current when the main switch is off. The inductor down-slope in turn depends on the input to output voltage differential of the converter and the inductor value. Theoretically, the compensation slope should be equal to 50% of the inductor downslope; however, a little higher than 50% slope is advised. Use the following equation to calculate the required compensating slope (mc) for the boost converter:

$$mc = 0.5 \times (V_{OUT} - V_{IN})/L A/s$$

The internal ramp signal resets at the beginning of each cycle and slews at the rate of  $50\mu A$  x  $f_{SW}$ . Adjust the amount of slope compensation by choosing  $R_{SCOMP}$  to satisfy the following equation:

$$R_{SCOMP} = (mc \times R_{CS})/(50e-6 \times f_{SW})$$

In some applications, a filter could be needed between the current-sense resistor and the ISNS pin to augment the internal blanking time. Set the RC time constant just long enough to suppress the leading edge spike of the MOSFET current. For a given design, measure the leading spike at the lowest input and rated output load to determine the value of the RC filter which can be formed from the slope-compensation resistor and an added capacitor from ISNS to GND.

#### **MOSFET Selection**

The devices drive a wide variety of logic-level n-channel power MOSFETs. The best performance is achieved with low-threshold n-channel MOSFETs that specify on-resistance with a gate-source voltage ( $V_{GS}$ ) of 5V or less. When selecting the MOSFET, key parameters can include:

- 1) Total gate charge (Q<sub>q</sub>).

- 2) Reverse-transfer capacitance or charge (C<sub>RSS</sub>).

- 3) On-resistance (R<sub>DS(ON)</sub>).

- 4) Maximum drain-to-source voltage (VDS(MAX)).

- 5) Maximum gate frequencies threshold voltage (V<sub>TH(MAX)</sub>).

At high switching frequencies, dynamic characteristics (parameters 1 and 2 of the above list) that predict switching losses have more impact on efficiency than  $R_{DS(ON)}$ , which predicts DC losses. Qg includes all capacitances associated with charging the gate. The  $V_{DS(MAX)}$  of the selected MOSFET must be greater than the maximum output voltage setting plus a diode drop (or the maximum input voltage if greater) plus an additional margin to allow for spikes at the MOSFET drain due to the inductance in the rectifier diode and output capacitor path. In addition,  $Q_g$  determines the current needed to drive the gate at the selected operating frequency using the PVL linear regulator and therefore determines the power dissipation of the IC (see the  $\underline{Power\ Dissipation}$  section).

#### **Low-Voltage Operation**

The devices operate down to a voltage of 4.5V or less on their SUP pins. If the system input voltage is lower than this, the circuit can be operated from its own output as shown in the *Typical Application Circuit*. At very low input voltages, it is important to remember that input current will be high and the power components (inductor, MOSFET and diode) must be specified for this higher input current. In addition, the current limit of the devices must be set high enough so that the limit is not reached during the ontime of the MOSFET, which would result in output-power limitation and eventually, entering hiccup mode. Estimate the maximum input current using the following equation:

$$I_{INMAX} = ((V_{OUT} \times I_{OUT})/\eta)/V_{INMIN} + 0.5 \times ((V_{OUT} - V_{INMIN})/V_{OUT}) \times (V_{INMIN}/(f_{SW} \times L))$$

where  $I_{INMAX}$  is the maximum input current;  $V_{OUT}$  and  $I_{OUT}$  are the output voltage and current, respectively;  $\eta$  is the estimated efficiency (which is lower at low input voltages due to higher resistive losses);  $V_{INMIN}$  is the minimum value of the input voltage;  $f_{SW}$  is the switching frequency; and L is the minimum value of the chosen inductor.

#### **Boost Converter Compensation**

Refer to Application Note 5587: Selecting External Components and Compensation for Automotive Step-Up DC-DC Regulator with Preboost Reference Design.

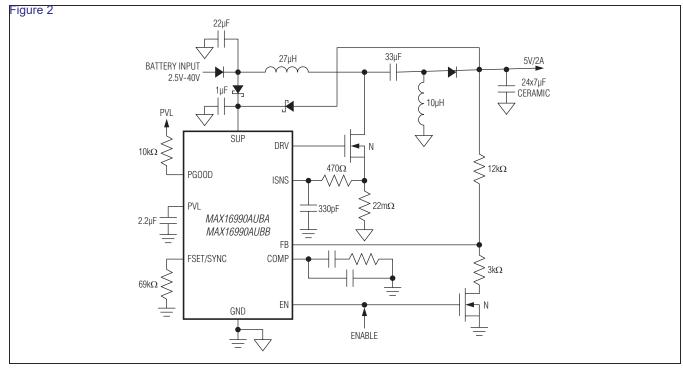

#### **SEPIC Operation**

For a reference example of using the devices in SEPIC mode, see Figure 2.

Figure 2. SEPIC Bootstrapped 400kHz Application with Low Operating Voltage

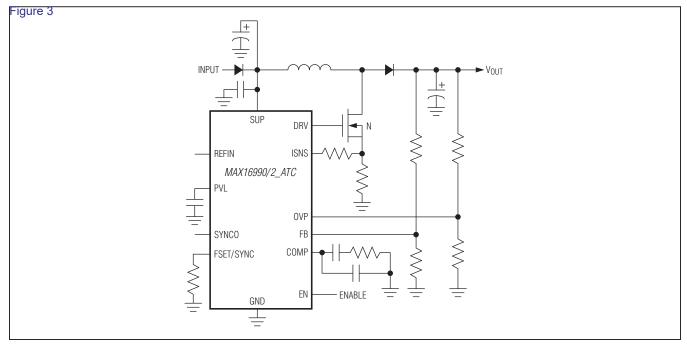

Figure 3. Application with Independent Output Overvoltage Protection

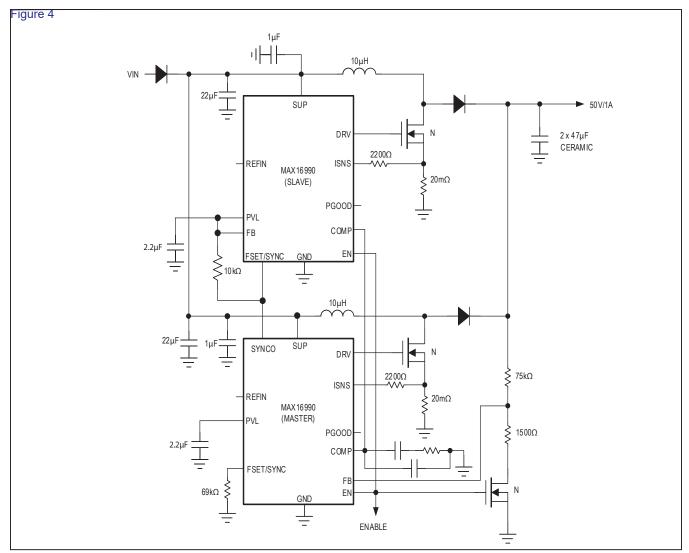

Figure 4. Two-Phase 400kHz Boost Application with Minimum Component Count

## **Overvoltage Protection**

The "C" and "D" variants of the devices include the overvoltage protection input. When the OVP pin goes above 110% of the FB regulation voltage, all switching is disabled. For an example application circuit, see <u>Figure 3</u>.

## **Multiphase Operation**

Two boost phases can be implemented with no extra components, using two ICs as shown in <a href="Figure 4">Figure 4</a>. In this circuit, the SYNCO output of the master device drives the SYNC input of the slave, forcing it to operate 180° out of phase. The FB pin of the slave device is connected to PVL, thus disabling its error amplifier. In this way, the error

amplifier of the master controls both devices by means of the COMP signal, and good current-sharing is attained between the two phases. When designing the PCB for a multiphase converter, it is important to protect the COMP trace in the layout from noisy signals by placing it on an inner layer and surrounding it with ground traces.

## **Using REFIN to Adjust the Output Voltage**

The REFIN pin can be used to directly adjust the reference voltage of the boost converter, thus altering the output voltage. When not used, REFIN should be connected to PVL. Because REFIN is a high-impedance pin, it is simple to drive it by means of an external digital-to-analog converter (DAC) or a filtered PWM signal.

## **Power Dissipation**

The power dissipation of the IC comes from two sources: the current consumption of the IC itself and the current required to drive the external MOSFET, of which the latter is usually dominant. The total power dissipation can be estimated using the following equation:

$P_{IC} = V_{SUP} \times I_{CC} + (V_{SUP} - 5) \times (Q_q \times f_{SW})$

where  $V_{SUP}$  is the voltage at the SUP pin of the IC,  $I_{CC}$  is the IC quiescent current consumption or typically 0.75mA (MAX16990) or 1.25mA (MAX16992),  $Q_g$  is the total gate charge of the chosen MOSFET at 5V, and  $f_{SW}$  is the switching frequency.  $P_{IC}$  reaches its maximum at maximum  $V_{SUP}$ .

## **Ordering Information**

| PART             | FREQUENCY<br>RANGE | OVP/<br>SYNCO | SPREAD<br>SPECTRUM | TEMP RANGE      | PIN-PACKAGE   |

|------------------|--------------------|---------------|--------------------|-----------------|---------------|

| MAX16990AUBA/V+  | 220kHz to 1MHz     | None          | Off                | -40°C to +125°C | 10 μMAX-EP*   |

| MAX16990AUBB/V+  | 220kHz to 1MHz     | None          | On                 | -40°C to +125°C | 10 μMAX-EP*   |

| MAX16990ATCC/V+  | 220kHz to 1MHz     | OVP           | Off                | -40°C to +125°C | 12 TQFN-EP*   |

| MAX16990ATCD/V+  | 220kHz to 1MHz     | OVP           | On                 | -40°C to +125°C | 12 TQFN-EP*   |

| MAX16990ATCD/VY+ | 220kHz to 1MHz     | OVP           | On                 | -40°C to +125°C | 12 SWTQFN-EP* |

| MAX16990ATCE/V+  | 220kHz to 1MHz     | SYNCO         | Off                | -40°C to +125°C | 12 TQFN-EP*   |

| MAX16990ATCF/V+  | 220kHz to 1MHz     | SYNCO         | On                 | -40°C to +125°C | 12 TQFN-EP*   |

| MAX16992AUBA/V+  | 1MHz to 2.5MHz     | None          | Off                | -40°C to +125°C | 10 μMAX-EP*   |

| MAX16992AUBB/V+  | 1MHz to 2.5MHz     | None          | On                 | -40°C to +125°C | 10 μMAX-EP*   |

| MAX16992ATCC/V+  | 1MHz to 2.5MHz     | OVP           | Off                | -40°C to +125°C | 12 TQFN-EP*   |

| MAX16992ATCD/V+  | 1MHz to 2.5MHz     | OVP           | On                 | -40°C to +125°C | 12 TQFN-EP*   |

| MAX16992ATCD/VY+ | 1MHz to 2.5MHz     | OVP           | On                 | -40°C to +125°C | 12 SWTQFN-EP* |

| MAX16992ATCE/V+  | 1MHz to 2.5MHz     | SYNCO         | Off                | -40°C to +125°C | 12 TQFN-EP*   |

| MAX16992ATCF/VY+ | 1MHz to 2.5MHz     | SYNCO         | On                 | -40°C to +125°C | 12 SWTQFN-EP* |

<sup>/</sup>V denotes an automotive qualified part.

## **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PKG<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN<br>NO. |

|-----------------|-------------|----------------|------------------------|

| 12 SWTQFN-EP    | T1233Y+4    | 21-100171      | 90-100060              |

| 12 TQFN-EP      | T1233+4     | 21-0136        | 90-0019                |

| 10 μMAX-EP      | U10E+3      | 21-0109        | 90-0148                |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>EP = Exposed pad.

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                         | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 3/13             | Initial release                                                                                                                                                                                                     | _                |

| 1                  | 4/13             | Added EP to µMAX package in Pin Descriptions                                                                                                                                                                        | 9–11             |

| 2                  | 4/13             | Corrected errors in TOCs 21 and 29                                                                                                                                                                                  | 7, 8             |

| 3                  | 7/13             | Removed future product asterisks from Ordering Information                                                                                                                                                          | 18               |

| 4                  | 2/15             | Update the Benefits and Features section                                                                                                                                                                            | 1                |

| 5                  | 7/15             | Corrected value in Figure 2, changing inductor value from 22μF to 22μH                                                                                                                                              | 16               |

| 6                  | 8/15             | Corrected part number in Typical Application Circuit                                                                                                                                                                | 1                |

| 7                  | 2/17             | Replaced toc18 in <u>Typical Operating Characteristics</u> , added MAX16992ATCF/VY+ in Ordering Information as a future product, and added SWTQFN-EP (package code T1233Y+4) in <u>Package Information</u> sections | 7, 18            |

| 8                  | 7/17             | Added Note 3 to SUP Operating Supply Range in the Electrical Characteristics table                                                                                                                                  | 2                |

| 9                  | 9/17             | Deleted Note 3 in and after the Electrical Characteristics table                                                                                                                                                    | 2, 4             |

| 10                 | 5/18             | Replaced Figure 4 and added MAX16990ATCD/VY+** to Ordering Information                                                                                                                                              | 17,18            |

| 11                 | 8/18             | Added MAX16992ATCD/VY+ to Ordering Information as a future product                                                                                                                                                  | 18               |

| 12                 | 10/18            | Removed future product status from MAX16990ATCD/VY+ in Ordering Information                                                                                                                                         | 18               |

| 13                 | 4/19             | Removed future product status from MAX16992ATCF/VY+ and future product-contact factory for availability note <u>Ordering Information</u> section                                                                    | 18               |

| 14                 | 6/19             | Updated Absolute Maximum Ratings and Package Thermal Characteristics                                                                                                                                                | 2                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.