# Synchronous Equipment Timing Source for 10G/40G/100G Synchronous Ethernet

# **Datasheet**

#### HIGHLIGHTS

- Synchronous Equipment Timing Source (SETS) for Synchronous Ethernet (SyncE) per ITU-T G.8264

- DPLL1 generates ITU-T G.8262 compliant SyncE clocks, Telcordia GR-1244-CORE/GR-253-CORE, and ITU-T G.813 compliant SONET/ SDH clocks

- DPLL2 performs rate conversions for synchronization interfaces or for other general purpose timing applications

- APLL3 is Voltage Controlled Crystal Oscillator (VCXO) based and generates clocks with jitter <0.3 ps RMS (10 kHz to 20 MHz) for: 10GBASE-R, 10GBASE-W, 40GBASE-R and 100GBASE-R

- APLL1 and APLL2 generate clocks with jitter < 1 ps RMS (12 kHz to 20 MHz) for: 1000BASE-T and 1000BASE-X

- Fractional-N input dividers support a wide range of reference frequencies

- Locks to 1 Pulse Per Second (PPS) references

- DPLLs, APLL1 and APLL2 can be configured from an external **EEPROM** after reset

### **FEATURES**

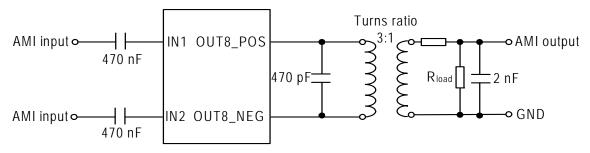

- Composite clock inputs (IN1 and IN2) accept 64 kHz synchronization interface signals per ITU-T G.703

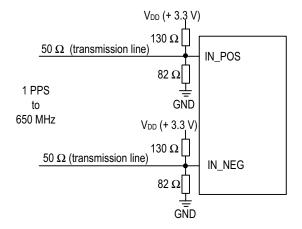

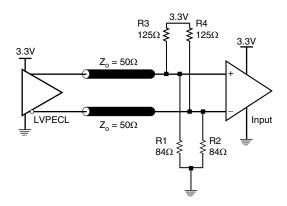

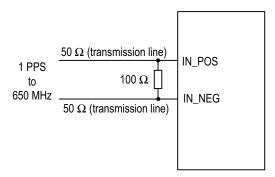

- Differential reference inputs (IN3 to IN8) accept clock frequencies between 1 PPS and 650 MHz

- Single ended inputs (IN9 to IN14) accept reference clock frequencies between 1 PPS and 162.5 MHz

- Loss of Signal (LOS) pins (LOS0 to LOS3) can be assigned to any clock reference input

- Reference monitors qualify/disqualify references depending on activity, frequency and LOS pins

- Automatic reference selection state machines select the active reference for each DPLL based on the reference monitors, priority tables, revertive and non-revertive settings and other programmable settings

- Fractional-N input dividers enable the DPLLs to lock to a wide range of reference clock frequencies including: 10/100/1000 Ethernet, 10G/ 40G/100G Ethernet, OTN, SONET/SDH, PDH, TDM, GSM, CPRI, and GNSS frequencies

- Any reference inputs (IN3 to IN14) can be designated as external sync pulse inputs (1 PPS, 2 kHz, 4 kHz or 8 kHz) associated with a selectable reference clock input

- FRSYNC\_8K\_1PPS and MFRSYNC\_2K\_1PPS output sync pulses that are aligned with the selected external input sync pulse input and frequency locked to the associated reference clock input

- DPLL1 can be configured with bandwidths between 0.09 mHz and 567 Hz

- DPLL1 locks to input references with frequencies between 1 PPS and

- DPLL2 locks to input references with frequencies between 8 kHz and 650 MHz

- DPLL1 complies with ITU-T G.8262 for Synchronous Ethernet Equipment Clock (EEC), and G.813 for Synchronous Equipment Clock

- (SEC); and Telcordia GR-253-CORE/ GR-1244-CORE for Stratum 3 and SONET Minimum Clock (SMC)

- DPLL1 generates clocks with PDH, TDM, GSM, CPRI/OBSAI, 10/100/ 1000 Ethernet and GNSS frequencies; these clocks are directly available on OUT1

- DPLL2 generates N x 8 kHz clocks up to 100 MHz that are output on OUT9 and OUT10

- APLL1, APLL2 and APLL3 are connected to DPLL1

- APLL1 and APLL2 generate 10/100/1000 Ethernet, 10G Ethernet, or SONET/SDH frequencies

- APLL3 generates 10G/40G/100G Ethernet, WAN-PHY, and LAN-PHY frequencies

- Any of eight common TCXO/OCXO frequencies can be used for the System Clock: 10 MHz, 12.8 MHz, 13 MHz, 19.44 MHz, 20 MHz, 24.576 MHz, 25 MHz, or 30.72 MHz

- The I2C slave interface can be used by a host processor to access the control and status registers

- The I2C master interface can automatically load a device configuration from an external EEPROM after reset; APLL3 must be configured via the I2C slave interface

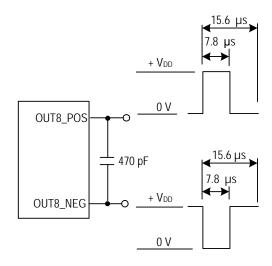

- DPLLs can be connected to an internal composite clock generator that outputs its 64 kHz synchronization signal on OUT8

- Differential outputs OUT3 to OUT6 output clocks with frequencies between 1 PPS and 650 MHz

- Differential outputs OUT11 and OUT12 output clocks with frequencies up to 650 MHz

- Single ended outputs OUT1, OUT2 and OUT7 output clocks with frequencies between 1 PPS and 125 MHz

- Single ended outputs OUT9 and OUT10 output clocks N\*8 kHz multiples up to 100 MHz

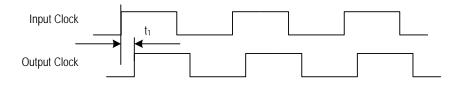

- DPLL1 supports independent programmable delays for each of IN3 to IN14; the delay for each input is programmable in steps of 0.61 ns with a range of ~±78 ns

- The input to output phase delay of DPLL1 is programmable in steps of 0.0745 ps with a total range of  $\pm 20 \mu s$

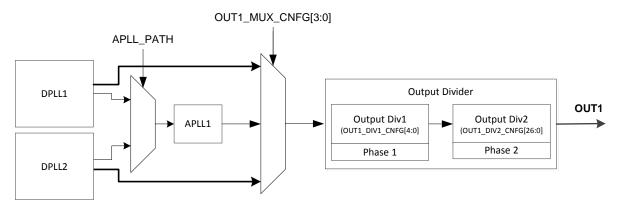

- The clock phase of each of the output dividers for OUT1 (from APLL1) to OUT7 is individually programmable in steps of ~200 ps with a total range of +/-180°

- 1149.1 JTAG Boundary Scan

- 144-pin CABGA green package

#### **APPLICATIONS**

- Access routers, edge routers, core routers

- Carrier Ethernet switches

- Multi-service access platforms

- PON OLT

- LTE eNodeB

- ITU-T G.8264 Synchronous Equipment Timing Source (SETS)

- ITU-T G.8262 Synchronous Ethernet Equipment Clock (EEC)

- ITU-T G.813 Synchronous Equipment Clock (SEC)

- Telcordia GR-253-CORE/GR1244-CORE Stratum 3 Clock (S3) and SONET Minimum Clock (SMC)

### **DESCRIPTION**

The 82P33731 Synchronous Equipment Timing Source (SETS) for 10G Synchronous Ethernet (SyncE) provides tools to manage timing references, clock generation and timing paths for SyncE based clocks, per ITU-T G.8264 and ITU-T G.8262. 82P33731 meets the requirements of ITU-T G.8262 for synchronous Ethernet Equipment Clocks (EECs) and ITU-T G.813 for Synchronous Equipment Clocks (SEC). The device outputs low-jitter clocks that can directly synchronize 100GBASE-R, 40GBASE-R, 10GBASE-R and 10GBASE-W and lower-rate Ethernet interfaces; as well as CPRI/OBSAI, SONET/SDH and PDH interfaces.

The 82P33731 accepts six differential reference inputs and six single ended reference inputs that can operate at common GNSS, Ethernet, SONET/SDH and PDH frequencies that range from 1 Pulse Per Second (PPS) to 650 MHz. The device also provides two Alternate Mark Inversion (AMI) inputs for Composite Clock (CC) signals bearing 64 kHz, 8 kHz and 0.4 kHz synchronization information. The references are continually monitored for loss of signal and for frequency offset per user programmed thresholds. All of the references are available to both Digital PLLs (DPLLs). The active reference for each DPLL is determined by forced selection or by automatic selection based on user programmed priorities and locking allowances and based on the reference monitors and LOS inputs.

The 82P33731 can accept a clock reference and an associated phase locked sync signal as a pair. DPLL1 can lock to the clock reference and align the frame sync and multi-frame sync outputs with the paired sync input. The device allows any of the differential or single ended reference inputs to be configured as sync inputs that can be associated with any of the other differential or single ended reference inputs. The input sync signals can have a frequency of 1 PPS, 2 kHz, 4 kHz or 8 kHz. This feature enables DPLL1 to phase align its frame sync and multi-frame sync outputs with a sync input without the need use a low bandwidth setting to lock directly to the sync input.

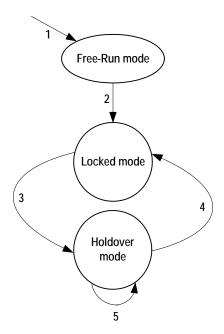

The DPLLs support three primary operating modes: Free-Run, Locked and Holdover. In Free-Run mode the DPLLs synthesize clocks based on the system clock alone. In Locked mode the DPLLs filter reference clock jitter with the selected bandwidth. In Locked mode, the long-term output frequency accuracy is the same as the long term frequency accuracy of the selected input reference. In Holdover mode, the DPLL uses frequency data acquired while in Locked mode to generate accurate frequencies when input references are not available.

The 82P33731 requires a system clock for its reference monitors and other digital circuitry. The frequency accuracy of the system clock determines the frequency accuracy of the DPLLs in Free-Run mode. The frequency stability of the system clock determines the frequency stability of the DPLLs in Free-Run mode and in Holdover mode; and it affects the wander generation of the DPLLs in Locked mode.

When used with a suitable system clock, DPLL1 meets the frequency accuracy, pull-in, hold-in, pullout, noise generation, noise tolerance, transient response, and holdover performance requirements of the following applications: ITU-T G.8262/G.813 EEC/SEC options 1 and 2, Telcordia GR-1244 Stratum 3 (S3), Telcordia GR-253-CORE S3 and SONET Minimum Clock (SMC).

DPLL1 can be configured with a range of selectable filtering bandwidths from 0.09 mHz to 567 Hz. The 17 mHz bandwidth can be used to lock the DPLL directly to a 1 PPS reference. The 92 mHz bandwidth can be used for G.8262/G.813 Option 2, or Telcordia GR-253-CORE S3, or SMC applications. The bandwidths in the range 1.1 Hz to 8.9 Hz can be used for G.8262/G.813 Option 1 applications. The bandwidth of 1.1 Hz or 2.2 Hz can be used for Telcordia GR-1244-CORE S3 applications. Bandwidths above 10 Hz can be used in jitter attenuation and rate conversion applications.

DPLL2 is a wideband (BW > 25Hz) frequency translator that can be used, for example, to convert a recovered line clock to a 1.544 MHz or 2.048 MHz synchronization interface clock.

For SETS applications per ITU-T G.8264, DPLL1 is configured as an EEC/SEC to output clocks for the T0 reference point and DPLL2 is used to output clocks for the T4 reference point.

Clocks generated by DPLL1 can be passed through APLL1 or APLL2 which are LC based jitter attenuating Analog PLLs (APLLs). The output clocks generated by APLL1 and APLL2 are suitable for serial GbE and lower rate interfaces.

Clocks generated by DPLL1 can be passed through APLL3 which is a voltage controlled crystal oscillator (VCXO) based jitter attenuating APLL. APLL3 can be provisioned with one or two selectable crystal resonators to support up to two base frequencies. The output clocks generated by APLL3 are suitable for multi-lane 100GBASE-R, 40GBASE-R and lower rate interfaces.

The device provides an AMI output for a CC signal bearing 64 kHz, 8 kHz and 0.4 kHz synchronization information. The CC output can be connected to either DPLL1 or DPLL3.

All 82P33731 control and status registers are accessed through an I2C slave microprocessor interface. For configuring the DPLLs, APLL1 and APLL2, the I2C master interface can automatically load a configuration from an external EEPROM after reset. APLL3 must be configured via the I2C slave interface.

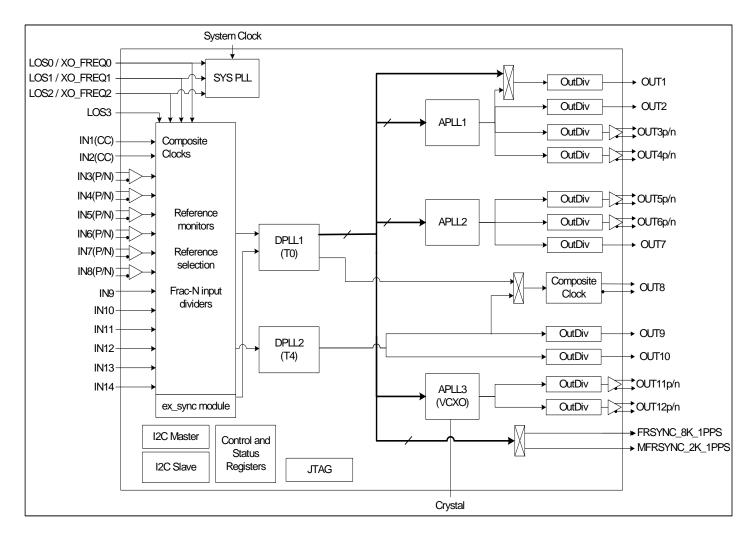

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

# **CONTENTS**

| HI | GHLIG  | HTS  |           |                        |                                                |    | 1 |

|----|--------|------|-----------|------------------------|------------------------------------------------|----|---|

| FE | EATURE | ES   |           |                        |                                                |    | 1 |

|    |        |      |           |                        |                                                |    |   |

|    |        |      |           |                        |                                                |    |   |

|    |        |      |           |                        | VI                                             |    |   |

|    |        |      |           |                        |                                                |    |   |

|    |        |      |           |                        |                                                |    |   |

|    |        |      |           |                        |                                                |    |   |

| 2  | PIN DI | ESCI | RIPTIO    |                        |                                                | (  | 6 |

|    | 2.1 R  |      |           |                        | UNUSED INPUT AND OUTPUT PINS                   |    |   |

|    | 2.     |      |           |                        |                                                |    |   |

|    |        |      |           |                        |                                                |    |   |

|    |        |      |           |                        |                                                |    |   |

|    |        |      |           |                        |                                                |    |   |

| 3  |        |      |           |                        | N                                              |    |   |

|    |        |      |           |                        | T (SYNCE), SONET, AND SDH SYSTEM ARCHITECTURES |    |   |

|    | 3.2 H  |      |           |                        | DESCRIPTION                                    |    |   |

|    |        |      |           |                        |                                                |    |   |

|    | 3.     | .2.2 |           |                        |                                                |    |   |

|    |        |      | 3.2.2.1   |                        | erating Mode                                   |    |   |

|    |        |      |           |                        | Free-Run Mode                                  |    |   |

|    |        |      |           | 3.2.2.1.2              | Pre-Locked Mode                                |    |   |

|    |        |      |           | 3.2.2.1.3              | Locked Mode                                    |    |   |

|    |        |      |           | 3.2.2.1.4              | Pre-Locked2 Mode                               |    |   |

|    |        |      |           | 3.2.2.1.5<br>3.2.2.1.6 | DCO Control Modes                              |    |   |

|    |        |      |           | 3.2.2.1.0              | Holdover Mode                                  |    |   |

|    |        |      |           | 3.2.2.1.7              | Hitless Reference Switching                    |    |   |

|    |        |      |           | 3.2.2.1.9              | Phase Slope Limit                              |    |   |

|    |        |      |           |                        | Frequency Offset Limit                         |    |   |

|    |        |      | 3.2.2.2   |                        | erating Mode                                   |    |   |

|    |        |      |           |                        | Free-Run Mode                                  |    |   |

|    |        |      |           | 3.2.2.2.2              | Locked Mode                                    |    |   |

|    |        |      |           | 3.2.2.2.3              | Holdover Mode                                  |    |   |

|    |        |      |           | 3.2.2.2.4              | Frequency Offset Limit                         | 21 | 0 |

|    | 3.     | .2.3 | Input Clo | cks and fran           | ne sync                                        | 21 | 0 |

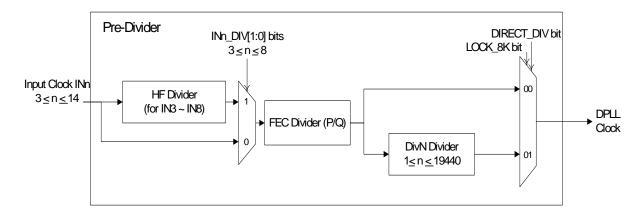

|    |        |      | 3.2.3.1   | Input Clock            | Pre-divider                                    | 2  | 0 |

|    |        |      | 3.2.3.2   | Input Clock            | Quality Monitoring                             |    |   |

|    |        |      |           | 3.2.3.2.1              | Loss of Signal (LOS) Monitoring                |    |   |

|    |        |      |           | 3.2.3.2.2              | Activity Monitoring                            |    |   |

|    |        |      |           | 3.2.3.2.3              | Frequency Monitoring                           |    |   |

|    |        |      | 3.2.3.3   | •                      | Selection                                      |    |   |

|    |        |      |           | 3.2.3.3.1              | Forced Selection                               |    |   |

|    |        |      |           | 3.2.3.3.2              | Automatic Selection                            |    |   |

|    |        |      |           |                        | 3.2.3.3.2.1Input Clock Validation              |    |   |

|    |        |      |           | 2 2 2 2 2              | 3                                              |    |   |

|    |        |      |           | 3.2.3.3.3<br>3.2.3.3.4 | Selected / Qualified Input Clocks Indication   |    |   |

|    | 2      | .2.4 | DPII I o  |                        | SS                                             |    |   |

|    | ٥.     | .∠.→ | 3.2.4.1   | 0                      |                                                |    |   |

|    |        |      | 3.2.4.2   |                        | Loss                                           |    |   |

|    |        |      | –         |                        |                                                |    |   |

|     |      |        | 3.2.4.3   | Hard Limit Exceeding                         | . 25 |

|-----|------|--------|-----------|----------------------------------------------|------|

|     |      |        | 3.2.4.4   | Locking Status                               | . 25 |

|     |      |        | 3.2.4.5   | Phase Lock Alarm                             | . 26 |

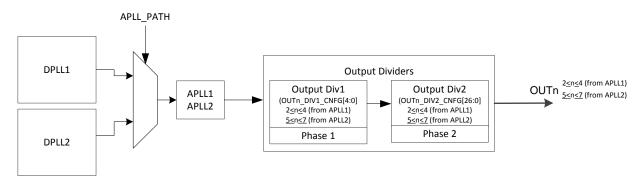

|     |      | 3.2.5  |           | d APLL2                                      |      |

|     |      |        |           |                                              |      |

|     |      |        |           | External Crystals                            |      |

|     |      | 3.2.7  |           | ocks & Frame Sync Signals                    |      |

|     |      | 0.2.7  |           | Output Clocks                                |      |

|     |      |        |           | Frame Sync Signals                           |      |

|     |      | 3.2.8  |           | output Phase control                         |      |

|     |      | 3.2.0  |           | DPLL1 and DPL2 Phase offset control          |      |

|     |      |        |           |                                              |      |

|     |      |        |           | Input Phase control                          |      |

| 4   |      | VED 6  |           | Output Phase control                         |      |

|     |      |        |           | FILTERING TECHNIQUES                         |      |

| 5   | MIC  | ROPR   | OCESSO    | OR INTERFACE                                 | . 34 |

|     | 5.1  | I2C SL | AVE MOD   | E                                            | 34   |

|     |      |        |           | e Address                                    |      |

|     |      |        |           | iming                                        |      |

|     |      |        |           | d Transactions                               |      |

|     | 5.2  |        |           | DE                                           |      |

|     | J.Z  |        |           | up Initialization Mode                       |      |

|     |      |        |           |                                              |      |

| ,   | IΤΛ  |        |           | memory map notes                             |      |

|     |      |        |           |                                              |      |

| 7   | THE  |        |           | EMENT                                        |      |

|     | 7.1  | JUNCT  | TON TEMP  | PERATURE                                     | 39   |

|     | 7.2  | THERN  | /AL RELE  | ASE PATH                                     | 39   |

| 8   | FLF  | CTRIC  | CAL SPE   | CIFICATIONS                                  | . 40 |

|     |      |        |           | IMUM RATING                                  |      |

|     |      |        |           | O OPERATION CONDITIONS                       |      |

|     |      |        |           | ONS                                          |      |

|     | 0.3  |        |           | / Output Port                                |      |

|     |      | 8.3.1  |           |                                              |      |

|     |      |        |           | Structure                                    |      |

|     |      |        |           | I/O Level                                    |      |

|     |      | 0.00   |           | Over-Voltage Protection                      |      |

|     |      |        |           | put / Output Port                            |      |

|     |      | 8.3.3  |           | LVDS Input / Output Port                     |      |

|     |      |        |           | PECL Input Port                              |      |

|     |      |        | 8.3.3.2   | LVPECL Output Port                           |      |

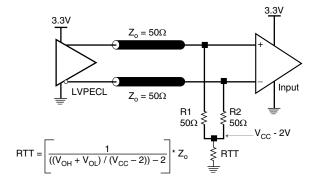

|     |      |        |           | 8.3.3.2.1 LVPECL Termination for 3.3 V       |      |

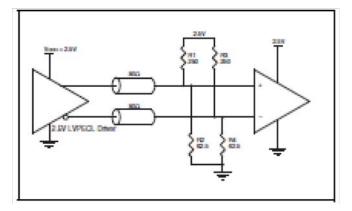

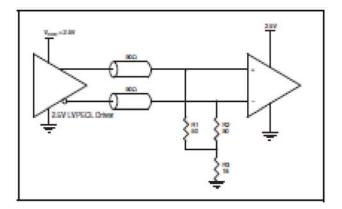

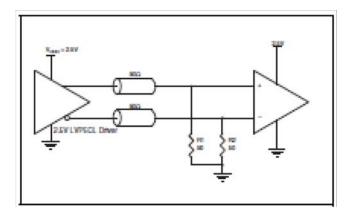

|     |      |        |           | 8.3.3.2.2 LVPECL Termination for 2.5 V       |      |

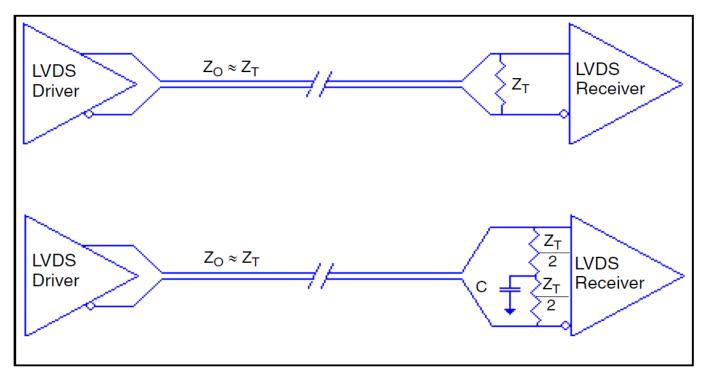

|     |      | 8.3.4  | LVDS Inp  | ut / Output Port                             | . 46 |

|     |      |        | 8.3.4.1   | LVDS Input Port                              | . 46 |

|     |      |        | 8.3.4.2   | LVDS Output Port                             | . 47 |

|     |      | 8.3.5  | Output CI | ock Duty Cycle                               | . 48 |

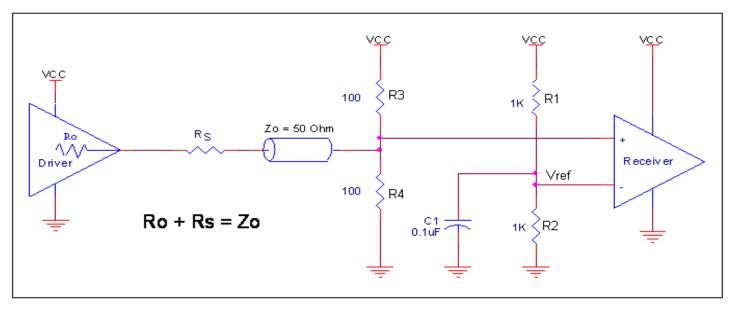

|     |      |        |           | e Differential Input for Single-Ended Levels |      |

|     | 8.4  |        | •         | MANCE                                        |      |

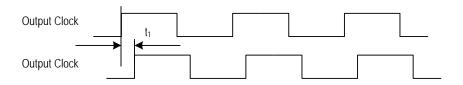

|     |      |        |           | CLOCK TIMING                                 |      |

|     | 8.6  |        |           | UT CLOCK TIMING                              |      |

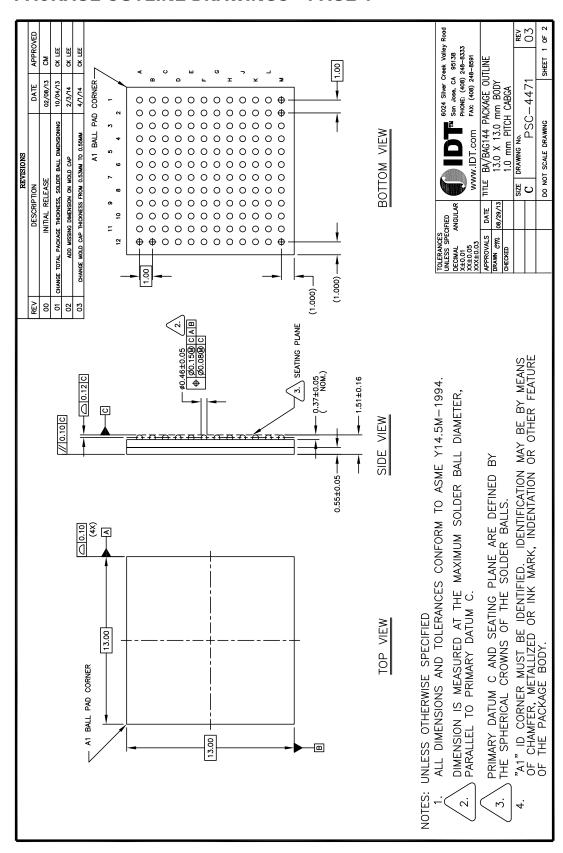

|     |      |        |           | DRAWINGS – PAGE 1                            |      |

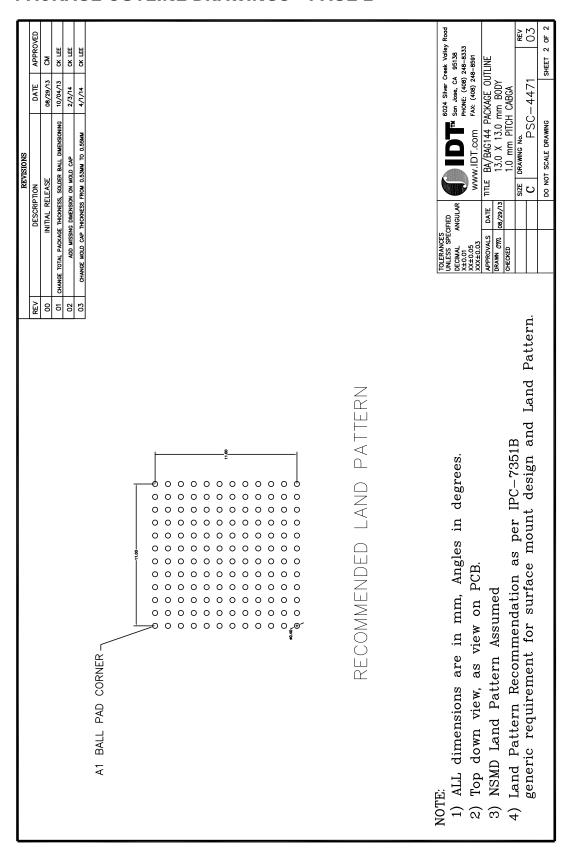

|     |      |        |           | DRAWINGS - PAGE 2                            |      |

|     |      |        |           |                                              |      |

|     |      |        |           | .TION                                        |      |

| RE' | VISI | ON HIS | STORY .   |                                              | 64   |

# 1 PIN ASSIGNMENT

|   | 1                 | 2                 | 3        | 4        | 5        | 6         | 7     | 8         | 9          | 10        | 11                     | 12                  |   |

|---|-------------------|-------------------|----------|----------|----------|-----------|-------|-----------|------------|-----------|------------------------|---------------------|---|

| Α | OUT5_POS          | OUT5_NEG          | OUT6_POS | OUT6_NEG | VDDAO    | OUT12_POS | VDDAO | OUT11_POS | CAP2       | XTAL2_IN  | SONET/SDH/LO<br>S3     | XTAL1_IN            | А |

| В | VSSAO             | VDDAO             | VDDAO    | VSSAO    | VSSAO    | OUT12_NEG | VSSAO | OUT11_NEG | VSSA       | XTAL2_OUT | MPU_MODE1/I<br>2CM_SCL | XTAL1_OUT           | В |

| С | VDDA              | VSSA              | VSS      | OUT7     | I2C_SDA  | VDDA      | VDDA  | IC        | CAP1       | IC        | MPU_MODE0/I<br>2CM_SDA | MFRSYNC_2<br>K_1PPS | С |

| D | VSSA              | VDDA              | VSSCOM   | VSSD     | VDDD     | VSSA      | VSSA  | CAP3      | I2C_AD2    | I2C_SCL   | OUT10                  | OUT9                | D |

| E | OSCI              | VSSA              | IC       | VDDDO    | I2C_AD1  | VDDD0     | VSSDO | VSSA      | DPLL2_LOCK | IN14      | IN13                   | FRSYNC_8K_<br>1PPS  | E |

| F | TMS               | VDDA              | VSSA     | VSSDO    | VSS      | VSSD      | VDDD  | VSSA      | VDDA       | IN12      | IN8_NEG                | IN8_POS             | F |

| G | тск               | VDDA              | IC       | VSS      | VSS      | VSS       | IC    | VSS       | IC         | IN11      | IN7_NEG                | IN7_POS             | G |

| Н | XO_FREQ0/<br>LOS0 | VDDA              | VSSA     | VSS      | vss      | vss       | VSS   | VSS       | DPLL1_LOCK | IN10      | VSSD                   | VDDD_1_8            | Н |

| J | XO_FREQ1/<br>LOS1 | XO_FREQ2/<br>LOS2 | VSS      | VSS      | VSS      | VSS       | VSS   | VSS       | INT_REQ    | IN9       | IN6_NEG                | IN6_POS             | J |

| K | VDDA              | VDDA              | TRSTB    | VSSAO    | OUT2     | RSTB      | VSSDO | MS_SL     | IN2        | IN1       | IN5_NEG                | IN5_POS             | К |

| L | VSSA              | VSSA              | TDI      | VDDAO    | TDO      | IC        | VDDDO | OUT1      | VSSD       | VDDD_1_8  | IN4_NEG                | IN4_POS             | L |

| М | OUT4_POS          | OUT4_NEG          | VSSAO    | VDDAO    | OUT3_POS | OUT3_NEG  | VSSDO | VDDDO     | OUT8_POS   | OUT8_NEG  | IN3_NEG                | IN3_POS             | М |

|   | 1                 | 2                 | 3        | 4        | 5        | 6         | 7     | 8         | 9          | 10        | 11                     | 12                  |   |

Figure 1. Pin Assignment (Top View)

# 2 PIN DESCRIPTION

Table 1: Pin Description

| Pin No.        | Name                                                        | I/O            | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-------------------------------------------------------------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                                                             |                |               | Global Control Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| E1             | OSCI                                                        | I              | CMOS          | OSCI: Crystal Oscillator System Clock A clock provided by a crystal oscillator is input on this pin. It is the system clock for the device. The oscillator frequency is selected via pins XO_FREQ0 ~ XO_FREQ2                                                                                                                                                                                                                                                                                    |

| K8             | MS/SL                                                       | l<br>pull-up   | CMOS          | MS/SL: Master / Slave Selection This pin, together with the MS_SL_CTRL bit, controls whether the device is configured as the Master or as the Slave. The signal level on this pin is reflected by the MASTER_SLAVE bit. MS_SL = 0: Slave MS_SL = 1: Master (default with internal pull-up)                                                                                                                                                                                                       |

| A11            | SONET/SDH/<br>LOS3                                          | l<br>pull-down | CMOS          | SONET/SDH: SONET / SDH Frequency Selection During reset, this pin determines the default value of the IN_SONET_SDH bit (b2, 09H): High: The default value of the IN_SONET_SDH bit is '1' (SONET); Low: The default value of the IN_SONET_SDH bit is '0' (SDH). After reset, this pin takes on the operation of LOS3 LOS3- This pin is used to disqualify input clocks. See input clocks section for more details.                                                                                |

| К6             | RSTB                                                        | I<br>pull-up   | CMOS          | RSTB: Reset Refer to section 2.2 reset operation for detail.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| H1<br>J1<br>J2 | XO_FREQ0/<br>LOS0<br>XO_FREQ1/<br>LOS1<br>XO_FREQ2/<br>LOS2 | l<br>pull-down | CMOS          | XO_FREQ0 - XO_FREQ2: These pins set the oscillator frequency.         XO_FREQ[2:0] Oscillator Frequency (MHz)         000       10.000         001       12.800         010       13.000         011       19.440         100       20.000         101       24.576         110       25.000         111       30.720         LOS0 ~ LOS2 - These pins are used to disqualify input clocks. See input clocks section for more details. After reset, this pin takes on the operation of LOS0-LOS2 |

|                |                                                             | ln .           | put Clock and | Frame Synchronization Input Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

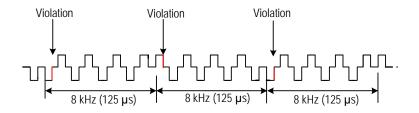

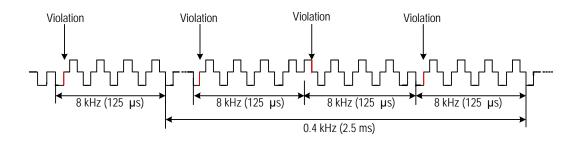

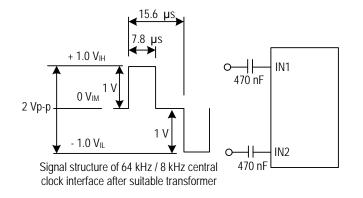

| K10            | IN1                                                         | I              | AMI           | IN1: Input Clock 1 A 64 kHz + 8 kHz or 64 kHz + 8 kHz + 0.4 kHz composite clock is input on this pin. AMI input has internal 1k ohm to 1.5V termination.                                                                                                                                                                                                                                                                                                                                         |

| К9             | IN2                                                         | I              | AMI           | IN2: Input Clock 2 A 64 kHz + 8 kHz or 64 kHz + 8 kHz + 0.4 kHz composite clock is input on this pin. AMI input has internal 1k ohm to 1.5V termination.                                                                                                                                                                                                                                                                                                                                         |

| M12<br>M11     | IN3_POS<br>IN3_NEG                                          | I              | PECL/LVDS     | IN3_POS / IN3_NEG: Positive / Negative Input Clock 3 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                                                                                                                                                                                                                                                         |

| L12<br>L11     | IN4_POS<br>IN4_NEG                                          | I              | PECL/LVDS     | IN4_POS / IN4_NEG: Positive / Negative Input Clock 4 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                                                                                                                                                                                                                                                         |

| K12<br>K11     | IN5_POS<br>IN5_NEG                                          | I              | PECL/LVDS     | IN5_POS / IN5_NEG: Positive / Negative Input Clock 5 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                                                                                                                                                                                                                                                         |

| J12<br>J11     | IN6_POS<br>IN6_NEG                                          | I              | PECL/LVDS     | IN6_POS / IN6_NEG: Positive / Negative Input Clock 6 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                                                                                                                                                                                                                                                         |

| G12<br>G11     | IN7_POS<br>IN7_NEG                                          | I              | PECL/LVDS     | IN7_POS / IN7_NEG: Positive / Negative Input Clock 7 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                                                                                                                                                                                                                                                         |

Table 1: Pin Description (Continued)

| Pin No.    | Name                   | I/O            | Туре      | Description                                                                                                                                                                                                              |

|------------|------------------------|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F12<br>F11 | IN8_POS<br>IN8_NEG     | I              | PECL/LVDS | IN8_POS / IN8_NEG: Positive / Negative Input Clock 8 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin. |

| J10        | IN9                    | l<br>pull-down | CMOS      | IN9: Input Clock 9 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                   |

| H10        | IN10                   | l<br>pull-down | CMOS      | IN10: Input Clock 10 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                 |

| G10        | IN11                   | l<br>pull-down | CMOS      | IN11: Input Clock 11 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                 |

| F10        | IN12                   | l<br>pull-down | CMOS      | IN12: Input Clock 12 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                 |

| E11        | IN13                   | l<br>pull-down | CMOS      | IN13: Input Clock 13 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                 |

| E10        | IN14                   | l<br>pull-down | CMOS      | IN14: Input Clock 14 A reference clock is input on this pin. This pin can also be used as a sync input, and in this case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.                                 |

|            | •                      | •              | Output F  | rame Synchronization Signal                                                                                                                                                                                              |

| E12        | FRSYNC<br>_8K_1PPS     | 0              | CMOS      | FRSYNC_8K_1PPS: 8 kHz Frame Sync Output An 8 kHz signal or a 1PPS sync signal is output on this pin.                                                                                                                     |

| C12        | MFRSYNC<br>_2K_1PPS    | 0              | CMOS      | MFRSYNC_2K_1PPS: 2 kHz Multiframe Sync Output A 2 kHz signal or a 1PPS sync signal is output on this pin.                                                                                                                |

|            |                        | •              |           | Output Clock                                                                                                                                                                                                             |

| L8<br>K5   | OUT1<br>OUT2           | 0              | CMOS      | OUT1 ~ OUT2: Output Clock 1 ~ 2                                                                                                                                                                                          |

| M5<br>M6   | OUT3_POS<br>OUT3_NEG   | 0              | PECL/LVDS | OUT3_POS / OUT3_NEG: Positive / Negative Output Clock 3 This output is set to LVDS by default.                                                                                                                           |

| M1<br>M2   | OUT4_POS<br>OUT4_NEG   | 0              | PECL/LVDS | OUT4_POS / OUT4_NEG: Positive / Negative Output Clock 4 This output is set to LVDS by default.                                                                                                                           |

| A1<br>A2   | OUT5_POS<br>OUT5_NEG   | 0              | PECL/LVDS | OUT5_POS / OUT5_NEG: Positive / Negative Output Clock 5 This output is set to LVDS by default.                                                                                                                           |

| A3<br>A4   | OUT6_POS<br>OUT6_NEG   | 0              | PECL/LVDS | OUT6_POS / OUT6_NEG: Positive / Negative Output Clock 6 This output is set to LVDS by default.                                                                                                                           |

| C4         | OUT7                   | 0              | CMOS      | OUT7: Output Clock 7                                                                                                                                                                                                     |

| M9<br>M10  | OUT8_POS<br>OUT8_NEG   | 0              | AMI       | OUT8_POS / OUT8_NEG: Positive / Negative Output Composite Clock A 64 kHz + 8 kHz or 64 kHz + 8 kHz + 0.4 kHz composite clock is differentially output on this pair of pins.                                              |

| D12        | OUT9                   | 0              | CMOS      | OUT9: Output Clock 9                                                                                                                                                                                                     |

| D11        | OUT10                  | 0              | CMOS      | OUT10: Output Clock 10                                                                                                                                                                                                   |

| A8<br>B8   | OUT11_POS<br>OUT11_NEG | 0              | PECL/LVDS | OUT11_POS / OUT11_NEG: Positive / Negative Output Clock 11                                                                                                                                                               |

| A6<br>B6   | OUT12_POS<br>OUT12_NEG | 0              | PECL/LVDS | OUT12_POS / OUT12_NEG: Positive / Negative Output Clock 12                                                                                                                                                               |

|            | •                      |                |           | Miscellaneous                                                                                                                                                                                                            |

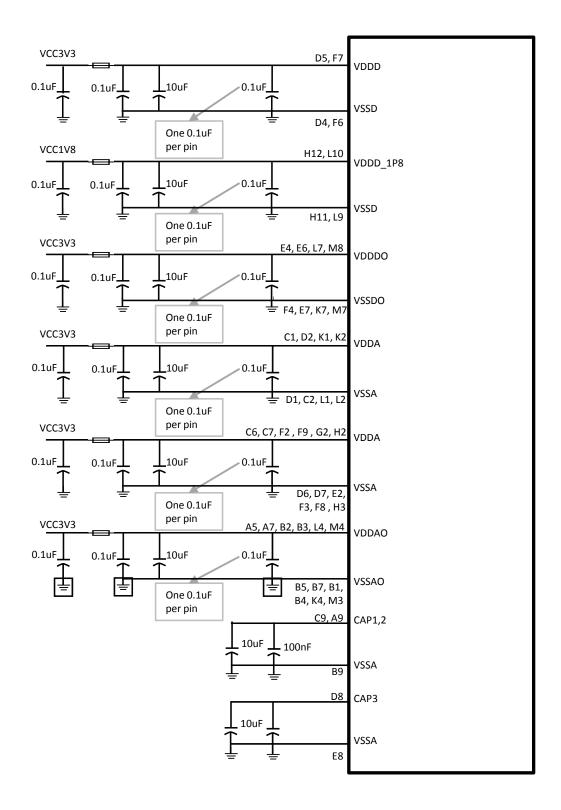

| C9, A9, D8 | CAP1, CAP2,<br>CAP3    |                |           | CAP1, CAP2 and CAP3: Analog Power Filter Capacitor connection 1 to 3. These capacitors are be part of the power filtering.                                                                                               |

Table 1: Pin Description (Continued)

| Pin No.    | Name                                             | I/O            | Туре                | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|--------------------------------------------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A12        | XTAL1_IN                                         | I              | Analog              | Crystal oscillator 1 input.  Determines first of two frequency families (Sonet/SDH, Ethernet or Ethernet*66/64) available for APLL3. Connect to ground if XTAL1 is not used.                                                                                                                                                                                                                                               |

| B12        | XTAL1_OUT                                        | 0              | Analog              | Crystal oscillator 1 output. Leave open if XTAL1 is not used.                                                                                                                                                                                                                                                                                                                                                              |

| A10        | XTAL2_IN                                         | 1              | Analog              | Crystal oscillator 2 input.  Determines first of two frequency families (chosen from Sonet/SDH, Ethernet or Ethernet*66/64) available for APLL3. Connect to ground if XTAL2 is not used                                                                                                                                                                                                                                    |

| B10        | XTAL2_OUT                                        | 0              | Analog              | Crystal oscillator 2 output.<br>Leave open if XTAL2 is not used.                                                                                                                                                                                                                                                                                                                                                           |

|            |                                                  |                |                     | Lock Signal                                                                                                                                                                                                                                                                                                                                                                                                                |

| E9         | DPLL2_LOCK                                       | 0              | CMOS                | DPLL2_LOCK This pin goes high when DPLL2 is locked                                                                                                                                                                                                                                                                                                                                                                         |

| Н9         | DPLL1_LOCK                                       | 0              | CMOS                | DPLL1_LOCK This pin goes high when DPLL1 is locked                                                                                                                                                                                                                                                                                                                                                                         |

|            | - 1                                              |                | Mi                  | croprocessor Interface                                                                                                                                                                                                                                                                                                                                                                                                     |

| J9         | INT_REQ                                          | O<br>Tri-state | CMOS                | INT_REQ: Interrupt Request This pin is used as an interrupt request.                                                                                                                                                                                                                                                                                                                                                       |

| B11<br>C11 | MPU_MODE1/<br>I2CM_SCL<br>MPU_MODE0/<br>I2CM_SDA | I/O<br>pull-up | CMOS/<br>Open Drain | MPU_MODE[1:0]: Microprocessor Interface Mode Selection During reset, these pins determine the default value of the MPU_SEL_CNFG[1:0] bits as follows: 00: I2C mode 01 ~ 10: Reserved 11: I2C master (EEPROM) mode I2CM_SCL: Serial Clock Line In I2C master mode, the serial clock is output on this pin. I2CM_SDA: Serial Data Input for I2C Master Mode In I2C master mode, this pin is used as the for the serial data. |

| D9         | I2C_AD2                                          | l<br>pull-down | CMOS                | I2C_AD2: Device Address Bit 2 I2C_AD[2:1] pins are the address bus of the microprocessor interface.                                                                                                                                                                                                                                                                                                                        |

| E5         | I2C_AD1                                          | l<br>pull-down | CMOS                | I2C_AD1: Device Address Bit 1 I2C_AD[2:1] pins are the address bus of the microprocessor interface.                                                                                                                                                                                                                                                                                                                        |

| D10        | I2C_SCL                                          | I              | CMOS                | I2C_SCL: Serial Clock Line The serial clock is input on this pin.                                                                                                                                                                                                                                                                                                                                                          |

| C5         | I2C_SDA                                          | I/O            | Open Drain          | I2C_SDA: Serial Data Input/Output This pin is used as the input/output for the serial data.                                                                                                                                                                                                                                                                                                                                |

|            | 1                                                |                | J                   | TAG (per IEEE 1149.1)                                                                                                                                                                                                                                                                                                                                                                                                      |

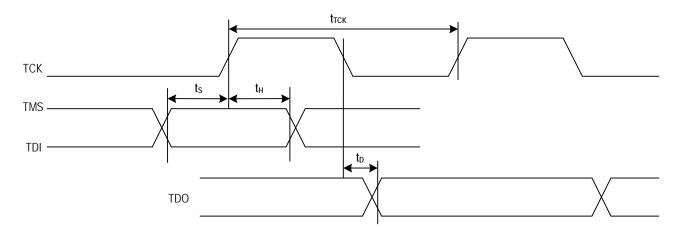

| F1         | TMS                                              | l<br>pull-up   | CMOS                | TMS: JTAG Test Mode Select The signal on this pin controls the JTAG test performance and is sampled on the rising edge of TCK.                                                                                                                                                                                                                                                                                             |

| K3         | TRSTB                                            | l<br>pull-up   | CMOS                | TRSTB: JTAG Test Reset (Active Low) A low signal on this pin resets the JTAG test port. This pin should be connected to ground when JTAG is not used.                                                                                                                                                                                                                                                                      |

| G1         | TCK                                              | l<br>pull-down | CMOS                | TCK: JTAG Test Clock The clock for the JTAG test is input on this pin. TDI and TMS are sampled on the rising edge of TCK and TDO is updated on the falling edge of TCK.  If TCK is idle at a low level, all stored-state devices contained in the test logic will indefinitely retain their state.                                                                                                                         |

| L3         | TDI                                              | l<br>pull-up   | CMOS                | TDI: JTAG Test Data Input The test data are input on this pin. They are clocked into the device on the rising edge of TCK.                                                                                                                                                                                                                                                                                                 |

Table 1: Pin Description (Continued)

| Pin No.                                                                  | Name     | I/O            | Туре | Description                                                                                                                                                                                                         |

|--------------------------------------------------------------------------|----------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L5                                                                       | TDO      | O<br>tri-state | CMOS | TDO: JTAG Test Data Output The test data are output on this pin. They are clocked out of the device on the falling edge of TCK. TDO pin outputs a high impedance signal except during the process of data scanning. |

|                                                                          |          | •              | •    | Power & Ground                                                                                                                                                                                                      |

| C1, C6, C7, D2, F2, F9,<br>G2, H2, K1, K2                                | VDDA     | Power          | -    | VDDA: Analog Core Power - +3.3V DC nominal                                                                                                                                                                          |

| A5, A7, B2, B3, L4, M4                                                   | VDDAO    | Power          |      | VDDAO: Analog Output Power - +3.3V DC nominal                                                                                                                                                                       |

| E4, E6, L7, M8                                                           | VDDDO    | Power          |      | VDDDO: Digital Output Power - +3.3V DC nominal                                                                                                                                                                      |

| D5, F7                                                                   | VDDD     | Power          |      | VDDD: Digital Core Power - +3.3V DC nominal                                                                                                                                                                         |

| L10, H12                                                                 | VDDD_1_8 | Power          |      | VDDD_1_8: Digital Core Power - +1.8V DC nominal                                                                                                                                                                     |

| B9, C2, D1, D6, D7, E2,<br>E8, F3, F8, H3, L1, L2                        | VSSA     | Ground         | -    | VSSA: Ground                                                                                                                                                                                                        |

| B1, B4, B5, B7, K4, M3                                                   | VSSAO    | Ground         |      | VSSAO: Ground                                                                                                                                                                                                       |

| E7, F4, K7, M7                                                           | VSSDO    | Ground         |      | VSSDO: Ground                                                                                                                                                                                                       |

| D4, F6, H11, L9                                                          | VSSD     | Ground         |      | VSSD: Ground                                                                                                                                                                                                        |

| D3                                                                       | VSSCOM   | Ground         | -    | VSSCOM: Ground                                                                                                                                                                                                      |

| C3, F5, G4, G5, G6, G8,<br>H4, H5, H6, H7, H8, J3,<br>J4, J5, J6, J7, J8 | VSS      | Ground         | -    | VSS: Ground                                                                                                                                                                                                         |

|                                                                          |          |                |      | Other                                                                                                                                                                                                               |

| C8, C10, E3, G3, G7,<br>G9, L6                                           | IC       | -              | -    | IC: Internal Connection Internal Use. This pin must be left open for normal operation.                                                                                                                              |

# 2.1 RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

# 2.1.1 INPUTS

#### **Control Pins**

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

### Single-Ended Clock Inputs

For protection, unused single-ended clock inputs should be tied to ground.

#### **Differential Clock Inputs**

For applications not requiring the use of a differential input, both \*\_POS and \*\_NEG can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from \_POS to ground.

### XTAL Inputs

For applications not requiring the use of a crystal oscillator input, both \_IN and \_OUT can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from \_IN to ground.

#### 2.1.2 OUTPUTS

#### Status Pins

For applications not requiring the use of a status pin, we recommend bringing out to a test point for debugging purposes.

## Single-Ended Clock Outputs

All unused single-ended clock outputs can be left floating, or can be brought out to a test point for debugging purposes.

### **Differential Clock Outputs**

All unused differential outputs can be left floating. We recommend that there is no trace attached. Both sides of the differential output pair should either be left floating or terminated.

### 2.2 RESET OPERATION

The device must be reset properly in order to ensure operations conform with specification.

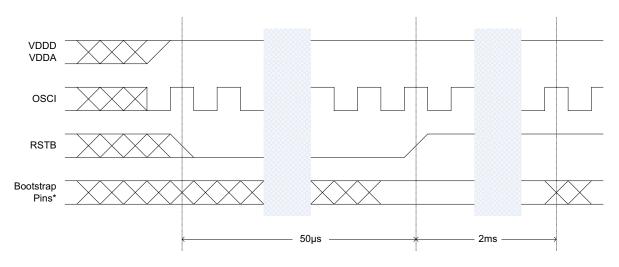

To properly reset the device, the RSTB pin must be held at a low value for at least 50 usec. The device should be brought out of reset only at the time when power supplies are stabilized and the system clock is available on OSCi pin. The RSTB can be held low until this time, or pulsed low for at least 50us after this time.

The bootstrap pins (XO\_FREQ[2:0], MPU\_MODE[1:0], I2C\_AD[2:1], MS/SL, SONET/SDH) need to be held at desired states for at least 2ms after de-assertion of RSTB pin to allow correct sampling. See Figure 3 for detail.

If loading from an EEPROM, the maximum time from RSTB deassert to have stable clocks is 100ms. Note that if there is a bad EEPROM read sequence and the EEPROM loading is repeated once or twice (three times halts the device), then this time can be 2 or 3 times longer respectively. If not loading from EEPROM the maximum time from RSTB de-assert to have stable clocks is 10ms.

An on-board reset circuit or a commercially available voltage supervisory can be used to generate the reset signal. It is also feasible to use a standalone power-up RC reset circuit. When using a power-up RC reset circuit, careful consideration must be taken into account to fine tune the circuit properly based on each power supply's specification to ensure the power supply rise time is fast enough with respect to the RC time constant of the RC circuit.

\* Bootstrap pins are: XO\_FREQ[2:0], MPU\_MODE[1:0], I2C\_AD[2:1], MS/SL, SONET/SDH

Figure 2. Reset timing diagram

# 2.3 MS/SL PIN USAGE

The MS/SL pin is used for timing card redundancy applications where there is a primary and secondary timing card in the system. For other applications, this pin should be left unconnected or connected to an external pull-up.

For more information, see AN-901, *How to Implement Master/Slave for SETS and SMU Devices on Timing Redundancy Designs.*

# 3 FUNCTIONAL DESCRIPTION

# 3.1 SYNCHRONOUS ETHERNET (SYNCE), SONET, AND SDH SYSTEM ARCHITECTURES

82P33731integrates key features that allows the device to be used in Synchronous Ethernet, SONET and SDH applications. There are several key synchronization standards that are important to meet for such a system, they are:

- ITU-T Recommendation G.8262, Timing characteristics of Synchronous Ethernet Equipment slave clock (EEC)

- ITU-T Recommendation G.8264, Distribution of timing through packet networks

- ITU-T Recommendation G.812, Timing requirements of slave clocks suitable for use as node clocks in synchronization networks.

- ITU-T Recommendation G.813, Timing characteristics of SDH equipment slave clocks (SEC).

- GR-253-CORE Telcordia Technologies Generic Requirements -Issue 5, October 2009

- GR-1244-CORE Telcordia Technologies Generic Requirements -Issue 4, October 2009

- ATIS-0900101.2006 T1.101 Synchronization Interface Standard

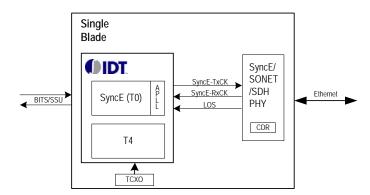

Figure 3 shows a single blade architecture that it is usually used in simple equipment. As an example, for a specific 10G PHY, the maximum

jitter requirement is 0.3ps from 10 kHz to 20 MHz. The 82P33731 does meet this tight jitter requirement.

Figure 3. SyncE/SONET/SDH single blade application

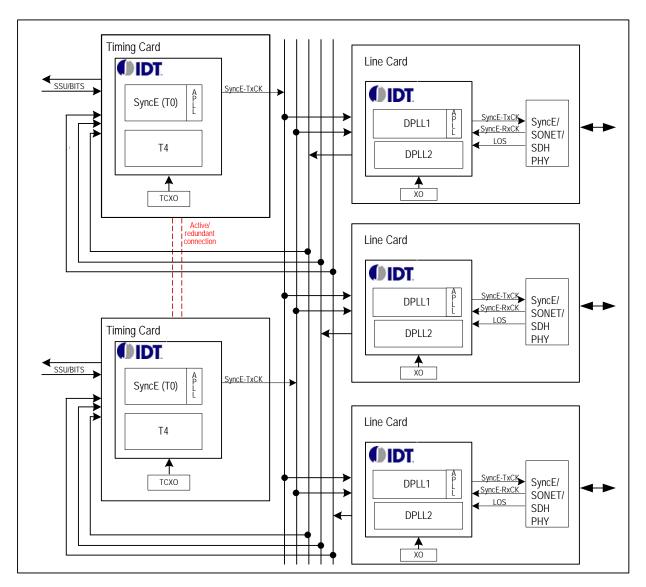

Figure 4 shows an active/redundant architecture, as described before it is usually used in Telecom equipment that are designed to have a redundant timing card in case of primary timing card failure. The redundant timing card mimics the output of the active timing card, so in case of failure the system will still provide proper synchronization.

Figure 4. SyncE/SONET/SDH active/redundant application

### 3.2 HARDWARE FUNCTIONAL DESCRIPTION

#### 3.2.1 SYSTEM CLOCK

A crystal oscillator should be used as an input on the OSCI pin. This clock is provided for the device as a system clock. The system clock is used as a reference clock for all the internal circuits. The active edge of the system clock can be selected by the OSC\_EDGE bit in xo\_freq\_cnfg register.

Eight common oscillator frequencies can be used for the stable System Clock. The oscillator frequency can be set by pins or by xo\_freq\_cnfg register as shown in Table 2.

**Table 2: Oscillator Frequencies**

| xo_freq[2:0] pins<br>xo_freq_cnfg[2:0] bits | Oscillator Frequency (MHz) |

|---------------------------------------------|----------------------------|

| 000                                         | 10.000                     |

| 001                                         | 12.800                     |

| 010                                         | 13.000                     |

| 011                                         | 19.440                     |

| 100                                         | 20.000                     |

| 101                                         | 24.576                     |

| 110                                         | 25.000                     |

| 111                                         | 30.720                     |

An offset from the nominal frequency may be compensated by setting the NOMINAL\_FREQ\_VALUE[23:0] bits. The calibration range is within  $\pm 741$  ppm.

The crystal oscillator should be chosen accordingly to meet different applications and standard requirements. (See AN-807 Recommended Crystal Oscillators for NetSynchro WAN PLL).

### 3.2.2 MODES OF OPERATION

### 3.2.2.1 DPLL1 Operating Mode

The DPLL1 can operate in several different modes as shown in Table 3.

The DPLL1 operating mode is controlled by the DPLL1\_OPERAT-ING\_MODE[4:0] bits

**Table 3: DPLL1 Operating Mode Control**

| DPLL1_OPERATING_MODE[4:0] | DPLL1 Operating Mode                          |

|---------------------------|-----------------------------------------------|

| 00000                     | Automatic                                     |

| 00001                     | Forced - Free-Run                             |

| 00010                     | Forced - Holdover                             |

| 00011                     | Reserved                                      |

| 00100                     | Forced - Locked                               |

| 00101                     | Forced - Pre-Locked2                          |

| 00110                     | Forced - Pre-Locked                           |

| 00111                     | Forced - Lost-Phase                           |

| 01000-01001               | Reserved                                      |

| 01010                     | DCO write frequency<br>see Chapter 3.2.2.1.6) |

| 10010 - 11111             | Reserved                                      |

| 10011-11111               | Reserved                                      |

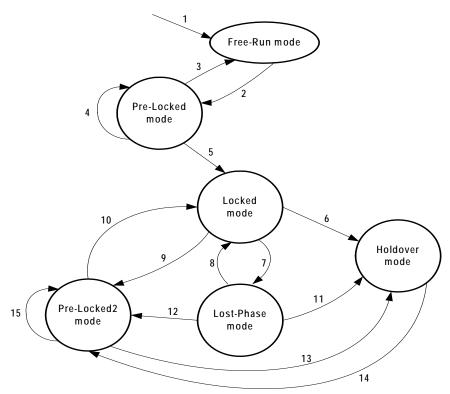

When the operating mode is switched automatically, the operation of the internal state machine is shown in Figure 5.

Whether the operating mode is under external control or is switched automatically, the current operating mode is always indicated by the DPLL1\_DPLL\_OPERATING\_STS[4:0] bits. When the operating mode switches, the DPLL1\_OPERATING\_STS bit will be set. If the DPLL1\_OPERATING\_STS bit is '1', an interrupt will be generated if the corresponding mask bit is set to "1", the mask bit is set to "0" by default.

Figure 5. DPLL Automatic Operating Mode

#### Notes to Figure 5:

- 1. Reset.

- 2. An input clock is selected.

- 3. The DPLL selected input clock is disqualified AND No qualified input clock is available.

- 4. The DPLL selected input clock is switched to another one.

- 5. The DPLL selected input clock is locked (the DPLL\_LOCK bit is '1').

- 6. The DPLL selected input clock is disqualified AND No qualified input clock is available.

- 7. The DPLL selected input clock is unlocked (the DPLL\_LOCK bit is '0').

- 8. The DPLL selected input clock is locked again (the DPLL\_LOCK bit is '1').

- 9. The DPLL selected input clock is switched to another one.

- 10. The DPLL selected input clock is locked (the DPLL\_LOCK bit is '1').

- 11. The DPLL selected input clock is disqualified AND No qualified input clock is available.

- 12. The DPLL selected input clock is switched to another one.

- 13. The DPLL selected input clock is disqualified AND No qualified input clock is available.

- 14. An input clock is selected.

- 15. The DPLL selected input clock is switched to another one.

The causes of Item 4, 9, 12, 15 - 'the *DPLL* selected input clock is switched to another one' - are: (The *DPLL* selected input clock is disqualified **AND** Another input clock is switched to) **OR** (In Revertive switching, a qualified input clock with a higher priority is switched to) **OR** (The DPLL selected input clock is switched to another one Forced selection).

#### 3.2.2.1.1 Free-Run Mode

In Free-Run mode, the DPLL1 output refers to the system clock and is not affected by any input clock. The accuracy of the DPLL1 output is equal to that of the system clock.

#### 3.2.2.1.2 Pre-Locked Mode

In Pre-Locked mode, the DPLL1 output attempts to track the selected input clock.

The Pre-Locked mode is a secondary, temporary mode.

#### 3.2.2.1.3 Locked Mode

In Locked mode, the DPLL1 is locked to the input clock. The phase and frequency offset of the DPLL1 output track those of the DPLL1 selected input clock.

For a closed loop, different bandwidths and damping factors can be used depending on DPLL locking stages: starting, acquisition and locked.

In the first two seconds when the DPLL1 attempts to lock to the selected input clock, the starting bandwidth and damping factor are used. They are set by the DPLL1\_START\_BW[4:0] bits and the DPLL1\_START\_DAMPING[2:0] bits respectively.

During the acquisition, the acquisition bandwidth and damping factor are used. They are set by the DPLL1\_ACQ\_BW[4:0] bits and the DPLL1\_ACQ\_DAMPING[2:0] bits respectively.

When the DPLL1 is locked, the locked bandwidth and damping factor are used. They are set by the DPLL1\_LOCKED\_BW[4:0] bits and the DPLL1\_LOCKED\_DAMPING[2:0] bits respectively.

The corresponding bandwidth and damping factor are used when the DPLL1 operates in different locking stages: starting, acquisition and locked, as controlled by the device automatically.

The locked bandwidth is selectable can be set as shown in Table 4.

Table 4: DPLL1 Locked Bandwidth

| DPLL1_LOCKED_BW[4:0] | BW        | Application                                             |

|----------------------|-----------|---------------------------------------------------------|

| 00000                | 0.090 mHz |                                                         |

| 00001                | 0.27 mHz  |                                                         |

| 00010                | 0.90 mHz  | stratum 3E, BW<1mHz                                     |

| 00011                | 2.9 mHz   | G.812 Type I, BW< 3mHz                                  |

| 00100                | 4.3 mHz   |                                                         |

| 00101                | 8.7 mHz   |                                                         |

| 00110                | 17 mHz    |                                                         |

| 00111                | 35 mHz    |                                                         |

| 01000                | 69 mHz    |                                                         |

| 01001                | 92 mHz    | GR-253 stratum 3, SMC and EEC-<br>option, 2, BW ≤ 0.1Hz |

| 01010                | 277 mHz   |                                                         |

| 01011                | 554 mHz   |                                                         |

| 01100                | 1.1 Hz    | EEC-option 1, 1≤BW ≤10<br>GR-1244 stratum 3, BW≤3Hz     |

| 01101                | 2.2 Hz    | EEC-option 1, 1≤BW ≤10<br>GR-1244 stratum 3, BW≤3Hz     |

| 01110                | 4.4 Hz    | EEC-option 1, 1≤BW ≤10                                  |

| 01111                | 8.9 Hz    | EEC-option 1, 1 <u>&lt;</u> BW <u>&lt;</u> 10           |

| 10000                | 18 Hz     |                                                         |

| 10001                | 35 Hz     |                                                         |

| 10010                | 71 Hz     |                                                         |

| 10011                | 142 Hz    |                                                         |

| 10100                | 283 Hz    |                                                         |

| 10101                | 567 Hz    |                                                         |

| 10110-11111          | Reserved  |                                                         |

#### 3.2.2.1.4 Pre-Locked2 Mode

The Pre-Locked2 mode is a secondary, temporary mode.

#### 3.2.2.1.5 Lost-Phase Mode

In Lost-Phase mode, the DPLL1 output attempts to track the selected input clock.

The Lost-Phase mode is a secondary, temporary mode.

#### 3.2.2.1.6 DCO Control Modes

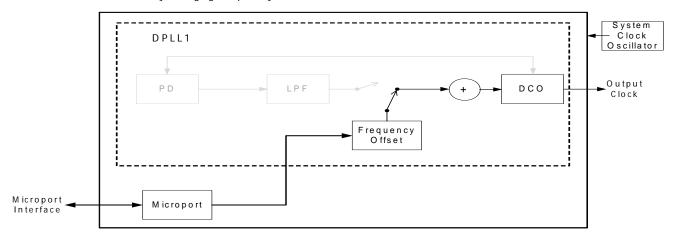

Figure 6 show a high level diagram of the DCO control architecture, it shows the DCO in DPLL1 being controlled. The DCO is a phase accumulator running at an internal clock. The DCO is controlled by a digital word that can represent phase offset or frequency offset. In the case of an IEEE 1588 application, the external processor will run the clock recovery servo algorithm and it will generate a frequency offset word to control the DCO.

The DCO control modes can be set by registers DPLL1\_operating\_mode\_cnfg for DPLL1.

Figure 6 shows the DCO being controlled by writing a frequency offset word into the DCO, then by changing temporarily the DCO's frequency, the phase of the clock (or 1PPS) being generated by the DCO will also change. The output phase change is the product of the frequency change times the duration for which the frequency change is applied for. Because the DCO's frequency word has a very fine resolution, the output phase can be adjusted in very fine steps. In this case the clock recovery servo algorithm controls the bandwidth and phase slope limiting. The frequency offset word can be written into DPLL1\_hold-over\_freq\_cnfg[39:0] bits of frequency configuration registers for DPLL12. This value is 2's complement signed number. Total range is +/-92 ppm, and the DCO programming resolution is [(77760 / 1638400) \* 2^-48] or ~1.686305041e-10 ppm. The DCO resolution is affected by the offset applied into the DCO, so when writing into the DCO, the programming resolution is [(77760/1638400) \* 2^-48] \* (1 + offset-in-ppm / 1e6).

Controlling the DCO's frequency for smaller fine resolution phase changes is a good method, but for bigger phase changes it is better to use the snap-alignment method. The snap phase alignment is fast but only provides coarse adjustment. The 82P33731 allows for both the fine phase adjustment by controlling the frequency of the DCO and the coarse phase adjustment by snap-aligning the output clock (or 1PPS), for details, see section 3.2.8.3 Output Phase control on page 31.

Figure 6. DCO frequency offset control functional block diagram

#### 3.2.2.1.7 Holdover Mode

In Holdover mode, the DPLL1 resorts to the stored frequency data acquired in Locked mode to control its output. The DPLL1 output is not phase locked to any input clock. The frequency offset acquiring method

is selected by the man\_holdover bit, auto\_avg bit, the hist\_mode [1:0] bits, and the avg\_mode[1:0] bits in DPLL1\_holdover\_mode\_cnfg registers as shown in Table 5:

Table 5: Frequency Offset Control in Holdover Mode

| man_hold<br>over | auto_avg | hist_mo    | ode [1:0] | avg_mode[1:0] |        | Frequency Offset Acquiring Method                                    |

|------------------|----------|------------|-----------|---------------|--------|----------------------------------------------------------------------|

|                  | 0        | don't      | -care     | don'          | t-care | Averaged                                                             |

|                  |          |            |           | 0             | 0      | Current averaged value with holdover filter BW of ~0.18mHz           |

|                  |          | 0          | 0         | 0             | 1      | Current averaged value with holdover filter BW of ~1.5mHz            |

|                  |          | U          | U         | 1             | 0      | Current averaged value with holdover filter BW of ~12mHz             |

|                  |          |            |           | 1             | 1      | Current averaged value with holdover filter BW of ~0.15Hz            |

|                  |          |            |           | 0             | 0      | Averaged value 1 second before with holdover filter BW of ~0.18mHz   |

|                  | 1        | 0          | 0         | 0             | 1      | Averaged value 1 second before with holdover filter BW of ~1.5mHz    |

|                  |          |            |           | 1             | 0      | Averaged value 1 second before with holdover filter BW of ~12mHz     |

| 0                |          |            |           | 1             | 1      | Averaged value 1 second before with holdover filter BW of ~0.15Hz    |

|                  |          |            |           | 0             | 0      | Averaged value 8 seconds before with holdover filter BW of ~0.18mHz  |

|                  |          | 0          | 1         | 0             | 1      | Averaged value 8 seconds before with holdover filter BW of ~1.5mHz   |

|                  |          | U          | l         | 1             | 0      | Averaged value 8 seconds before with holdover filter BW of ~12mHz    |

|                  |          |            |           | 1             | 1      | Averaged value 8 seconds before with holdover filter BW of ~0.15Hz   |

|                  |          |            |           | 0             | 0      | Averaged value 64 seconds before with holdover filter BW of ~0.18mHz |

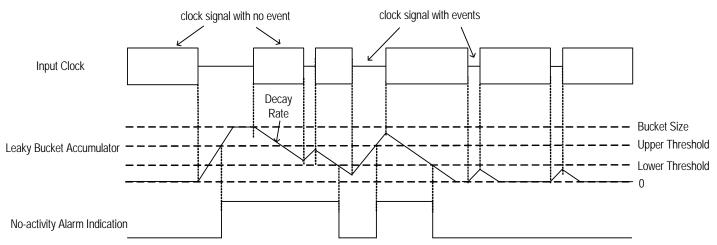

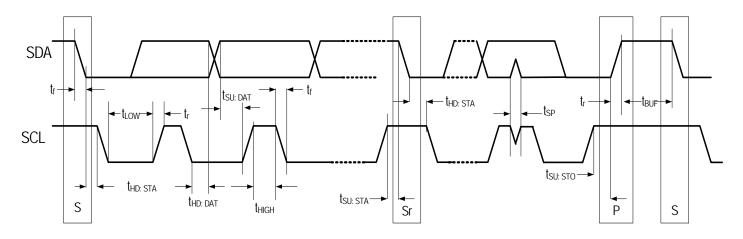

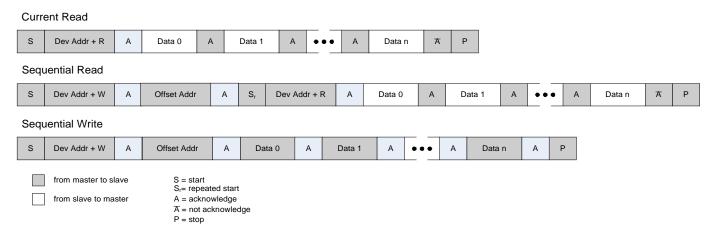

|                  |          | 1          | 0         | 0             | 1      | Averaged value 64 seconds before with holdover filter BW of ~1.5mHz  |