# 20A Switching Current, Up to 17V Output, Synchronous Boost Converter with Isolation NMOS Driver

# 1 Descriptions

The SC8329 is a synchronous boost converter fully integrated with a 6 m $\Omega$  low side power switch and a 11 m $\Omega$  high side power switch. The SC8329 supports wide input range from 2.7 V to 13 V. It has 20A switch current capability and is capable of providing an output voltage to 17 V.

The SC8329 adopts constant-off-time (COT) control topology, which provides fast transient response. It supports operating modes selection for PWM mode and PFM mode. The switching frequency is adjustable ranging from 200 kHz to 2.2 MHz by an external resistor. The SC8329 implements soft-stat and an adjustable output current limit function.

The SC8329 also supports full protections including input under-voltage lockout (UVLO), output over voltage protection at 20V (OVP), programmable cycle-by-cycle overcurrent protection (OCP) and thermal shut down protection. Furthermore, the SC8329 contains an NMOS driver for short circuit protection.

The SC8329 is available in FCQFN-15 package (4.0mm× 3.0mm).

# 3 Applications

- Portable POS terminals

- Bluetooth Speakers

- E-cigarettes

# 2 Features

- Wide input operating voltage from 2.7 V to 13 V

- Wide output range, from 4.5 V to 17V

- Up to 20-A programmable switching current limit

- Integrated 6 m $\Omega$  and 11 m $\Omega$  Power MOSFETs

- PFM and PWM mode selection

- 1.0 µA shutdown current

- Adjustable switching frequency: 200 kHz to 2.2 MHz

- Full protection of UVLO, OVP, OCP, OTP

- Short circuit protection with Isolation NMOS driver

- Available in QFN-15 package (4.0mm×3.0mm)

# 4 Device Information

| ORDER NUMBER | PACKAGE    | BODY SIZE          |

|--------------|------------|--------------------|

| SC8329       | 15 pin QFN | 4mm x 3mm x 0.75mm |

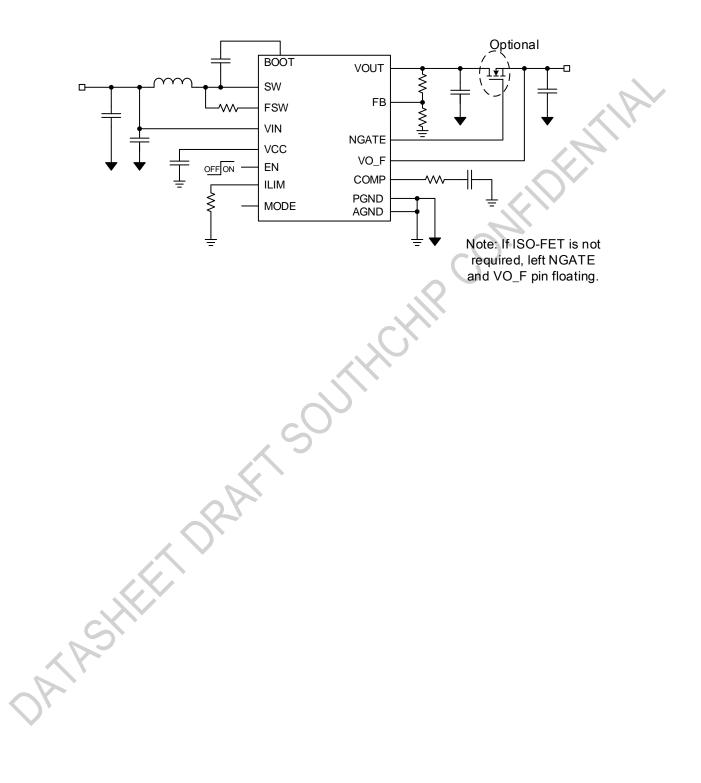

# 5 Typical Application Circuit

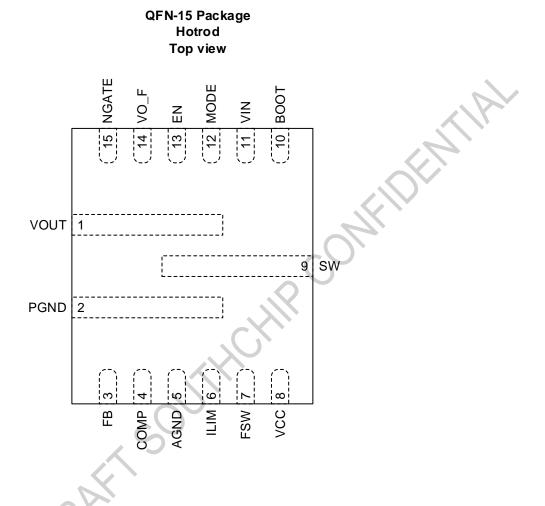

# 6 Terminal Configuration and Functions

| TE     | ERMINAL 1/O |                                                                                                                                                                                                             | DESCRIPTION                                                                         |  |  |

|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| NUMBER | NAME        | DUT O Output node of the boost.   ND I Power ground of IC.   'B I Feedback node for output voltage.   'MP I/O Connect resistor and capacitor to compensate the control loop.   'ND I/O Signal ground of IC. |                                                                                     |  |  |

| 1      | VOUT        | о                                                                                                                                                                                                           | Output node of the boost.                                                           |  |  |

| 2      | PGND        | I                                                                                                                                                                                                           | Power ground of IC.                                                                 |  |  |

| 3      | FB          | I                                                                                                                                                                                                           | Feedback node for output voltage.                                                   |  |  |

| 4      | COMP        | I/O                                                                                                                                                                                                         | Connect resistor and capacitor to compensate the control loop.                      |  |  |

| 5      | AGND        | I/O                                                                                                                                                                                                         | Signal ground of IC.                                                                |  |  |

| 6      | ILIM        | I                                                                                                                                                                                                           | Peak current limit setting pin. Connect a resistor between ILIM and AGND.           |  |  |

| 7      | FSW         | I                                                                                                                                                                                                           | Switching frequency programming pin. Connect a resistor between FSW pin and SW pin. |  |  |

SOUTHCHIP CONFIDENTIAL

|    | VCC   | 0 | Output of an internal regulator. Connect a $1\mu$ F ceramic capacitor from VCC to AGNE pin close to the IC. The regulator provides supply for internal gate driver.                                           |

|----|-------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9  | SW    | I | Switching Node. Connect to inductor.                                                                                                                                                                          |

| 10 | воот  | 0 | A 100nF capacitor should be connected between BT and SW to bootstrap a buvoltage for high side MOSFET driver.                                                                                                 |

| 11 | VIN   | I | Power supply to the IC. Place a $1\mu$ F capacitor from this pin to PGND as close to th IC as possible.                                                                                                       |

| 12 | MODE  | I | Mode selection pin between PFM Mode and Forced PWM Mode at light load. Whe this pin is connected to analog ground, the device works in FPWM mode. When th pin is left floating, the device works in PFM mode. |

| 13 | EN    | I | Enable logic input pin. Logic high level enables the device, nor disables the device When not in use, connect EN to VIN for automatic start-up.                                                               |

| 14 | VO_F  | I | Connect this pin to the source of NMOS.                                                                                                                                                                       |

| 15 | NGATE | 0 | NMOS gate driver. This pin drives an external NMOS for short circuit protection.                                                                                                                              |

|    |       |   | SON                                                                                                                                                                                                           |

| OA | ASHE  |   | Att                                                                                                                                                                                                           |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                          |                                      | MIN  | I MAX | Unit |

|--------------------------|--------------------------------------|------|-------|------|

|                          | BOOT                                 | -0.3 | 26.5  | V    |

| Voltage range at         | VIN, SW, FSW, VOUT, VO_F             | -0.3 | 20    | V    |

| terminals <sup>(2)</sup> | EN, VCC, COMP, MODE, FB              | -0.3 | 6.5   | V    |

|                          | NGATE                                | -0.3 | 26.5  | V    |

| TJ                       | Operating junction temperature range | -40  | 150   | °C   |

| T <sub>stg</sub>         | Storage temperature range            | -65  | 150   | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

# 7.2 Handling Ratings

| PARAMETER          | DEFINITION                                                        | MIN  | МАХ | UNIT |

|--------------------|-------------------------------------------------------------------|------|-----|------|

| ESD <sup>(1)</sup> | Human body model (HBM) ESD stress voltage <sup>(2)</sup> All pins | -2   | 2   | kV   |

| E3D(*)             | Charged device model (CDM) ESD stress voltage <sup>(3)</sup>      | -500 | 500 | V    |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Thermal Information

| PARAMETER         | DEFINITION                                                                                            | ТҮР  | UNIT |

|-------------------|-------------------------------------------------------------------------------------------------------|------|------|

| R <sub>θJA</sub>  | Junction-to-ambient thermal resistance, measured on SC8329_EVM_C53, 4 layers 65mm x 65mm x 1.6mm PCB. | 29.5 | ℃/W  |

| R <sub>θJCT</sub> | Junction-to-case thermal resistance (top)                                                             | 26   | °C/W |

| Rejcb             | Junction-to-case thermal resistance (bottom)                                                          | 3.5  | °C/W |

# 7.4 Recommended Operating Conditions

| PARAMETER        | DEFINITION           | MIN | ТҮР | МАХ | UNIT |

|------------------|----------------------|-----|-----|-----|------|

| VIN              | Input voltage range  | 2.7 |     | 13  | V    |

| Vout             | Output voltage range | 4.5 |     | 17  | V    |

| C <sub>IN</sub>  | Input Capacitance    | 30  |     |     | μF   |

| C <sub>OUT</sub> | Output capacitance   | 60  |     |     | μF   |

| L                | Inductance           |     | 1.5 |     | μH   |

SOUTHCHIP CONFIDENTIAL

| Fsw            | Switching frequency range     |          | 200 | 2200 | kHz |

|----------------|-------------------------------|----------|-----|------|-----|

| T <sub>A</sub> | Operating ambient temperatu   | re       | -40 | 85   | °C  |

| TJ             | Operating junction temperatur | e        | -40 | 125  | °C  |

|                | RA                            | Southorn |     |      |     |

| OA             | ASHE                          |          |     |      |     |

|                |                               |          |     |      |     |

|                |                               |          |     |      |     |

### 7.5 Electrical Characteristics

$T_J$  = 25°C and  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 9V, unless otherwise noted.

| PARAMETER                |                                                 | TEST CONDITIONS                                                     | MIN | ТҮР   | МАХ      | UNIT |

|--------------------------|-------------------------------------------------|---------------------------------------------------------------------|-----|-------|----------|------|

| POWER SUPP               | LY                                              |                                                                     |     |       |          |      |

| VIN                      | Input voltage range                             |                                                                     | 2.7 |       | 13       | V    |

| Vin uvlo                 | Under Voltage lockout threshold (UVLO)          | V <sub>IN</sub> rising                                              |     | 2.6   | 2.7      | V    |

| VIN_OVEO                 | Under Volkage lockout inteshold (0 VEO)         | V <sub>IN</sub> falling                                             |     | 2.4   | $ \leq $ |      |

| la                       | Operating quiescent current from VIN            | MODE = 5V, EN = 5V, FB = 2V, VIN = 5V,<br>VOUT = 10V, non-switching |     | 80    |          | μΑ   |

| ISHUT                    | Quiescent current from VOUT pin during shutdown | EN = 0V, VIN = 3.6V                                                 |     | 1     |          | μΑ   |

| OUTPUT                   |                                                 |                                                                     |     | ~     |          |      |

| Vout                     | Output voltage range                            |                                                                     | 4.5 |       | 17       | V    |

| V <sub>FB_REF</sub>      | Reference voltage at FB pin                     |                                                                     |     | 1.000 |          | V    |

| Error Amplifier          |                                                 |                                                                     |     |       |          |      |

| I <sub>SINK</sub>        | Comp pin sink current                           |                                                                     |     |       | 20       | μA   |

| ISOURCE                  | Comp pin source current                         |                                                                     |     |       | 20       | μA   |

| GEA                      | Error amplifier transconductance                |                                                                     |     | 190   |          | μA/V |

| POWER SWITC              | ж                                               | $\sim$                                                              |     |       |          |      |

| R <sub>DS(ON)</sub>      | High side MOSFET on-resistance                  |                                                                     |     | 11    |          | mΩ   |

| NDS(UN)                  | Low side MOSFET on-resistance                   | 5                                                                   |     | 6     |          | mΩ   |

| SWITCHING F              | REQUENCY                                        |                                                                     |     |       |          |      |

| f <sub>SW</sub>          | Switching frequency                             |                                                                     | 200 |       | 2200     | kHz  |

| t <sub>ON_min</sub>      | Minimum on-time                                 |                                                                     |     | 70    |          | ns   |

| VCC AND DRIV             | /ER                                             |                                                                     |     |       |          |      |

| Vcc                      | Vcc clamp voltage                               |                                                                     |     | 5     |          | V    |

| Vcc_uvlo                 | Vcc UVLO threshold                              |                                                                     |     | 2.5   |          | V    |

| V <sub>CC_UVLO_HYS</sub> | Vcc UVLO hysteresis                             |                                                                     |     | 200   |          | mV   |

| V <sub>NGATE</sub>       | NGATE voltage                                   | Respect to VO_F                                                     |     | 5     |          | V    |

| INGATE                   | NGATE capabilities                              |                                                                     |     | 10    |          | μA   |

| LOGIC CONTR              | OL                                              |                                                                     |     |       |          |      |

| VENH                     | EN high threshold voltage                       |                                                                     |     |       | 1.2      | V    |

| VENL                     | EN low threshold voltage                        |                                                                     | 0.4 |       |          | V    |

| R <sub>EN_PD</sub>       | EN internal pull-down resistance                |                                                                     |     | 800   |          | kΩ   |

| VMODEH                   | MODE high threshold voltage                     |                                                                     |     |       | 4.0      | V    |

| VMODEL                   | MODE low threshold voltage                      |                                                                     | 1.5 |       |          | V    |

| CURRENT LIM              |                                                 | •                                                                   |     |       |          | -    |

SOUTHCHIP CONFIDENTIAL

| SOFT START |                                           |                              |       |   |

|------------|-------------------------------------------|------------------------------|-------|---|

| Tss        |                                           |                              | 1     |   |

|            | Soft start time                           |                              | 5     |   |

| PROTECTION |                                           |                              | 1     |   |

| Vovp       | Output over voltage protection threshold  | V <sub>OUT</sub> rising      | 19 20 | 1 |

| Vovp_hys   | Output over voltage protection hysteresis | VOUT falling below VOVP      | 700   |   |

| Тот        | Over temperature threshold                | TJ rising                    | 165   |   |

| Tot_hys    | Over temperature hysteresis               | $T_J$ falling below $T_{OT}$ | 15    |   |

|            | SHEET                                     | South                        |       |   |

## 8 Feature Description

## 8.1 Chip enable and under voltage lockout

The SC8329 has an enable control pin EN: pulling it high enables the IC and pulling it low disables the IC. Connect EN to VIN for automatic start-up.

The SC8329 features under voltage lockout (UVLO) to prevent battery from excessive discharging and prevent the chip from malfunctioning at low input voltage. Once the falling voltage at VIN pin below the UVLO threshold (2.4V) is detected, the IC is disabled. The IC resumes to normal operation when the rising voltage at VIN pin is 200mV above the UVLO threshold.

# 8.2 Soft start

The SC8329 has a fixed soft start function to prevent high inrush current during start-up without any external circuit. During soft start phase, the output voltage is achieved by slowly ramping up the target regulation voltage.

### 8.3 Mode Selection

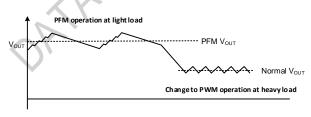

The SC8329 integrates two different operating modes: PWM mode and PFM mode.

The SC8329 works in PWM mode when MODE pin is connected to AGND. In PWM mode, the IC always works with constant switching frequency for the whole load range. This helps achieve the best output voltage performance and fast transient response, but the efficiency is low at light load condition because of the high switching loss.

The SC8329 works in PFM mode to improve efficiency at light load when MODE pin is left floating. In PFM mode, the IC still works with constant switching frequency under heavy load condition, but under light load condition, the IC automatically changes to pulse frequency modulation operation to reduce the switching loss. The efficiency can be improved under light load condition while output voltage ripple will be a little larger compared to PWM operation. Below figure 1 shows the output voltage behavior of PFM mode.

Figure 1. PFM mode illustration

## 8.4 Output Voltage Setting

The output voltage is fed back to FB pin through an external resistor divider. The output voltage can be set by the resistor divider as following equation.

$$V_{\rm OUT} = V_{\rm FB\_REF} \times (1 + \frac{R_{\rm UP}}{R_{\rm DOWN}})$$

Where:

- V<sub>FB\_REF</sub> = 1.000V

- R<sub>UP</sub> and R<sub>DOWN</sub> are the resistances of resistor divider.

# 8.5 Adjustable Switching Frequency

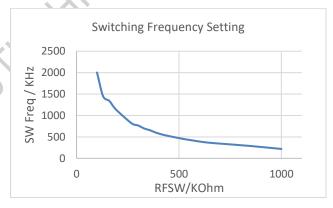

A resistor should always be connected from the FSW pin to SW pin for proper operation. The switching frequency can be set by a resistor between FSW pin and SW pin. Adjustable switching frequency ranges from 200 kHz to 2.2MHz. The relationship between switching frequency and R<sub>FSW</sub> plotting as follows.

#### Figure 2 Switching Frequency Setting

### 8.6 Load Isolation N-MOS Gate Driver

SC8329 builds in load isolation N-MOS gate driver to disconnect VO\_F from VOUT when VO\_F short happens or SC8329 shuts down. Once SC8329 starts up, NGATE drives external isolation N-MOS with soft-starting. After VO\_F goes stable, SC8329 keeps driving external isolation FET fully on.

# 8.7 Output Overvoltage Protection (OVP)

Output overvoltage protection is available in SC8329 preventing the circuits connected to the output from excessive overvoltage. Once the output voltage is detected above threshold (typically 20V), the SC8329 stops switching immediately until the output voltage drops the hysteresis value lower than output overvoltage protection threshold.

### 8.8 Overcurrent Protection (OCP)

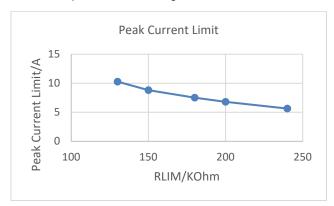

The SC8329 has a programmable cycle-by-cycle switching peak current limit. The threshold could be set by an external resistor between ILIM and AGND. In each cycle, the internal current circuit monitors the LS-FET current. Once the sensed current reaches to current limit threshold, the LS-FET turns off. RILIM is recommended as following equation.

$$R_{ILIM} \approx 1.25 * 10^6 / I_L$$

Where I<sub>L</sub> is peak current setting.

#### Figure 3 Peak Current Limit Setting

#### 8.9 Short Circuit Protection

The SC8329 integrates a NMOS driver for short circuit protection. Once short circuit is detected, the SC8329 drives external NMOS open and stops switching. After a while, the SC8329 drives external NMOS closed and restart (Hiccup mode).

#### 8.10 Over Temperature Protection (OTP)

The over temperature protection prevents the chip form operating at exceedingly high temperatures. Once the temperature of the die exceeds 165 °C, the SC8329 shuts down. And resumes normal operation when the die temperature drops below threshold (typically 150 °C).

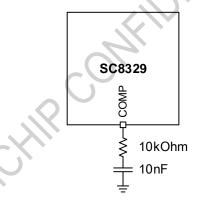

### 8.11 Feedback compensation (COMP)

The feedback loop can be compensated by adjusting the external components to the COMP pin. Typical values are like below.

Figure 4. Feedback loop setting

# **9** Application Information

# 9.1 Input and output capacitor selection

Because of inductor current ripple, the input voltage changes if there is parasite inductance and resistance between the power supply and the inductor. At least  $10\mu$ F input capacitance is required for small input voltage ripple and stability. The input capacitor can be electrolytic, tantalum or ceramic. If electrolytic or tantalum capacitor is used, at least  $1\mu$ F ceramic should be placed close to IC's VIN pin, to improve high frequency performance.

Since MLCC ceramic capacitor has good high frequency filtering with low ESR, above 60µF X5R or X7R capacitors with higher voltage rating than operating voltage with margin is recommended for small output voltage ripple and stability. For example, if the highest operating VOUT voltage is 12V, select at least 16V capacitor, and to ensure enough margin, 25V voltage rating capacitor is recommended.

The high capacitance electrolytic capacitor and tantalum capacitor can be used for stable output but capacitor voltage rating should be higher than the highest operating voltage. When the tantalum capacitor is used, at least  $1\mu$ F ceramic capacitor is placed in parallel. If the electrolytic capacitor is used, much more ceramic capacitors are required.

For large input current applications, a high capacitance electrolytic capacitor is required to reduce the impact of parasitic parameters of long conductors.

### 9.2 Inductor selection

For the SC8329 system stability, the inductance of  $1\mu$ H ~ 4.7 $\mu$ H inductor is required. High inductance ( $3.3\mu$ H ~ 4.7 $\mu$ H) is used in the system where the input voltage and output voltage gap is big, such as 3V VIN and 16V VOUT; Low inductance ( $1\mu$ H) is used in the system which the input voltage and output voltage difference is small but high current is required. Typically,  $1.5\mu$ H inductor is recommended. The inductance can be adjusted for high efficiency and optimization in application.

The inductor DC resistance value (DCR) affects the conduction loss of switching regulator, so around  $3m\Omega$  DCR is recommended for the first selection. If the power is relatively small, high DCR inductor can be selected. But if switch on current is high, just like around 10A, select the lowest DCR inductor as much as possible, because  $10m\Omega$  DCR also causes 1W power loss.

The inductor saturation current  $I_{\text{SAT}}$  should be higher than input output current with sufficient margin.

## 9.3 NMOS selection

The NMOS is connected between the output node of boost converter and subsequent circuits, which protects short circuit.

Considering PCB parasitic parameters during operation, driver voltage can be higher than VCC due to transient overshoot, and  $\pm 12V$  or higher V<sub>GS</sub> is recommended to secure sufficient margin.

The MOSFET current I<sub>D</sub> should be higher than the highest peak current with enough margin.

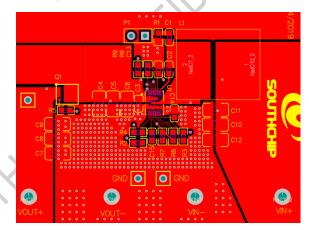

Figure 5 PCB layout reference

Efficient PCB layout can make SC8329 perform well. A poor layout could result in reduced performance. Some tips are suggested as follows to get a good performance.

1. Output capacitor (C3~C6) should be placed as closed as possible. Place a smaller ceramic (100nf) capacitor next to the output node of converter.

2. All traces connected to the SW pin should be as short as possible, and always use a ground plane under the switching regulator to minimize inter plane coupling.

3. Input loop should be as small as possible.

4. Place resistor divider as close to FB pin as possible and make sure traces connected FB far away from SW node.

5. Low-side resistor of FB resistor divider or peak current limit setting resistor should be connected to AGND for lower ripple and stable peak current limit. AGND and PGND should be connected with single point.

6. PGND vias closed to SC8329 should be as much as possible for enhanced thermal dissipation.

7. It is essential to adopt 4-layer PCB for high input current application.

# 9.4 Layout Guide

SOUTHCHIP CONFIDENTIAL

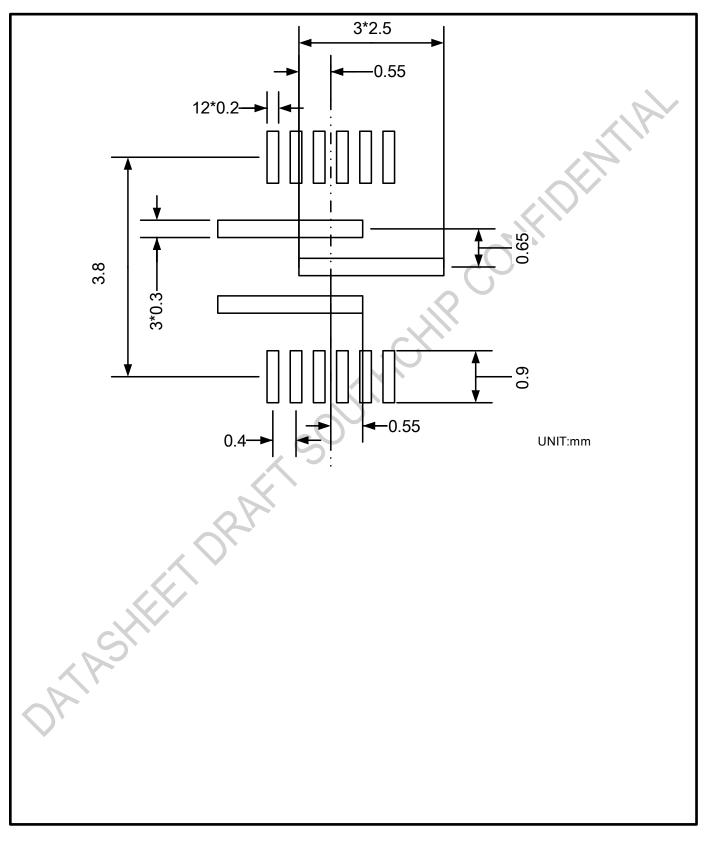

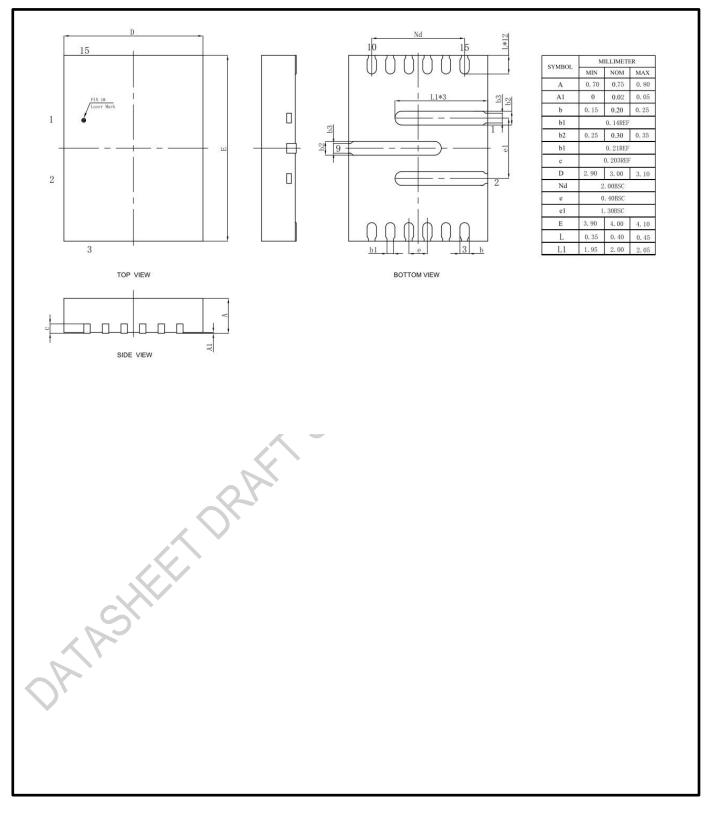

# **MECHANICAL DATA**

FCQFN15L

SOUTHCHIP CONFIDENTIAL

# **RECOMMENDED FOOTPRINT**