#### **NXP Semiconductors**

Data Sheet: Technical Data

# S32R274

# S32R274/S32R264 Series Data Sheet

Supports S32R274K, S32R274J, S32R264K and S32R264J

#### **Features**

- On-chip modules available within the device include the following features:

- Safety core: Power Architecture® e200Z4 32-bit CPU with checker core

- Dual issue computation cores: Power Architecture® e200Z7 32-bit CPU

- 2 MB on-chip code flash (FMC flash) with ECC

- 1.5 MB on-chip SRAM with ECC

- RADAR processing

- Signal Processing Toolbox (SPT) for RADAR signal processing acceleration

- Cross Timing Engine (CTE) for precise timing generation and triggering

- Waveform generation module (WGM) for chirp ramp generation

- 4x 12-bit  $\Sigma\Delta$ -ADC with 10 MSps

- One DAC with 10 MSps

- MIPICSI2 interface to connect external ADCs

- Memory Protection

- Each core memory protection unit provides 24 entries

- Data and instruction bus system memory protection unit (SMPU) with 16 region descriptors each

- Register protection

- · Clock Generation

- 40 MHz external crystal (XOSC)

- 16 MHz Internal oscillator (IRCOSC)

- Dual system PLL with one frequency modulated phase-locked loop (FMPLL)

- Low-jitter PLL to ΣΔ-ADC and DAC clock generation (not supported on SC66760x devices)

#### · Functional Safety

- Enables up to ASIL-D applications

- FCCU for fault collection and fault handling

- MEMU for memory error management

- Safe eDMA controller

- Self-Test Control Unit (STCU2)

- Error Injection Module (EIM)

- On-chip voltage monitoring

- Clock Monitor Unit (CMU)

#### Security

- Cryptographic Security Engine (CSE2)

- Supports censorship and life-cycle management

#### Timers

- Two Periodic Interval Timers (PIT) with 32-bit counter resolution

- Three System Timer Module (STM)

- Three Software Watchdog Timers (SWT)

- Two eTimer modules with 6 channels each

- One FlexPWM module for 12 PWM signals

#### • Communication Interfaces

- Two Serial Peripheral interface (SPI) modules

- One LINFlexD module

- Two inter-IC communication interface (I2C) modules

- One dual-channel FlexRay module with 128 message buffers

- Three FlexCAN modules with configurable buffers -CAN FD optionally supported on 2 FlexCAN modules

- One ENET MAC supporting MII/RMII/RGMII interface

- ZipWire high-speed serial communication

#### • Debug Functionality

- 4-pin JTAG interface and Nexus/Aurora interface for serial high-speed tracing

- e200Z7 core and e200Z4 core: Nexus development interface (NDI) per IEEE-ISTO 5001-2012 Class 3+

NXP reserves the right to change the production detail specifications as may be required to permit improvements in the design of its products.

- Two analog-to-digital converters (SAR ADC)

- Each ADC supports up to 16 input channels

- Cross Trigger Unit (CTU)

- On-chip voltage DC/DC regulator for core clock (VREG)

- Two Temperature Sensors (TSENS)

# **Table of Contents**

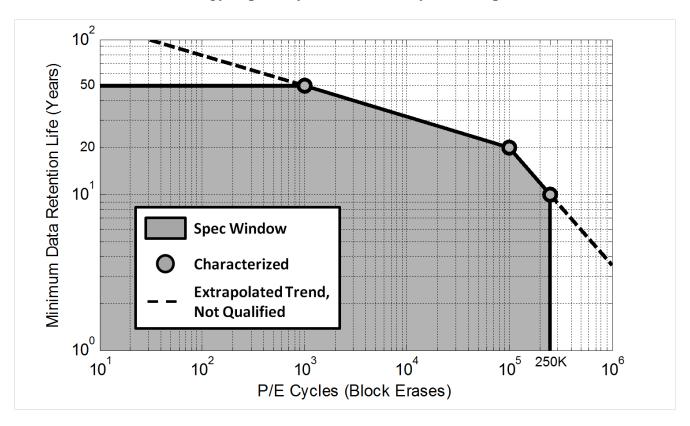

| 1 | Intro  | duction                                            | 4  |    | 8.4   | Data retention vs program/erase cycles                    |

|---|--------|----------------------------------------------------|----|----|-------|-----------------------------------------------------------|

|   | 1.1    | Family comparison                                  | 4  |    | 8.5   | Flash memory AC timing specifications                     |

|   | 1.2    | Feature list                                       | 5  |    | 8.6   | Flash memory read wait-state and address-pipeline control |

|   | 1.3    | Block diagram                                      | 9  |    |       | settings                                                  |

| 2 | Orde   | ring parts                                         | 9  | 9  | Com   | munication modules                                        |

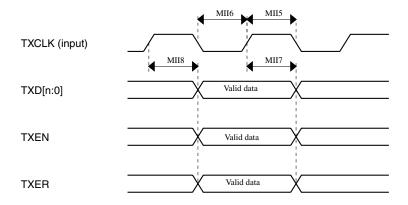

|   | 2.1    | Determining valid orderable parts                  |    |    | 9.1   | Ethernet switching specifications                         |

| 3 | Part i | dentification                                      |    |    | 9.2   | FlexRay timing parameters                                 |

|   | 3.1    | Description                                        |    |    | 9.3   | LVDS Fast Asynchronous Transmission (LFAST) electrical    |

|   | 3.2    | Fields                                             | 10 |    |       | characteristics5                                          |

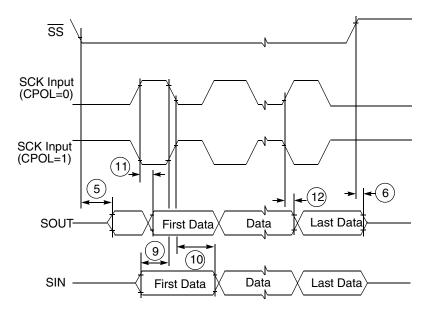

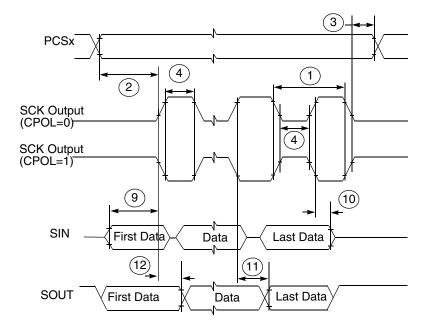

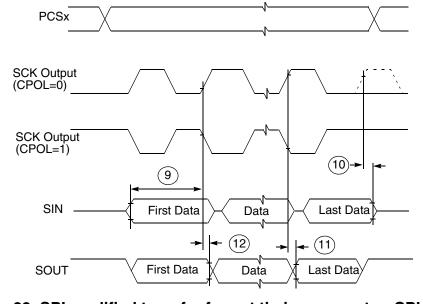

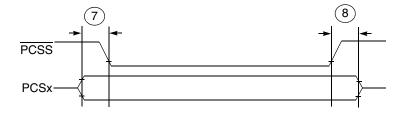

| 4 | Gene   | ral                                                | 11 |    | 9.4   | Serial Peripheral Interface (SPI) timing specifications5  |

|   | 4.1    | Absolute maximum ratings                           | 11 |    | 9.5   | LINFlexD timing specifications                            |

|   | 4.2    | Operating conditions                               | 13 |    | 9.6   | I2C timing5                                               |

|   | 4.3    | Supply current characteristics                     | 15 | 10 | Debu  | g modules6                                                |

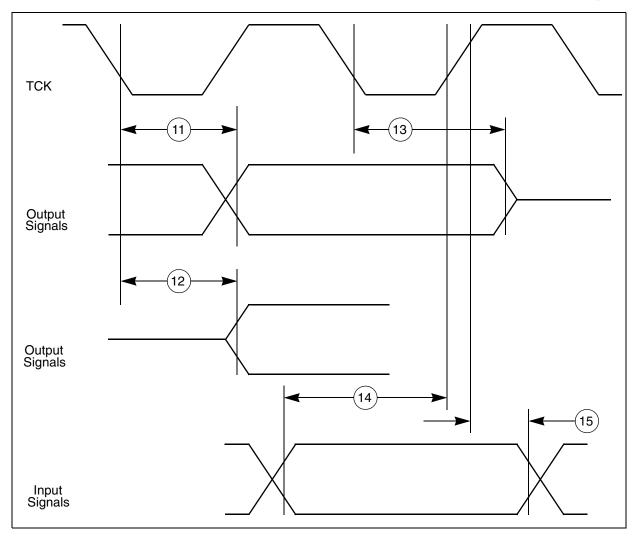

|   | 4.4    | Voltage regulator electrical characteristics       | 16 |    | 10.1  | JTAG/CJTAG interface timing                               |

|   | 4.5    | Electromagnetic Compatibility (EMC) specifications | 20 |    | 10.2  | Nexus Aurora debug port timing6                           |

|   | 4.6    | Electrostatic discharge (ESD) characteristics      | 20 | 11 | wĸu   | JP/NMI timing specifications6                             |

| 5 | I/O P  | arameters                                          | 21 | 12 | Exter | rnal interrupt timing (IRQ pin)6                          |

|   | 5.1    | I/O pad DC electrical characteristics              | 21 | 13 | Temp  | perature sensor electrical characteristics6               |

|   | 5.2    | I/O pad AC specifications                          | 22 | 14 | Rada  | r module6                                                 |

|   | 5.3    | Aurora LVDS driver electrical characteristics      | 23 |    | 14.1  | MIPICSI2 D-PHY electrical and timing specifications6      |

|   | 5.4    | Reset pad electrical characteristics               | 24 |    | 14.2  | MIPICSI2 Disclaimer6                                      |

| 6 | Perip  | heral operating requirements and behaviours        | 26 | 15 | Ther  | mal Specifications7                                       |

|   | 6.1    | Clocks and PLL Specifications                      | 26 |    | 15.1  | Thermal characteristics                                   |

| 7 | Analo  | og modules                                         | 29 | 16 | Pack  | aging7                                                    |

|   | 7.1    | ADC electrical characteristics                     | 29 | 17 | Rese  | t sequence                                                |

|   | 7.2    | Sigma Delta ADC electrical characteristics         | 33 |    | 17.1  | Reset sequence duration                                   |

|   | 7.3    | DAC electrical specifications                      | 37 |    | 17.2  | Reset sequence description                                |

| 8 | Mem    | ory modules                                        | 38 | 18 | Powe  | er sequencing requirements7                               |

|   | 8.1    | Flash memory program and erase specifications      | 38 | 19 | Pinou | uts7                                                      |

|   | 8.2    | Flash memory Array Integrity and Margin Read       |    |    | 19.1  | Package pinouts and signal descriptions7                  |

|   |        | specifications                                     | 39 | 20 | Revis | sion History7                                             |

|   | 8.3    | Flash memory module life specifications            | 39 |    |       |                                                           |

## 1 Introduction

# 1.1 Family comparison

The following table provides a comparison of the devices: S32R274, S32R264, and MPC5775K. This information is intended to provide an understanding of the range of functionality offered by this family. For full details of all of the family derivatives please contact your marketing representative.

Table 1. S32R274 and S32R264 Family Comparison

| Feature                           | S32R274K                                                     | S32R274J                                | S32R264K                                | S32R264J                                | MPC5775K                                                             |

|-----------------------------------|--------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------------|

| CPUs                              |                                                              |                                         | e200z420 lock-step                      |                                         |                                                                      |

|                                   |                                                              |                                         | 2x e200z7260                            |                                         |                                                                      |

| SIMD                              |                                                              |                                         |                                         |                                         |                                                                      |

| Maximum<br>Operating<br>Frequency | 240 MHz (z7<br>cores) / 180 MHz<br>(z4)                      | 266 MHz (z7<br>cores) / 133 MHz<br>(z4) | 240 MHz (z7<br>cores) / 180 MHz<br>(z4) | 266 MHz (z7<br>cores) / 133 MHz<br>(z4) | 266 MHz (z7<br>cores) / 133 MHz<br>(z4)                              |

| Flash                             |                                                              | 2 MB w                                  | ith ECC                                 |                                         | 4 MB with ECC                                                        |

| EEPROM support                    |                                                              | 64 KB (e                                | mulation)                               |                                         | 96 KB (emulation)                                                    |

| RAM                               |                                                              |                                         | 1.5 MB with ECC                         |                                         | 1                                                                    |

| ECC                               |                                                              |                                         | end-to-end                              |                                         |                                                                      |

| MPU                               |                                                              | Core MPU: 24 entr                       | ies per core, System                    | MPU: 2x16 entries                       |                                                                      |

| eDMA                              |                                                              | safe eDM                                | A with 32 channels, 6                   | 64 triggers                             |                                                                      |

| Control ADC                       | 2x 12-bit SAR ADC, 1 MSps input mux for 16 external channels |                                         |                                         |                                         | 4x 12-bit SAR<br>ADC, 1 MSps, inpu<br>mux for 37 externa<br>channels |

| SD-ADC                            | 4 channels                                                   | s, 10 MSps                              | -                                       | _                                       | 8 channels, 10<br>MSps                                               |

| SPT                               |                                                              |                                         | 1x                                      |                                         | 1                                                                    |

| CTE                               |                                                              |                                         | 1x                                      |                                         |                                                                      |

| WGM                               |                                                              |                                         | 1x                                      |                                         |                                                                      |

| CTU                               |                                                              | 1                                       | х                                       |                                         | 2x                                                                   |

| SWT                               |                                                              |                                         | 3x                                      |                                         | 1                                                                    |

| STM                               |                                                              |                                         | 3x                                      |                                         |                                                                      |

| PIT                               |                                                              |                                         | 2x                                      |                                         |                                                                      |

| CRC                               |                                                              |                                         | 2x                                      |                                         |                                                                      |

| SEMA42                            |                                                              |                                         | 1x                                      |                                         |                                                                      |

| LINFlexD                          |                                                              | 1                                       | х                                       |                                         | 4x                                                                   |

| CAN                               |                                                              | 3x FlexCAN includ                       | ing 2x FlexCAN-FD                       |                                         | 4x FlexCAN + 1x<br>MCAN-FD                                           |

Table continues on the next page...

Table 1. S32R274 and S32R264 Family Comparison (continued)

| Feature                | S32R274K            | S32R274J                                              | S32R264K              | S32R264J           | MPC5775K                          |  |  |

|------------------------|---------------------|-------------------------------------------------------|-----------------------|--------------------|-----------------------------------|--|--|

| SPI                    | 2x                  |                                                       |                       |                    | 4x                                |  |  |

| I <sup>2</sup> C       |                     | 2                                                     | 2x                    |                    | 3x                                |  |  |

| Zipwire                |                     | 1x                                                    | LFAST+SIPI, 320 M     | Hz                 |                                   |  |  |

| FlexRay                |                     | 1x dual channel                                       |                       |                    |                                   |  |  |

| Ethernet               | 10/100              | 10/100 and >100 Mbps, RMII/MII/RGMII I/F, AVB support |                       |                    |                                   |  |  |

| FlexPWM                | 1x, 12 PWM channels |                                                       |                       |                    | 2x, 12 PWM<br>channels each       |  |  |

| eTimer                 |                     | 2x, 6 char                                            | nnels each            |                    | 3x, 6 channels<br>each            |  |  |

| External ADC interface |                     | 1x 4 lanes MIPICS                                     | I2 Rx, 1 Gbps/lane    |                    | 1x PDI (16-bit data, clock, sync) |  |  |

| IRCOSC                 |                     |                                                       | 16 MHz                |                    | •                                 |  |  |

| XOSC                   |                     |                                                       | 40 MHz                |                    |                                   |  |  |

| FMPLL                  |                     | dual sy                                               | stem PLL, 1x FM mo    | dulated            |                                   |  |  |

| DAC                    | 1x 12-bit           | 10 MSps                                               | _1                    | _1                 | 1x 12-bit 2 MSps                  |  |  |

| SIUL2                  |                     |                                                       | 1x                    |                    |                                   |  |  |

| BAM                    |                     |                                                       | 1x                    |                    |                                   |  |  |

| INTC                   |                     |                                                       | 1x                    |                    |                                   |  |  |

| SSCM                   |                     |                                                       | 1x                    |                    |                                   |  |  |

| FCCU/FOSU              |                     |                                                       | 1x                    |                    |                                   |  |  |

| MEMU                   |                     |                                                       | 1x                    |                    |                                   |  |  |

| STCU2                  |                     |                                                       | 1x                    |                    |                                   |  |  |

| CSE                    |                     | 1                                                     | х                     |                    | -                                 |  |  |

| PASS/TDM               |                     | 1                                                     | х                     |                    | -                                 |  |  |

| MC_ME                  |                     |                                                       | 1x                    |                    | •                                 |  |  |

| MC_CGM                 |                     |                                                       | 1x                    |                    |                                   |  |  |

| MC_RGM                 |                     |                                                       | 1x                    |                    |                                   |  |  |

| TSENS                  |                     |                                                       | 2x                    |                    |                                   |  |  |

| Debug                  |                     | JTAGC, JTAGM, C                                       | CJTAG, with class3+ I | Nexus, Aurora only |                                   |  |  |

| Safety level           |                     | ISO262                                                | 262 SEooC ASIL-B to   | ASIL-D             |                                   |  |  |

| Temp. range (Tj)       |                     |                                                       | -40 to 150°C          |                    |                                   |  |  |

<sup>1.</sup> DAC is not supported in S32R264x devices. Hence, ignore its occurrences in this document for S32R264K and S32R264J.

### 1.2 Feature list

On-chip modules available within the device include the following features:

• Safety core: Power Architecture® e200Z4 32-bit CPU with checker core

#### Introduction

- 2 cycle delayed lockstep

- Harvard architecture with 64-bit bus for data and instructions

- Dual issue: up to two instructions per clock cycle

- 8 KB instruction cache and 4 KB data cache

- 64 KB data local memory

- with background load/store: backdoor access

- 0-wait state for all read and 32/64-bit write accesses

- Low number of wait states for backdoor accesses

- Support for decorated storage

- Variable Length Encoding (VLE) compliant for higher code density

- Single precision floating point operations

- Computation cores: Power Architecture® e200Z7 32-bit CPU

- Dual issue: up to two instructions per clock cycle

- Harvard architecture with 64-bit bus for data instructions

- 16 KB instruction cache and 16 KB data cache

- 64 KB data local memory

- with background load/store: backdoor access

- 0-wait state for all read and 32/64-bit write accesses

- Low number of wait states for backdoor accesses

- Support for decorated storage

- Using variable length encoding (VLE) for higher code density

- 4-way integer processing unit (SPE2)

- 2-way single-precision Floating Point Unit (EFPU2)

- 2 MB on-chip code flash (FMC flash) with ECC

- Three ports (one per CPU) shared between code and data flash with  $4 \times 256$  bit buffer for code and data flash including prefetch functions

- Data flash is part of the code flash module

- Including 64 KB EEPROM emulation

- 1.5 MB on-chip SRAM with ECC

- Decorated memory controller to support atomic read-modify-write operations

- Single- and double-bit error visibility is supported

- Up to four ports (one per CPU and SPT) and up to 8 banks allow simultaneous accesses from different masters to different banks

- RADAR processing

- Signal Processing Toolbox (SPT) for RADAR signal processing acceleration

- Cross Timing Engine (CTE) for precise timing generation and triggering

- Waveform generation module (WGM) for chirp ramp generation

- 4x 12-bit  $\Sigma\Delta$ -ADC with 10 MSps (not supported on S32R264 devices)

- One DAC with 10 MSps (not supported on S32R264 devices)

- MIPICSI2 interface to connect external ADCs

- Four data lanes, with up to 1 Gbps per lane and in total

- One clock lane

- Memory Protection

- Each core memory protection unit provides 24 entries

- Data and instruction bus system memory protection Unit (SMPU) with 16 region descriptors each

- Register protection

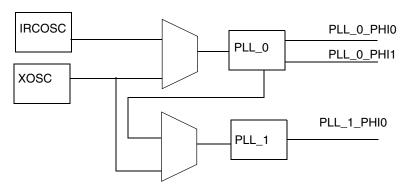

- Clock Generation

- 40 MHz external crystal (XOSC)

- 16 MHz Internal oscillator (IRCOSC)

- Dual system PLL with one frequency modulated phase-locked loop (FMPLL)

- Low-jitter PLL to  $\Sigma\Delta$ -ADC and DAC clock generation

- Functional Safety

- Enables up to ASIL-D applications

- End to end ECC ensuring full protection of all data accesses throughout the system, from each of the systems masters through the crossbar and into the memories and peripherals

- FCCU for fault collection and fault handling

- MEMU for memory error management

- Safe eDMA controller

- User selectable Memory BIST (MBIST) can be enabled to run out of various reset conditions or during runtime

- Self-Test Control Unit (STCU2)

- Error Injection Module (EIM)

- On-chip voltage monitoring

- Clock Monitor Unit (CMU) to support monitoring of critical clocks

- Security

- Cryptographic Security Engine (CSE2) enabling advanced security management

- Supports censorship and life-cycle management via Password and Device Security (PASS) module

- Diary control for tamper detection (TDM)

- Support Modules

- Global Interrupt controller (INTC) capable of routing interrupts to any CPU

- Semaphore unit to manage access to shared resources

- Two CRC computation units with four polynomials

- 32-channel eDMA controller with multiple transfer request sources using DMAMUX

- Boot Assist Module (BAM) supports internal flash programming via a serial link (LIN / CAN)

- Timers

- Two Periodic Interval Timers (PIT) with 32-bit counter resolution

#### Introduction

- Three System Timer Module (STM)

- Three Software Watchdog Timers (SWT)

- Two eTimer modules with 6 channels each

- One FlexPWM module for 12 PWM signals

- Communication Interfaces

- Two Serial Peripheral interface (SPI) module

- Two inter-IC communication interface (I2C) modules

- One LINFlexD module

- One dual-channel FlexRay module with 128 message buffers

- Three FlexCAN modules with configurable buffers

- CAN FD optionally supported on 2 FlexCAN modules

- One ENET MAC supporting MII/RMII/RGMII interface

- Supports 10/100 Mbps (MII/RMII/RGMII) and >100 Mbps (RGMII)

- Supports IEEE1588 timestamps and PTP

- Zipwire high-speed serial communication

- Supports LFAST and SIPI protocol

- Fast interprocessor communication with 320 Mbps gross data rate

- DMA based access to memory resources

- Debug Functionality

- 4-pin JTAG interface and Nexus/Aurora interface for serial high-speed tracing

- e200Z7 core and e200Z4 core: Nexus development interface (NDI) per IEEE-ISTO 5001-2012 Class 3+

- All platform bus masters except CSE can be monitored via Nexus/Aurora

- Device/board boundary Scan testing supported with per Joint Test Action Group (JTAG) (IEEE 1149.1) and 1149.7 (cJTAG)

- On-chip control for Nexus development interface by JTAGM module

- Two analog-to-digital converters (SAR ADC)

- Each ADC supports up to 16 input channels

- Cross Trigger Unit to enable synchronization of ADC conversions with eTimer

- On-chip voltage DC/DC regulator for core clock (VREG)

- Two Temperature Sensors (TSENS)

S32R264 feature changes with respect to S32R274 are as follows:

- SD-ADC's removed

- DAC removed

- SDPLL replaced with AFEPLL

- Improved radiated emissions in the GLONASS band. Full EMC reports are available from NXP on request for both S32R264, and S32R274 to allow the customer to select the most suitable part for their usecase.

#### PIT\_1 SWT\_1 SDADC MIPICSI2 DMA SRAM VLE FFT/ VLE Sequence Core MPU 24 Entries e2eECC DAC CSF SD VREGS Instr. Crossbar Switch (AMBA 2.0 v6 AHB) 64- bit Data Crossbar Switch (AMBA 2.0 v6 AHB) 64 bit SDPLL System memory Protection Unit SMPU\_0 System memory Protection Unit SMPU\_1 IRCOSC TSENS 0/1 VREG LVD Triple Ported Quad Ported SRAM Controller AIPS-Lite 1 AIPS-Lite\_0 (PFLASH) e2eECC e2eECC 2 MB Flash memory up to 64 KB DFlash 1.5 MB SRAM 8 Banks

# 1.3 Block diagram

Figure 1. S32R274 block diagram

#### NOTE

S32R264 devices support AFE PLL while S32R274 devices support SDPLL.

# 2 Ordering parts

# 2.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to www.nxp.com and perform a part number search for the device number.

S32R274/S32R264 Series Data Sheet, Rev. 5, 04/2019

## 3 Part identification

# 3.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

### 3.2 Fields

This section lists the possible values for each field in the part number (not all combinations are valid):

**Table 2. Configuration**

| 257MAPBGA       | Configuration | Performance | Temperature |

|-----------------|---------------|-------------|-------------|

| FS32R274KSK2MMM | S             | K           | М           |

| FS32R274KCK2MMM | С             | K           | М           |

| FS32R274VBK2MMM | В             | V           | М           |

| FS32R274VCK2MMM | С             | V           | М           |

| FS32R274KSK2VMM | S             | K           | V           |

| FS32R274KCK2VMM | С             | K           | V           |

| FS32R274VBK2VMM | В             | V           | V           |

| FS32R274VCK2VMM | С             | V           | V           |

| FS32R274JSK2MMM | S             | J           | M           |

| FS32R264KBK0MMM | В             | K           | М           |

| FS32R264KCK0MMM | С             | K           | М           |

| FS32R264JBK0MMM | В             | J           | М           |

| FS32R264JCK0MMM | С             | J           | М           |

**Table 3. Configuration**

| Configuration | 2 MB Flash | 1.5 MB RAM | CSE |

|---------------|------------|------------|-----|

| B or S        | Yes        | Yes        | Yes |

| С             | Yes        | Yes        | No  |

Table 4. Performance

| Perf (MHz) | <b>Z</b> 7 | Z7  | Z4  | Z4  |

|------------|------------|-----|-----|-----|

| K          | 240        | 240 | 120 | 120 |

Table continues on the next page...

10 NXP Semiconductors

#### S32R274/S32R264 Series Data Sheet, Rev. 5, 04/2019

**Table 4. Performance (continued)**

| Perf (MHz) | <b>Z</b> 7 | <b>Z</b> 7 | Z4  | Z4  |

|------------|------------|------------|-----|-----|

| V          | 200        | 200        | 100 | 100 |

| J          | 266        | 266        | 133 | 133 |

**Table 5. Temperature values**

| Temperature | T <sub>A</sub>   |

|-------------|------------------|

| M           | -40 °C to 125 °C |

| V           | -40 °C to 105 °C |

### 4 General

# 4.1 Absolute maximum ratings

#### NOTE

Functional operating conditions appear in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maximum values is not guaranteed.

Stress beyond the listed maximum values may affect device reliability or cause permanent damage to the device.

Table 6. Absolute maximum ratings

| Symbol                    | Parameter                                                                             | Conditions | Min  | Max                  | Unit |

|---------------------------|---------------------------------------------------------------------------------------|------------|------|----------------------|------|

| V <sub>DD_HV_PMU</sub>    | 3.3 V PMU supply voltage                                                              | _          | -0.3 | 4.0 <sup>1, 2</sup>  | V    |

| V <sub>DD_HV_REG3V8</sub> | REG3V8 Supply Voltage                                                                 | _          | -0.3 | 5.5                  | V    |

| V <sub>DD_HV_IO*</sub>    | 3.3 V Input/Output Supply Voltage, LFAST IO Supply, RGMII IO Supply and PWM IO Supply | _          | -0.3 | 3.63 <sup>1, 2</sup> | V    |

| V <sub>SS_HV_IOx</sub>    | Input/output ground voltage                                                           |            | -0.1 | 0.1                  | V    |

| V <sub>DD_HV_FLA</sub>    | 3.3 V flash supply voltage                                                            | _          | -0.3 | 3.63 <sup>1, 2</sup> | V    |

| $V_{DD\_HV\_RAW}$         | AFE RAW supply voltage                                                                | _          | -0.1 | 4                    | V    |

| $V_{DD\_HV\_DAC}$         | AFE DAC supply voltage                                                                |            | -0.1 | 4                    | V    |

| $V_{DD\_LV\_IO^*}$        | Aurora supply voltage                                                                 | _          | -0.3 | 1.5                  | V    |

| $V_{DD}$                  | 1.25 V core supply voltage <sup>3, 4, 5</sup>                                         | _          | -0.3 | 1.5                  | V    |

| V <sub>SS</sub>           | 1.25 V core supply ground <sup>3, 4, 5</sup>                                          | _          | -0.3 | 0.3                  | V    |

| V <sub>SS_LV_OSC</sub>    | Oscillator amplifier ground                                                           | _          | -0.1 | 0.1                  | V    |

Table continues on the next page...

#### General

Table 6. Absolute maximum ratings (continued)

| Symbol                       | Parameter                                                                          | Conditions                         | Min         | Max                          | Unit        |

|------------------------------|------------------------------------------------------------------------------------|------------------------------------|-------------|------------------------------|-------------|

| V <sub>DD_LV_PLL0</sub>      | System PLL supply voltage                                                          | _                                  | -0.3        | 1.5                          | V           |

| V <sub>DD_LV_LFASTPLL</sub>  | LFAST PLL supply voltage                                                           | _                                  | -0.3        | 1.5                          | ٧           |

| V <sub>DD_HV_ADCREF0/1</sub> | ADC_0 and ADC_1 high reference voltage                                             | _                                  | -0.3        | 5.5                          | ٧           |

| V <sub>SS_HV_ADCREF0/1</sub> | ADC_0 and ADC_1 ground and low reference voltage                                   | _                                  | -0.1        | 0.1                          | ٧           |

| V <sub>DD_HV_ADC</sub>       | 3.3 V ADC supply voltage                                                           | _                                  | -0.3        | 4.0 1, 2                     | ٧           |

| V <sub>SS_HV_ADC</sub>       | 3.3 V ADC supply ground                                                            | _                                  | -0.1        | 0.1                          | ٧           |

| TV <sub>DD</sub>             | Supply ramp rate <sup>6</sup>                                                      | _                                  | 0.00005     | 0.1                          | V/µs        |

| V <sub>IN_XOSC</sub>         | Voltage on XOSC pins with respect to ground                                        | _                                  | -0.3        | 1.47                         | ٧           |

| V <sub>INA</sub>             | Voltage on SAR ADC analog pin with respect to ground (V <sub>SS_HV_ADCREFx</sub> ) | _                                  | -0.3        | 6.0                          | V           |

| V <sub>INA_SD</sub>          | Voltage on Sigma-Delta ADC analog pin with respect to ground <sup>7</sup>          | Powered up <sup>8</sup>            | -0.3        | V <sub>DD_HV_RAW</sub> + 0.3 | <b>&gt;</b> |

|                              |                                                                                    | Powered down                       | -0.3        | 1.47                         |             |

| V <sub>IN</sub>              | Voltage on any digital pin with respect to ground (V <sub>SS_HV_IOx</sub> )        | Relative to V <sub>DD_HV_IOx</sub> | -0.3        | $V_{DD\_HV\_IOx} + 0.3$      | V           |

| V <sub>DD_LV_DPHY</sub>      | MIPICSI2 DPHY voltage supply <sup>3, 4, 5</sup>                                    | _                                  | -0.3        | 1.5                          | ٧           |

| V <sub>SS_LV_DPHY</sub>      | MIPICSI2 DPHY supply ground <sup>3, 4, 5</sup>                                     | _                                  | -0.3        | 0.3                          | ٧           |

| I <sub>INJPAD</sub>          | Injected input current on any pin during overload condition <sup>11</sup>          | _                                  | -10         | 10 <sup>12</sup>             | mA          |

| I <sub>INJSUM</sub>          | Absolute sum of all injected input currents during overload condition              | _                                  | <b>–</b> 50 | 50                           | mA          |

| T <sub>STG</sub>             | Storage temperature                                                                | _                                  | <b>–</b> 55 | 150                          | ŷ           |

- 1. 5.3 V for 10 hours cumulative over lifetime of device; 3.3 V +10% for time remaining.

- 2. Voltage overshoots during a high-to-low or low-to-high transition must not exceed 10 seconds per instance.

- 3. 1.45 V to 1.5 V allowed for 60 seconds cumulative time at maximum T<sub>J</sub> = 150°C; remaining time as defined in note 5 and

- 4. 1.375 V to 1.45 V allowed for 10 hours cumulative time at maximum T<sub>,I</sub> = 150°C; remaining time as defined in note 6.

- 5. 1.32 V to 1.375 V range allowed periodically for supply with sinusoidal shape and average supply value below 1.275 V at maximum T<sub>J</sub>=150°C.

- 6. TV<sub>DD</sub> is relevant for all external supplies.

- 7. ADC inputs include an overvoltage detect function that detects any voltage higher than 1.2 V with respect to ground on either ADC input and open circuit (disconnect) the input in order to prevent damage to the ADC internal circuitry. The ADC input remains disconnected until the inputs return to the normal operating range.

- 8. SDADC is powered up and overvoltage protection is ON.

- 9. SDADC is powered up and overvoltage protection is OFF.

- 10. Only when  $V_{DD\ HV\ IOx}$  < 3.63 V.

- 11. No input current injection circuitry on AFE pins.

- 12. The maximum value of 10 mA applies to pulse injection only. DC current injection is limited to a maximum of 5 mA.

# 4.2 Operating conditions

The following table describes the operating conditions for the device, and for which all specifications in the datasheet are valid, except where explicitly noted. The device operating conditions must not be exceeded, or the functionality of the device is not guaranteed.

Table 7. Device operating conditions

| Symbol                        | Parameter                                                                                     | Conditions   | Min               | Тур  | Max <sup>1</sup>               | Unit   |

|-------------------------------|-----------------------------------------------------------------------------------------------|--------------|-------------------|------|--------------------------------|--------|

| V <sub>DD_HV_PMU</sub>        | 3.3V PMU Supply Voltage                                                                       | _            | 3.13 <sup>2</sup> | 3.3  | 3.6                            | V      |

| V <sub>DD_HV_REG3V8</sub>     | REG3V8 Supply Voltage                                                                         | _            | 3.13              | 3.8  | 5.5                            | V      |

| $V_{DD}$                      | Core Supply Voltage                                                                           | <del>_</del> | 1.19 <sup>2</sup> | 1.25 | 1.31 <sup>3</sup>              | V      |

| V <sub>DD_HV_IO*</sub>        | Main GPIO 3V Supply<br>Voltage, LFAST IO Supply,<br>RGMII IO Supply, PWM IO<br>Supply Voltage | _            | 3.13 <sup>2</sup> | 3.3  | 3.6                            | V      |

| V <sub>DD_LV_IO_*</sub> 4     | Aurora Supply Voltage                                                                         | _            | 1.19              | 1.25 | 1.31                           | V      |

| V <sub>DD_LV_PLL0</sub>       | System PLL Supply Voltage                                                                     | _            | 1.19 <sup>2</sup> |      | 1.31                           | V      |

| V <sub>DD_LV_LFASTPLL</sub>   | LFAST PLL Supply Voltage                                                                      | _            | 1.19              | T —  | 1.31                           | V      |

| V <sub>DD_HV_FLA</sub> 5      | Flash Supply Voltage                                                                          | _            | 3.13 <sup>2</sup> | 3.3  | 3.6                            | V      |

| V <sub>DD_HV_ADC</sub>        | SAR ADC Supply Voltage<br>(HVD supervised)                                                    | _            | 3.13 <sup>2</sup> | 3.3  | 3.66                           | V      |

| $V_{DD\_HV\_RAW}$             | 3.3V AFE RAW Supply<br>Voltage                                                                | _            | 3.13              | 3.3  | 3.6                            | V      |

| V <sub>DD_HV_DAC</sub>        | 3.3V AFE DAC Supply<br>Voltage                                                                | _            | 3.13              | 3.3  | 3.6                            | V      |

| V <sub>DD_HV_ADCREF0/1</sub>  | ADC_0 and ADC_1 high reference voltage                                                        | _            | 3.13              | 3.3  | 3.6                            | V      |

| V <sub>IN</sub>               | Voltage on digital pin with respect to ground (V <sub>SS_HV_IOx</sub> )                       | _            | _                 | _    | V <sub>DD_HV_IOx</sub><br>+0.3 | V      |

| $V_{INSDPP}$                  | Sigma-Delta ADC Input<br>Voltage (peak-peak) <sup>7, 8</sup>                                  | Differential | _                 | _    | 1.2                            | V      |

| V <sub>INSR</sub>             | Sigma-Delta ADC Input Slew Rate <sup>7</sup>                                                  | _            | _                 | _    | 165                            | V/µs   |

| R <sub>TRIM_TOL</sub>         | External Trim Resistor tolerance                                                              | ±0.1%        | 40.16             | 40.2 | 40.25                          | kΩ     |

| R <sub>TRIM_TEMPCO</sub>      | External Trim Resistor<br>Temperature Coefficient                                             | _            | _                 | _    | 25                             | ppm/°C |

| V <sub>INA</sub> <sup>9</sup> | Voltage on SAR ADC analog pin with respect to ground (V <sub>SS_HV_ADCREFx</sub> )            | _            | _                 | _    | V <sub>DD_HV_ADCRE</sub>       | V      |

| $V_{DD\_LV\_DPHY}$            | MIPICSI2 DPHY voltage supply <sup>10</sup>                                                    |              | 1.19              | 1.25 | 1.31                           | V      |

| T <sub>A</sub> , 11           | Ambient temperature at full performance 12                                                    | _            | -40               | _    | 125                            | °C     |

Table continues on the next page...

Table 7. Device operating conditions (continued)

| Symbol                          | Parameter                                        | Conditions         | Min                | Тур  | Max <sup>1</sup>  | Unit |

|---------------------------------|--------------------------------------------------|--------------------|--------------------|------|-------------------|------|

| T <sub>J</sub> <sup>11</sup>    | Junction temperature                             | _                  | -40                | _    | 150               | °C   |

| F <sub>XTAL</sub>               | XOSC Crystal Frequency <sup>13</sup>             | _                  | _                  | 40   | _                 | MHz  |

|                                 | AF                                               | E Bypass Modes O   | nly                |      |                   | •    |

|                                 | Single                                           | e-Ended External C | lock <sup>14</sup> |      |                   |      |

| EXTAL <sub>clk</sub>            | EXTAL external clock frequency                   |                    |                    | 40   |                   | MHz  |

| $V_{inxoscjit}$                 | EXTAL external clock Cycle to Cycle Jitter (RMS) | _                  | _                  |      | 2.5 <sup>15</sup> | ps   |

| V <sub>inxoscclkvil</sub>       | EXTAL external clock input low voltage           | _                  | 0                  |      | 0.4               | V    |

| V <sub>inxoscclkvih</sub>       | EXTAL external clock input high voltage          | _                  | 1                  |      | 1.23              | V    |

| t <sub>r</sub> /t <sub>f</sub>  | Rise/fall time of EXTAL external clock input     |                    |                    |      | 1                 | ns   |

| t <sub>dc</sub>                 | Duty Cycle of EXTAL external clock input         |                    | 47                 | 50   | 53                | %    |

|                                 | Differe                                          | ntial LVDS Externa | Clock              |      |                   | -1   |

| LVDS <sub>clk</sub>             | LVDS external clock frequency                    |                    |                    | 40   |                   | MHz  |

| LVDSV <sub>inxoscclk</sub>      | LVDS external clock input voltage                |                    | 0                  |      | 1.36              | V    |

| LVDSV <sub>inxoscclk(p-p)</sub> | LVDS external clock input                        | Voltage driven,    | 0.45               | 0.70 | 1.12              | V    |

|                                 | voltage (peak-peak)                              | AC coupled         |                    |      |                   |      |

|                                 |                                                  | Differential       |                    |      |                   |      |

| LVDSI <sub>inxoscclk</sub>      | LVDS external clock input                        | Current driven,    | 3.0                | 3.5  | 4.0               | mA   |

|                                 | current                                          | DC coupled.        |                    |      |                   |      |

| LVDSV <sub>inxoscjit</sub>      | LVDS external clock Jitter (RMS) <sup>15</sup>   |                    |                    |      | 2.5               | ps   |

| t <sub>r</sub> /t <sub>f</sub>  | Rise/fall time of LVDS external clock input      | 20% - 80%          |                    |      | 1.5               | ns   |

| t <sub>dcLVDS</sub>             | Duty Cycle of LVDS external clock input          |                    | 47                 | 50   | 53                | %    |

- 1. Full functionality cannot be guaranteed when voltages are out of the recommended operating conditions.

- 2. Min voltage takes into account the LVD variation.

- 3. Max voltage takes into account HVD variation.

- 4. Aurora supply must connect to core supply voltage at board level.

- 5. The ground connection for the  $V_{DD\ HV\ FLA}$  is shared with  $V_{SS}$ .

- 6. Supply range does not take into account HVD levels. Full range can be achieved after power-up, if HVD is disabled. See Voltage regulator electrical characteristics section for details.

- 7. Around common mode voltage of 0.7 V. Input voltage cannot exceed 1.4 V prior to AFE start-up completion (VREF and VREGs on and LVDs cleared).

- 8. SDADC input voltage full scale is 1.2 Vpp

- On channels shared between ADC0 and 1, V<sub>DD\_HV\_ADCREFx</sub> is the lower of V<sub>DD\_HV\_ADCREF0/1</sub>.

- 10. V<sub>DD\_LV\_DPHY</sub> supply should be shorted to core supply voltage VDD on board. Refer to AN5251. Contact your NXP sales representative for details.

15

- 11. While determining if the operating temperature specifications are met, either the ambient temperature or junction temperature specification can be used. It is critical that the junction temperature specification is not exceeded under any condition.

- 12. Full performance means full frequency.

- 13. Recommended Crystal 40 MHz (ESR≤30 Ω), 8 pF load capacitance.

- 14. External mode can be used as differential input with EXTAL and XTAL

- 15. The number is 3.5 ps when SD-ADC and/or DAC is not used in the device.

# 4.3 Supply current characteristics

Current consumption data is given in the following table. These specifications are design targets and are subject to change per device characterization.

Table 8. Current consumption characteristics

| Symbol                    | Parameter                                      | Conditions                                                                           | Min | Тур             | Max                                    | Unit |

|---------------------------|------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----------------|----------------------------------------|------|

| I <sub>DD_CORE</sub>      | Core current in run mode                       | All cores at max frequency. 1.31 V. Tj = 150°C (240 MHz)                             | -   | -               | 1480 <sup>1</sup><br>1642 <sup>1</sup> | mA   |

|                           |                                                | All cores at max frequency. 1.31 V. Tj = 150°C (266 MHz)                             |     |                 |                                        |      |

| I <sub>DD_HV_FLA</sub>    | Flash operating current                        | Tj = 150°C. V <sub>DD_HV_FLA</sub> = 3.6 V                                           | -   | 3 <sup>2</sup>  | 40 <sup>3</sup>                        | mA   |

| I <sub>DD_LV_AURORA</sub> | Aurora operating current                       | Tj = 150°C. V <sub>DD_LV_AURORA</sub> = 1.31 V. 4 TX lanes enabled.                  | -   | -               | 60                                     | mA   |

| I <sub>DD_HV_ADC</sub>    | ADC operating current                          | Tj = $150$ °C. $V_{DD\_HV\_ADC}$ = 3.6 V. 2 ADCs operating at 80 MHz.                | -   | 2               | 5                                      | mA   |

| I <sub>DD_HV_ADCREF</sub> | Reference current per                          | Tj = 150°C. V <sub>DD_HV_ADCREFx</sub> = 3.6 V. ADC operating                        | -   | -               | 1.5                                    | mA   |

|                           | ADC <sup>4</sup>                               | at 80 MHz.                                                                           | -   | -               | 0.75                                   |      |

|                           | Reference current per temp sensor <sup>5</sup> |                                                                                      |     |                 |                                        |      |

| I <sub>DD_HV_RAW</sub>    | AFE SD and regulator operating current         | Tj = 150°C. V <sub>DD_HV_RAW</sub> = 3.6 V. SD-PLL, AFE regulators and 4 SD enabled. | -   | 70 <sup>6</sup> | 75                                     | mA   |

| I <sub>DD_HV_DAC</sub>    | AFE DAC operating current                      | Tj = 150°C. $V_{DD\_HV\_DAC}$ = 3.6 V. DAC enabled.                                  | -   | 10              | 15                                     | mA   |

| I <sub>DD_HV_PMU</sub>    | PMU operating current                          | Tj = 150°C. VDD_HV_PMU = 3.6 V. Internal regulation enabled.                         | -   | 2               | 10                                     | mA   |

| I <sub>DD_LV_DPHY</sub>   | MIPICSI2 DPHY operating current in HS-RX mode  | Tj = 150°C, V <sub>DD_LV_DPHY</sub> =1.31 V                                          | •   | 14.9            | 23.2                                   | mA   |

- 1. Strong dependence on use case, cache usage.

- 2. Measured during flash read.

- 3. Peak Flash current measured during read while write (RWW) operation.

- 4. ADC0 and 1 on ADCREF0/1.

- 5. Temp sensor current when PMC\_CTL\_TD[TSx\_AOUT\_EN] = 1. TS0 on ADCREF0/1.

- 6. Typical number is approximately 10 mA per each SD-ADC enabled, 12 mA for SD-PLL and 15 mA for the AFE regulators.

S32R274/S32R264 Series Data Sheet, Rev. 5, 04/2019

# 4.4 Voltage regulator electrical characteristics

Table 9. Voltage regulator electrical specifications

| Symbol               | Parameter                                                     | Conditions                          | Min   | Тур   | Max   | Unit |

|----------------------|---------------------------------------------------------------|-------------------------------------|-------|-------|-------|------|

| POR-R                | 1.25 V VDD core POR release                                   | _                                   | 0.97  | 1.02  | 1.06  | ٧    |

| POR-E                | 1.25 V VDD core POR engage                                    | _                                   | 0.93  | 0.98  | 1.02  | V    |

| LVD12R               | Low-Voltage Detection 1.25 V release (Core                    | Untrimmed                           | 1.122 | 1.157 | 1.192 | V    |

| LVD12R-trim          | VDD supply, and PLL0/1 supply LVDs)                           | Trimmed                             | 1.142 | 1.157 | 1.172 | V    |

| LVD12E               | Low-Voltage Detection 1.25 V engage (Core                     | Untrimmed                           | 1.102 | 1.137 | 1.172 | V    |

| LVD12E-trim          | VDD supply and PLL0/1 supply LVDs)                            | Trimmed                             | 1.122 | 1.137 | 1.152 | V    |

| HVD12R-trim          | High-Voltage Detection 1.25 V release (Core VDD)              | Trimmed                             | 1.33  | 1.35  | 1.37  | V    |

| HVD12E-trim          | High-Voltage Detection 1.25 V engage (Core VDD supply)        | Trimmed                             | 1.36  | 1.38  | 1.40  | ٧    |

| LVD_MIPI12R-trim     | Low-Voltage Detection 1.25V release<br>(MIPICSI2 DPHY supply) | _                                   | 1.130 | 1.157 | 1.184 | ٧    |

| LVD_MIPI12E-trim     | Low-Voltage Detection 1.25V engage (MIPICSI2 DPHY supply)     | _                                   | 1.111 | 1.137 | 1.163 | V    |

| POR-R-<br>VDD_HV_PMU | 3.3 V PMU supply voltage POR release threshold                | _                                   | 2.54  | 2.645 | 2.735 | V    |

| POR-E-<br>VDD_HV_PMU | 3.3 V PMU supply voltage POR engage threshold                 | _                                   | 2.50  | 2.60  | 2.695 | V    |

| LVD33R               | 3.3V Low-Voltage Detection Release                            | Untrimmed                           | 2.90  | 3.02  | 3.13  | V    |

| LVD33R-trim          | Threshold (PMC, FLASH, IO, ADC)                               | Trimmed                             | 3.00  | 3.05  | 3.10  | V    |

| LVD33E               | 3.3V Low-Voltage Detection Engage                             | Untrimmed                           | 2.86  | 2.98  | 3.09  | V    |

| LVD33E-trim          | Threshold (PMC, FLASH, IO, ADC)                               | Trimmed                             | 2.96  | 3.01  | 3.06  | V    |

| HVD33R               | 3.3V High-Voltage Detection Release                           | Untrimmed                           | 3.45  | 3.61  | 3.75  | V    |

| HVD33R-trim          | Threshold (ADC)                                               | Trimmed                             | 3.47  | 3.53  | 3.58  | V    |

| HVD33E               | 3.3V High-Voltage Detection Engage                            | Untrimmed                           | 3.51  | 3.65  | 3.79  | V    |

| HVD33E-trim          | Threshold (ADC)                                               | Trimmed                             | 3.51  | 3.57  | 3.62  | V    |

| UVL30R               | SMPS under-voltage lockout release threshold                  | Untrimmed                           | 2.75  | 2.90  | 3.05  | V    |

| UVL25E               | SMPS under-voltage lockout engage threshold                   |                                     | 2.40  | 2.55  | 2.7   | V    |

| DGLITCHE             | Voltage Detector Deglitcher Filter Time -<br>Engage           | _                                   | 2.0   | 3.5   | 5     | μs   |

| DGLITCHR             | Voltage Detector Deglitcher Filter Time -<br>Release          | _                                   | 5     | 7     | 12    | μs   |

| RSTDGLTC             | VREG_POR_B Input Deglitch Filter Time                         | _                                   | 200   | 320   | 500   | ns   |

| RSTPUP               | VREG_POR_B Pin Pull-up Resistance                             | _                                   | 37    | 75    | 150   | kΩ   |

| REGENPUP             | VREG_SEL Pin Pull-up Resistance                               | _                                   | 37    | 75    | 150   | kΩ   |

| VSMPS                | Internal switched regulator output voltage 1                  | Load Current from 10<br>mA to 1.8 A | 1.19  | 1.255 | 1.35  | V    |

Table continues on the next page...

Table 9. Voltage regulator electrical specifications (continued)

| Symbol           | Parameter                                                                   | Conditions | Min                     | Тур  | Max                     | Unit |

|------------------|-----------------------------------------------------------------------------|------------|-------------------------|------|-------------------------|------|

| FSMPS            | Internal switched regulator operating                                       | Untrimmed  | 0.65                    | 1.00 | 1.35                    | MHz  |

|                  | frequency without modulation                                                | Trimmed    | 0.93                    | 1.00 | 1.07                    | MHz  |

| FSMPS-M7.5       | Internal switched regulator frequency                                       | _          | _                       | 7.5  | _                       | %    |

| FSMPS-M15        | modulation                                                                  | _          | _                       | 15   | _                       | %    |

| FSMPS-M30        |                                                                             | _          | _                       | 30   |                         | %    |

| VREGSWPUP        | Internal switched regulator gate-driver pull-<br>up resistance <sup>2</sup> | _          | _                       | _    | _                       | _    |

| VREF_BG_T        | PMC bandgap reference voltage for SARADC                                    | Trimmed    | 1.20                    | 1.22 | 1.237                   | V    |

| Vih (VREG_POR_B) | VREG_POR_B pin High Voltage level                                           | _          | 0.7 x<br>VDD_H<br>V_PMU | _    | VDD_H<br>V_PMU<br>+ 0.3 | V    |

| Vil (VREG_POR_B) | VREG_POR_B pin Low Voltage level                                            | _          | -0.3                    | _    | 0.3 x<br>VDD_H<br>V_PMU | V    |

| LVDAFER          | Low Voltage Detection 3.3V Release (AFE VDD_HV_DAC and VDD_HV_RAW supplies) |            | 2.75                    | 2.80 | 2.90                    | V    |

| LVDAFEE          | Low Voltage Detection 3.3V Engage (AFE VDD_HV_DAC and VDD_HV_RAW supplies)  |            | 2.68                    | 2.77 | 2.86                    | V    |

<sup>1.</sup> Min/Max includes transient load conditions. Steady state voltage is within the core supply operating specifications.

<sup>2.</sup> There is a strong pull up from VREG\_SWP to VDD\_HV\_REG3V8 which is connected when SMPS is disabled. The pullup has resistance less than 1 Kohm, therefore VREG\_SWP should not be connected to ground if unused.

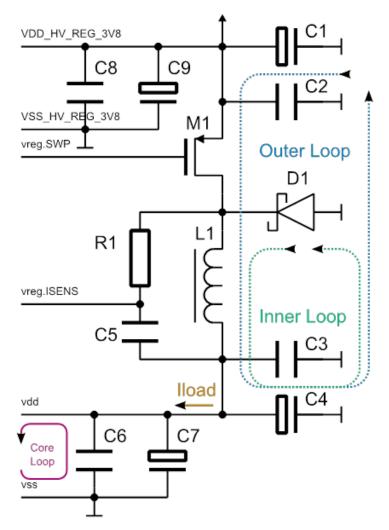

Figure 2. SMPS External Components Configuration

**Table 10. SMPS External Components**

| Ref | Description                                                    |

|-----|----------------------------------------------------------------|

| M1  | Sl3443, 2SQ2315                                                |

| L1  | 2.2 uH 3A < 100 mΩ series resistance (Ex. Bourns SRU8043-2R2Y) |

| D1  | SS8P3L 8A Schottcky Diode                                      |

| R1  | 24 kΩ                                                          |

| C1  | 10 μF Ceramic                                                  |

| C2  | 100 nF Ceramic                                                 |

| C3  | 100 nF Ceramic (place close to inductor)                       |

| C4  | 10 uF Ceramic (place close to inductor)                        |

| C5  | 1 nF Ceramic                                                   |

| C6  | 4 x 100 nF + 4 x 10nF Ceramic (place close to MCU supply pins) |

| C7  | 4 x 10 μF Ceramic (place close to MCU supply pins)             |

| C8  | 100 nF Ceramic                                                 |

| C9  | 1 μF Ceramic (Unless C1 is really close to the pin)            |

S32R274/S32R264 Series Data Sheet, Rev. 5, 04/2019

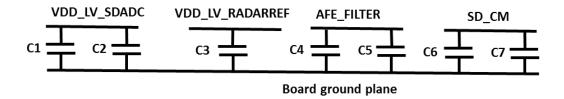

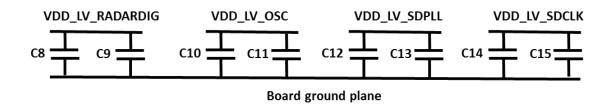

Figure 3. Radar AFE External Components Configuration

**Table 11. Radar AFE External Components**

| Component | Component<br>Value | Tolerance | Placement<br>Priority of<br>larger cap. <sup>1</sup> | Placement<br>Priority of<br>smaller cap <sup>1</sup> | Special notes |

|-----------|--------------------|-----------|------------------------------------------------------|------------------------------------------------------|---------------|

| C1        | 0.47 μF            | ±35%      | 3                                                    | _                                                    | _             |

| C2        | 0.1 μF             | ±35%      | _                                                    | 1                                                    | _             |

| C3        | 1.0 µF             | ±35%      | 7                                                    | _                                                    | _             |

| C4        | 1.0 µF             | ±35%      | 2                                                    | _                                                    | _             |

| C5        | 0.1 μF             | ±35%      | _                                                    | 4                                                    | _             |

| C6        | 1.0 µF             | ±35%      | 8                                                    | _                                                    | _             |

| C7        | 0.1 μF             | ±35%      | _                                                    | 6                                                    | _             |

| C8        | 1.0 µF             | ±35%      | 6                                                    | _                                                    | _             |

| C9        | 0.1 μF             | ±35%      | _                                                    | 5                                                    | _             |

| C10       | 1.0 µF             | ±35%      | 4                                                    | _                                                    | _             |

| C11       | 0.1 μF             | ±35%      | _                                                    | 2                                                    | _             |

| C12       | 1.0 µF             | ±35%      | 5                                                    | _                                                    | _             |

| C13       | 0.1 μF             | ±35%      | _                                                    | 3                                                    | _             |

| C14       | 1.0 µF             | ±35%      | 10                                                   | _                                                    | _             |

| C15       | 0.1 μF             | ±35%      | _                                                    | 8                                                    | _             |

| C16       | 1.0 µF             | ±35%      | 9                                                    | _                                                    | _             |

| C17       | 0.1µF              | ±35%      | _                                                    | 7                                                    | _             |

Table continues on the next page...

Table 11. Radar AFE External Components (continued)

| Component | Component<br>Value | Tolerance | Placement<br>Priority of<br>larger cap. <sup>1</sup> | Placement<br>Priority of<br>smaller cap <sup>1</sup> | Special notes                                         |

|-----------|--------------------|-----------|------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|

| C18       | 10 μF              | _         | 1                                                    | _                                                    | X7R type                                              |

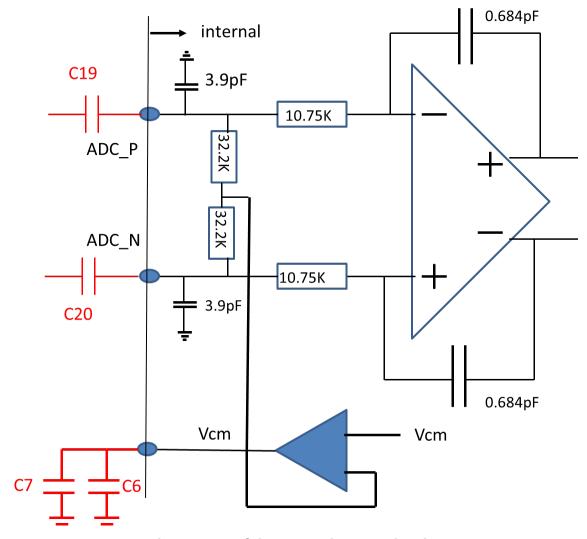

| C19       | 220 nF             | _         | _                                                    | _                                                    | Sigma Delta ADC input capacitor. See Figure 9         |

| C20       | 220 nF             | _         | _                                                    | _                                                    | Sigma Delta ADC input capacitor. See Figure 9         |

| R1        | 40.2 kΩ            | ±0.1%     | _                                                    | _                                                    | tempco = 25ppm/C                                      |

| R2        | 300 Ω              | _         | _                                                    | _                                                    | DAC RI See Table 27                                   |

| R3        | 300 Ω              | _         | _                                                    | _                                                    | DAC RI See Table 27                                   |

| Crystal   | 40MHz              | _         | _                                                    | _                                                    | Connected between XOSC_EXTAL/<br>XOSC_XTAL, ESR ≤ 30Ω |

All Radar AFE external bypass capacitors should be placed as close as possible to the associated package pin. As shown in Radar AFE External Components Configuration figure, most pins have two values of bypass capacitor. Greater than 0.1 μF is referred to as the larger cap. 0.1 μF is referred to as the smaller cap.

# 4.5 Electromagnetic Compatibility (EMC) specifications

EMC measurements to IC-level IEC standards are available from NXP on request.

# 4.6 Electrostatic discharge (ESD) characteristics

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n + 1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard.

#### **NOTE**

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

Table 12. ESD ratings

| No. | Symbol                | Parameter               | Conditions <sup>1</sup> | Class | Max value <sup>2</sup> | Unit |

|-----|-----------------------|-------------------------|-------------------------|-------|------------------------|------|

| 1   | V <sub>ESD(HBM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C  | H1C   | 2000                   | V    |

|     |                       | (Human Body Model)      |                         |       |                        |      |

Table continues on the next page...

| Table 12. E | ESD ratings ( | (continued) |

|-------------|---------------|-------------|

|-------------|---------------|-------------|

| No. | Symbol                | Parameter               | Conditions <sup>1</sup>        | Class | Max value <sup>2</sup> | Unit |

|-----|-----------------------|-------------------------|--------------------------------|-------|------------------------|------|

|     |                       |                         | conforming to AEC-<br>Q100-002 |       |                        |      |

| 2   | V <sub>ESD(CDM)</sub> | Electrostatic discharge | T <sub>A</sub> = 25 °C         | СЗА   | 500 <sup>3</sup>       | V    |

|     |                       | (Charged Device Model)  | conforming to AEC-<br>Q100-011 |       | 750 (corners)          |      |

- 1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

- 2. Data based on characterization results, not tested in production.

- 3. 500 V for non-AFE pins, 250 V for AFE pins.

### 5 I/O Parameters

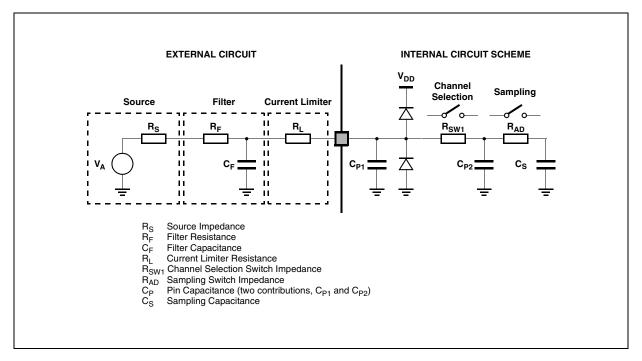

# 5.1 I/O pad DC electrical characteristics

NMI, TCK, TMS, JCOMP are treated as GPIO.

Table 13. I/O pad DC electrical specifications

| Symbol               | Parameter                                                 | Va                           | Unit                                |    |

|----------------------|-----------------------------------------------------------|------------------------------|-------------------------------------|----|

|                      |                                                           | Min                          | Max                                 |    |

| Vih_hys              | CMOS Input Buffer High Voltage (with hysteresis enabled)  | 0.65*V <sub>DD_HV_IO</sub>   | V <sub>DD_HV_IO</sub> + 0.3         | V  |

| Vil_hys              | CMOS Input Buffer Low Voltage (with hysteresis enabled)   | -0.3                         | 0.35*V <sub>DD_HV_IO</sub>          | V  |

| Vih                  | CMOS Input Buffer High Voltage (with hysteresis disabled) | 0.55 * V <sub>DD_HV_IO</sub> | $V_{DD\_HV\_IO} + 0.3$              | V  |

| Vil                  | CMOS Input Buffer Low Voltage (with hysteresis disabled)  | -0.3                         | 0.40 * V <sub>DD_HV_IO</sub>        | V  |

| Vhys                 | CMOS Input Buffer Hysteresis                              | 0.1 * V <sub>DD_HV_IO</sub>  | _                                   | V  |

| Vih <sub>TTL</sub>   | TTL Input high level voltage (All SAR_ADC input pins)     | 2                            | V <sub>DD_HV_ADCREFx</sub><br>+ 0.3 | V  |

| Vil <sub>TTL</sub>   | TTL Input low level voltage (All SAR_ADC input pins)      | -0.3                         | 0.56                                | V  |

| Vhyst <sub>TTL</sub> | TTL Input hysteresis voltage (All SAR_ADC input pins)     | 0.3                          | _                                   | V  |

| Pull_loh             | Weak Pullup Current <sup>1</sup>                          | 10                           | 55                                  | μΑ |

| Pull_lol             | Weak Pulldown Current <sup>2</sup>                        | 10                           | 55                                  | μΑ |

| linact_d             | Digital Pad Input Leakage Current (weak pull inactive)    | -2.5                         | 2.5                                 | μΑ |

| Voh                  | Output High Voltage <sup>3</sup>                          | 0.8 * V <sub>DD_HV_IO</sub>  | _                                   | V  |

| Vol                  | Output Low Voltage <sup>4</sup>                           | _                            | 0.2 * V <sub>DD_HV_IO</sub>         | V  |

| loh_f                | Full drive loh <sup>5</sup> (ipp_sre[1:0] = 11)           | 18                           | 70                                  | mA |

| lol_f                | Full drive Iol <sup>5</sup> (ipp_sre[1:0] = 11)           | 21                           | 120                                 | mA |

| loh_h                | Half drive loh <sup>5</sup> (ipp_sre[1:0] = 10)           | 9                            | 35                                  | mA |

| lol_h                | Half drive Iol <sup>5</sup> (ipp_sre[1:0] = 10)           | 10.5                         | 60                                  | mA |

#### I/O Parameters

- 1. Measured when pad = 0 V

- 2. Measured when pad =  $V_{DD\ HV\ IO}$

- 3. Measured when pad is sourcing 2 mA

- 4. Measured when pad is sinking 2 mA

- 5. Ioh/lol is derived from spice simulations. These values are NOT guaranteed by test.

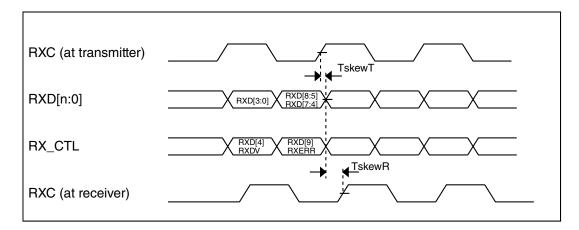

# 5.1.1 RGMII pad DC electrical characteristics

Table 14. RGMII pad DC electrical specifications

| Symbol   | Parameter                                              | Valu                         | Unit                         |    |

|----------|--------------------------------------------------------|------------------------------|------------------------------|----|

|          |                                                        | Min                          | Max                          |    |

| Vih      | CMOS Input Buffer High Voltage                         | 0.65 x V <sub>DD_HV_IO</sub> | V <sub>DD_HV_IO</sub> + 0.3  | V  |

| Vil      | CMOS Input Buffer Low Voltage                          | -0.3                         | 0.35 x V <sub>DD_HV_IO</sub> | V  |

| Pull_loh | Weak Pullup Current <sup>1</sup>                       | 10                           | 55                           | μΑ |

| Pull_lol | Weak Pulldown Current <sup>2</sup>                     | 10 55                        |                              | μΑ |

| linact_d | Digital Pad Input Leakage Current (weak pull inactive) | -2.5                         | 2.5                          | μΑ |

| Voh      | Output High Voltage <sup>3</sup>                       | 0.8 x V <sub>DD_HV_IO</sub>  | _                            | ٧  |

| Vol      | Output Low Voltage <sup>4</sup>                        | _                            | 0.2 * V <sub>DD_HV_IO</sub>  | V  |

| loh_f    | Full drive loh <sup>5</sup>                            | 8                            | 26                           | mA |

| lol_f    | Full drive Iol <sup>6</sup>                            | 8                            | 24                           | mA |

- 1. Measured when pad = 0 V

- 2. Measured when pad =  $V_{DD\_HV\_IO}$

- 3. Measured when pad is sourcing 2 mA

- 4. Measured when pad is sinking 2 mA

- 5. Ioh\_f value is measured with 0.8\*VDDE applied to the pad.

- 6. Iol\_f is measured when 0.2\*VDDE is applied to the pad.

# 5.2 I/O pad AC specifications

AC Parameters are specified over the full operating junction temperature range of -40°C to +150°C and for the full operating range of the  $V_{DD\ HV\ IO}$  supply defined in Table 7.

Table 15. Functional Pad electrical characteristics

| Symbol    | Prop. Delay (ns) <sup>1</sup> |           | Rise/Fall Edge (ns) <sup>2</sup> |         | Drive Load (pF) | SIUL2_MSCR[SRC |

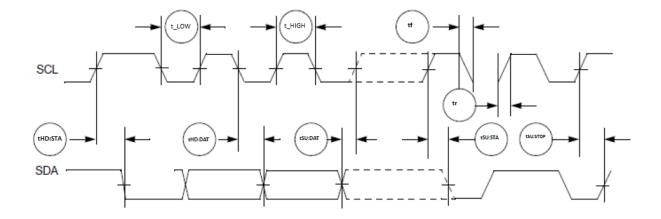

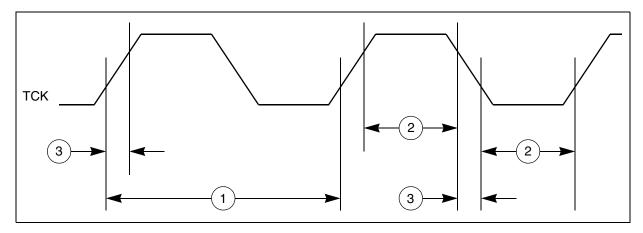

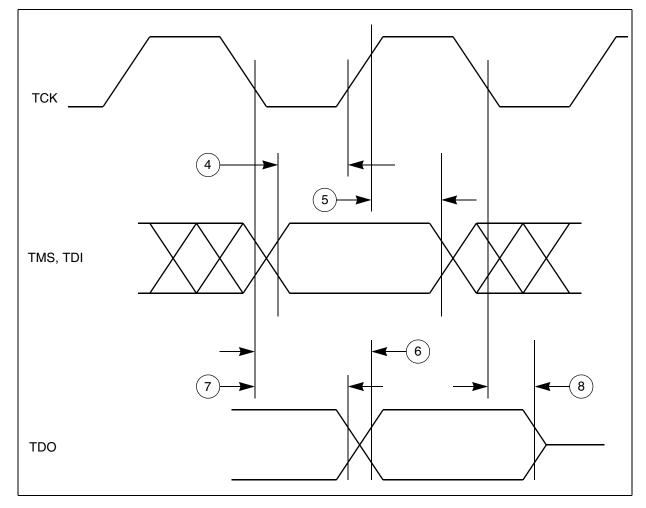

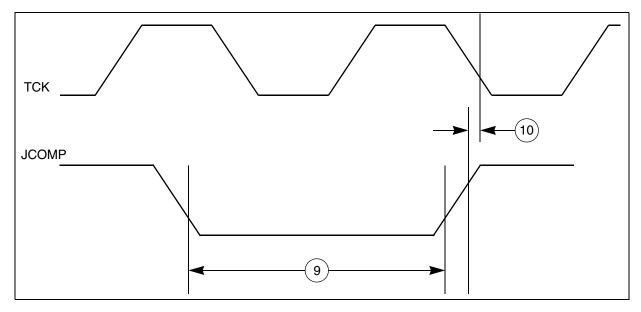

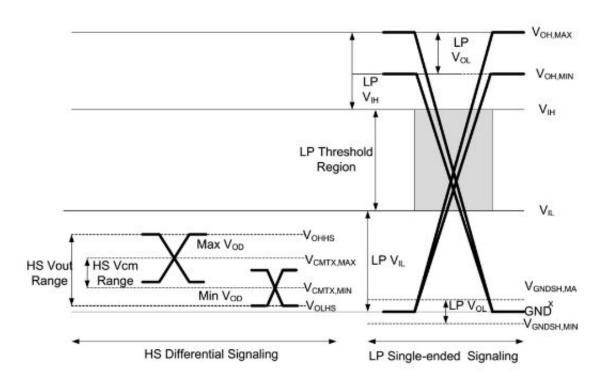

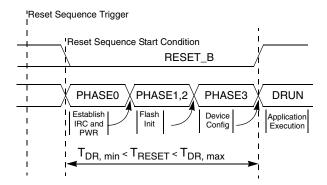

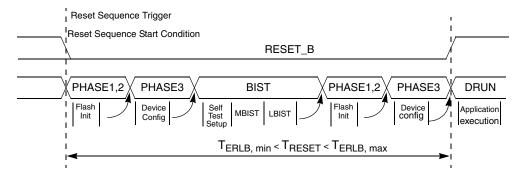

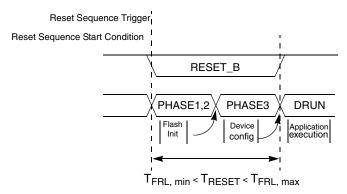

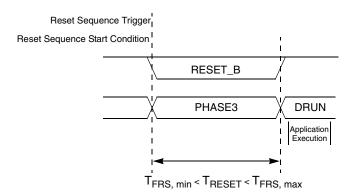

|-----------|-------------------------------|-----------|----------------------------------|---------|-----------------|----------------|