# Shanghai Siproin Microelectronics Co.,Ltd.

# **Built-in Clock, Calibration Free, Single Phase Energy Meter IC with Integrated Oscillator**

# SSP1839 Datasheet

Date: 2021/09/08

Version: 1.03

Official Website: <a href="http://www.SIPROIN.COM">http://www.SIPROIN.COM</a>

# **Catalog**

| 1. | . General Description                                  | 4  |

|----|--------------------------------------------------------|----|

|    | . Features                                             |    |

|    | . Order Specification                                  |    |

| 4. | . Block Diagram                                        | 5  |

| 5. | . Pin Assignment                                       | 5  |

| 6. | . Absolute Maximum Ratings                             | 6  |

| 7. | . Electrical Characteristics                           | 6  |

| 8. | . Internal Register Description                        | 8  |

|    | 8.1 Register list                                      | 8  |

|    | 8.2 Special Register Description                       | 9  |

|    | 8.2.1 User mode selection register                     | 9  |

|    | 8.2.2 Temperature mode control register                | 10 |

| 9. | . Theory of Operation                                  | 11 |

|    | 9.1 Current and voltage transient waveform measurement | 11 |

|    | 9.2 Channel offset correction                          | 12 |

|    | 9.3 Active Power                                       | 12 |

|    | 9.4 Active power offset correction                     | 13 |

|    | 9.5 Active power anti-creep                            | 13 |

|    | 9.6 Energy Measurement                                 | 14 |

|    | 9.7 Current and Voltage RMS                            | 15 |

|    | 9.8 RMS offset calibration of current and voltage      | 16 |

|    | 9.9 Leakage/Over-current Detection                     | 16 |

|    | 9.10 Phase Angle Calculation                           | 18 |

|    | 9.11 Zero Crossing Detection                           | 19 |

|    | 9.12 Temperature Measurement                           | 19 |

| 10 | 0. Communication Interface                             | 20 |

|    | 10.1 SPI                                               | 20 |

|    | 10.1.1 Operation Mode                                  | 21 |

|    | 10.1.2 Frame Structure                                 | 21 |

| 10.1.3 Write Operation Timing                       | 22 |

|-----------------------------------------------------|----|

| 10.1.4 Read Operation Timing                        | 22 |

| 10.1.5 Fault-tolerant mechanism of SPI interface    | 22 |

| 10.2 UART Communication methods                     | 23 |

| 10.2.1 Summarize                                    | 23 |

| 10.2.2 Description                                  | 23 |

| 10.2.3 Byte Formation                               | 23 |

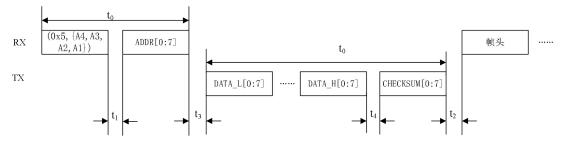

| 10.2.4 Write Timing                                 | 23 |

| 10.2.5 Read Timing                                  | 23 |

| 10.2.6 Timing Description                           | 24 |

| 10.2.7 Packet sending mode                          | 24 |

| 10.2.8 Full electrical parameter data packet format | 24 |

| 10.2.9 Protection mechanism of UART interface       | 25 |

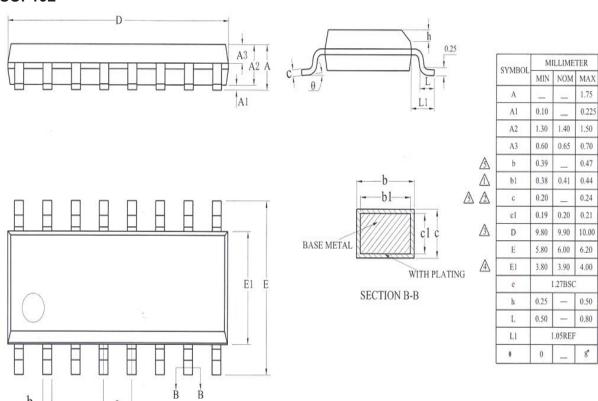

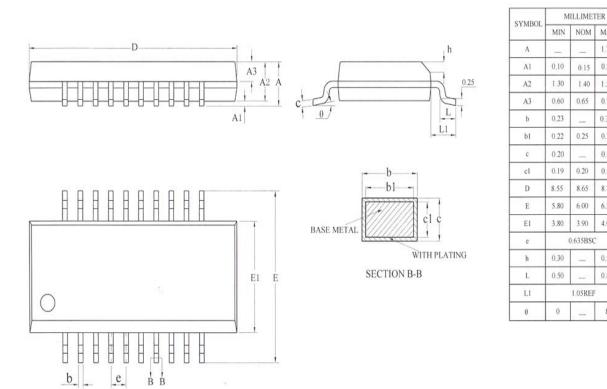

| 11. Package Information                             | 26 |

| SOP16L                                              | 26 |

| SSOP20L                                             | 26 |

| 12. Special Instructions                            |    |

| Version Change Description                          | 27 |

## 1. General Description

SSP1839 is a built-in clock and calibration-free energy metering IC, suitable for single-phase multifunctional electricity meter, smart socket, smart home appliances, electric bicycle charging pile and other applications with better cost performance.

SSP1839 integrates 3 high-precision sigma-delta ADC, it can measure two channel of current and one channel of voltage simultaneously.

SSP1839 can measure electric parameters such as current and voltage RMS, active power, active energy, fast current RMS (for leakage detection/over-current protection), and temperature detection, waveform output and so on. SSP1839 output data through the UART/SPI interface. It is available for the smart socket, smart appliances, single-phase multi-function power meter, electric bicycle charging pile and information requirement of data acquisition in electricity applications.

SSP1839 has a patented anti-creep design, which can be combined with reasonable external hardware design to ensure that the noise energy cannot be calculated in the energy pulse when there is no load.

#### SS0P20L

#### 2. Features

- 3 high-precision sigma-delta ADC, used to measure two channel of currents and one channel of voltage

- The range of current (10mA~35A) @1mohm

- The range of Active energy (1w~7700w) @1mohm@220V

- Measure RMS Voltage and Current, fast current RMS, Active Power, Active Energy

- The gain error is less than 1%, calibration-free when peripheral components meet certain conditions.

- Two current channel support electric leakage/over-current monitoring function, the threshold and response time can be configured

- Voltage zero-crossing logic output

- Built-in waveform register for load type analysis, Waveform data can be output for load type analysis

- Built-in temperature sensor, Meet the requirements of the product itself, such as over-temperature monitoring, high current node preset temperature alarm, room temperature measurement

- SPI(\$900KHz)/UART(4800bps), UART supports multi-chip address communication (SSOP20L)

- On-chip power supply monitoring, IC reset when VDD is lower than 2.7V(typical).

- On-chip voltage reference of 1.218V

- On-chip 4MHz oscillator circuit

- Power supply 3.3V, low power consumption 10mW (typical)

- Package: SSOP20L/SOP16L

# 3. Order Specification

| Part No         | Package | Manner of Packing | Devices per bag/reel |

|-----------------|---------|-------------------|----------------------|

| SSP1839-SOP16L  | SOP16L  | Reel              | 3000PCS              |

| SSP1839-SSOP20L | SSOP20L | Reel              | 2500PCS              |

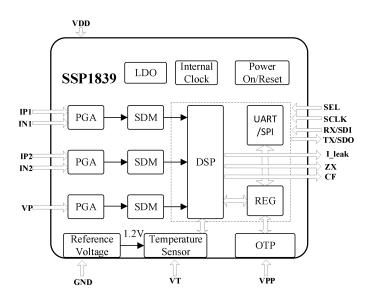

# 4. Block Diagram

Figure 1 Internal block diagram

# 5. Pin Assignment

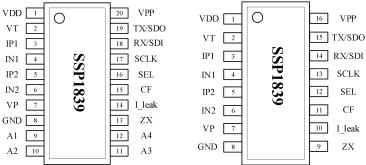

Figure 2 SSOP20L Figure 3 SOP16L

| SSOP20 | SOP16  | Pin Name | Description                                                                                                                     |

|--------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| 1      | 1      | VDD      | Power Supply (+3.3V).                                                                                                           |

| 2      | 2      | VT       | External temperature sensor(NTC) signal input.                                                                                  |

| 3, 4   | 3, 4   | IP1,IN1  | Analog input of current channel A, maximum differential voltage has a maximum input range of ±50mV(35mV RMS).                   |

| 5, 6   | 5, 6   | IP2,IN2  | Analog input of current channel B, maximum differential voltage has a maximum input range of ±50mV(35mV RMS).                   |

| 7      | 7 7 VP |          | Analog input for voltage channel, this differential input has a maximum input range of $\pm 100 \text{mV} (70 \text{mV RMS})$ . |

| 8  | 8  | GND    | GND                                                                                                                                                                                           |

|----|----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9  |    | A1     | Chip address setting pin, UART multi-chip communication                                                                                                                                       |

| 10 |    | A2     | mode, used to set the chip address, A4/A3/A2/A1 binary coding                                                                                                                                 |

| 11 |    | A3     | (0000~1111), can set the address 0~15; There is pull-down                                                                                                                                     |

| 12 |    | A4     | resistance inside the pin, which is 0 level when it is suspended, and high level when the pin is directly connected to VDD. It matches the device address in the UART communication protocol. |

| 13 | 9  | ZX     | Voltage channel zero-crossing output pin                                                                                                                                                      |

| 14 | 10 | I_leak | Channel B leakage/over-current alarm output                                                                                                                                                   |

| 15 | 11 | CF     | Energy pulse output, multiplex function refer to MODE register description                                                                                                                    |

| 16 | 12 | SEL    | Interface select pin (0: UART 1: SPI), pull-down resistance inside, disconnect is low-level (UART), connected to VDD is high-level (SPI)                                                      |

| 17 | 13 | SCLK   | SPI clock input. If using UART interface, this pin doesn't need be connected.                                                                                                                 |

| 18 | 14 | RX/SDI | Data input for SPI interface/Receive line for UART interface                                                                                                                                  |

| 19 | 15 | TX/SDO | Data output for SPI interface/Transmit line for UART interface, this pin require external pull-up resistor.                                                                                   |

| 20 | 16 | VPP    | Reserved, not connected.                                                                                                                                                                      |

# 6. Absolute Maximum Ratings

| Parameter                     | Symbol     | Value           | Unit       |

|-------------------------------|------------|-----------------|------------|

| Power Voltage VDD             | VDD        | <b>-</b> 0.3∼+4 | V          |

| Analog Input Voltage to GND   | IP1,IP2,VP | -4~+4           | V          |

|                               | A1~A4      |                 |            |

| Digital Input Voltage to GND  | UART_SEL   | -0.3∼VDD+0.3    | V          |

|                               | RX/SDI     |                 |            |

|                               | CF         |                 |            |

| Digital Output Voltage to GND | I_Leak     | -0.3∼VDD+0.3    | V          |

|                               | TX/SDO     |                 |            |

| Operating Temperature Range   | T          | <b>-</b> 40∼+85 | $^{\circ}$ |

| Storage Temperature Range     | Tstg       | -40~+85         | $^{\circ}$ |

Note: Unless specified otherwise, Tamb= 25°C

# 7. Electrical Characteristics

| Parameter         | Symbol | <b>Test Conditions</b> | Min | Тур | Max | Unit |

|-------------------|--------|------------------------|-----|-----|-----|------|

| Power Supply      | VDD    |                        | 3.0 |     | 3.6 | V    |

| Power Dissipation | Iop    | VDD=3.3V               |     | 3   |     | mA   |

| Measuring range   |        | 4000:1 Input dynamic   |     |     |     |      |

| Weasuring range   |        | range                  |     |     |     |      |

#### SSP1839

|                                   |         |                            |      |       | 551 | 1037 |

|-----------------------------------|---------|----------------------------|------|-------|-----|------|

| Active energy measurement         |         | 35A~100mA Input@           |      | 0.2   |     | %    |

| accuracy (large signal)           |         | 1mohm sampling resistor    |      |       |     |      |

| Active energy measurement         |         | 100mA~50mA Input@          |      | 0.4   |     | %    |

| accuracy (small signal)           |         | 1mohm sampling resistor    |      |       |     |      |

| Active energy measurement         |         | 50mA~10mA Input@           |      | 0.6   |     | %    |

| accuracy (tiny signal)            |         | 1mohm sampling resistor    |      |       |     |      |

| RMS measurement                   |         | 35A~100mA Input@           |      | 0.2   |     | %    |

| accuracy(large signal)            |         | 1mohm sampling resistor    |      |       |     |      |

| RMS measurement                   |         | 100mA~50mA Input@          |      | 2     |     | %    |

| accuracy(small signal)            |         | 1mohm sampling resistor    |      |       |     |      |

| RMS measurement                   |         | 50mA~10mA Input@           |      | 6     |     | %    |

| accuracy(tiny signal)             |         | 1mohm sampling resistor    |      |       |     |      |

| Fast RMS response time            | 50Hz    | Can be set to cycle/half   | 10   |       | 40  | mS   |

| _                                 | 60Hz    | cycle                      | 8.3  |       | 33  | mS   |

| Zero-crossing signal output delay |         |                            |      | 571   |     | uS   |

| Measurement error caused by       |         |                            |      |       |     |      |

| phase angle between channels      | PF08err | Phase advance 37 °         |      |       | 0.5 | %    |

|                                   | Proteii | (PF=0.8)                   |      |       | 0.3 | 70   |

| (capacitance)                     |         |                            |      |       |     |      |

| Measurement error caused by       | PF05err | Phase delay 60 °           |      |       | 0.5 | %    |

| phase angle between channels      | Proserr | (PF=0.5)                   |      |       | 0.3 | 70   |

| (sensibility)                     |         |                            |      |       |     |      |

| AC power suppression (output      | A CDCDD | ID/NI 100 N/               |      |       | 0.1 | 0/   |

| frequency amplitude               | ACPSRR  | IP/N=100mV                 |      |       | 0.1 | %    |

| variation)                        |         |                            |      |       |     |      |

| DC power suppression (output      | DODODD  | AND AL 100 AL              |      |       | 0.1 | 0/   |

| frequency amplitude               | DCPSRR  | VP/N=100mV                 |      |       | 0.1 | %    |

| variation)                        |         | D:001                      | -    |       |     |      |

| Analog input level (current)      |         | Differential current input |      |       | 50  | mV   |

|                                   |         | (peak)                     |      |       |     |      |

| Analog input level (voltage)      |         | Differential voltage input |      |       | 200 | mV   |

|                                   |         | (peak)                     |      |       |     |      |

| Analog input impedance            |         |                            |      | 370   |     | kΩ   |

| SEL pull-down resistor            |         | SEL(pull-down)             |      | 56.9  |     | kΩ   |

| Analog input bandwidth            |         | (-3dB)                     |      | 3.5   |     | kHz  |

| Internal voltage reference        | Vref    |                            |      | 1.218 |     | V    |

| Logic input high-level            |         | VDD=3.3V±5%                | 2.6  |       |     | V    |

| Logic input low-level             |         | VDD=3.3V±5%                |      |       | 0.8 | V    |

| Logic output high-level           |         | VDD=3.3V±5%                | VDD  |       |     | V    |

| Logic output ingii-levei          |         | IOH=5mA                    | -0.5 |       |     | v    |

| Logio output love lovel           |         | VDD=3.3V±5%                |      |       | 0.5 | 17   |

| Logic output low-level            |         | IOL=5mA                    |      |       | 0.5 | V    |

| 1                                 |         |                            |      |       |     |      |

Note: Unless specified otherwise, Tamb= 25°C

All voltage values take GND terminal potential as reference point.

Test conditions VDD=3.3V, Built-in crystal oscillator, electric energy is measured by CF output.

# 8. Internal Register Description

# 8.1 Register list

| 01111                                     | External Internal    |     |               |           |                |                                                         |  |  |  |

|-------------------------------------------|----------------------|-----|---------------|-----------|----------------|---------------------------------------------------------|--|--|--|

| Address                                   | Symbol               | R/W | R/W           | Bits      | Default        | Description                                             |  |  |  |

| Electrical parameter register (read only) |                      |     |               |           |                |                                                         |  |  |  |

| 0x00                                      | IA_FAST_R<br>MS      | R   | W             | 24        | 0x000000       | Channel A fast RMS, unsigned                            |  |  |  |

| 0x01                                      | IA_WAVE              | R   | W             | 20        | 0x00000        | Channel A current waveform register, signed             |  |  |  |

| 0x02                                      | IB_WAVE              | R   | W             | 20        | 0x00000        | Channel B current waveform register, signed             |  |  |  |

| 0x03                                      | V_WAVE               | R   | W             | 20        | 0x00000        | Voltage waveform register, signed                       |  |  |  |

| 0x04                                      | IA_RMS               | R   | W             | 24        | 0x000000       | Channel A current RMS register, unsigned                |  |  |  |

| 0x05                                      | IB_RMS               | R   | W             | 24        | 0x000000       | Channel B current RMS register, unsigned                |  |  |  |

| 0x06                                      | V_RMS                | R   | W             | 24        | 0x000000       | Voltage RMS register, unsigned                          |  |  |  |

| 0x07                                      | IB_FAST_R<br>MS      | R   | W             | 24        | 0x000000       | Channel B fast RMS, unsigned                            |  |  |  |

| 0x08                                      | A_WATT               | R   | W             | 24        | 0x000000       | Channel A active power register, signed                 |  |  |  |

| 0x09                                      | B_WATT               | R   | W             | 24        | 0x000000       | Channel B active power register, signed                 |  |  |  |

| 0x0A                                      | CFA_CNT              | R   | W             | 24        | 0x000000       | Channel A active energy pulse count, unsigned           |  |  |  |

| 0x0B                                      | CFB_CNT              | R   | W             | 24        | 0x000000       | Channel B active energy pulse count, unsigned           |  |  |  |

| 0x0C                                      | A_CORNER             | R   | W             | 16        | 0x0000         | Channel A current voltage waveform phase angle register |  |  |  |

| 0x0D                                      | B_CORNER             | R   | W             | 16        | 0x0000         | Channel B current voltage waveform phase angle register |  |  |  |

| 0x0E                                      | TPS1                 | R   | W             | 10        | 0x000          | Internal temperature register, unsigned                 |  |  |  |

| 0x0F                                      | TPS2                 | R   | W             | 10        | 0x000          | External temperature register, unsigned                 |  |  |  |

|                                           |                      | J   | Jser operated | d registe | r (read and wr | ite)                                                    |  |  |  |

| 0x10                                      | IA_FAST_R<br>MS_CTRL | R/W | R             | 16        | 0xFFFF         | Channel A fast RMS control register                     |  |  |  |

| 0x11                                      | IA_CHOS              | R/W | R             | 8         | 0x00           | Channel A current DC offset correction                  |  |  |  |

| 0x12                                      | IB_CHOS              | R/W | R             | 8         | 0x00           | Channel B current DC offset correction                  |  |  |  |

| 0x13                                      | IA_RMSOS             | R/W | R             | 8         | 0x00           | Channel A current RMS offset adjust register            |  |  |  |

| 0x14                                      | IB_RMSOS             | R/W | R             | 8         | 0x00           | Channel B current RMS offset adjust register            |  |  |  |

|    |          |                          |        |        |                                          |          | Channel A sative nerven affect adjust    |

|----|----------|--------------------------|--------|--------|------------------------------------------|----------|------------------------------------------|

| 0x | 15       | A WATTOS                 | R/W    | R      | 8                                        | 0x00     | Channel A active power offset adjust     |

|    |          | _                        |        |        |                                          |          | register                                 |

| Ox | 16       | B WATTOS                 | R/W    | R      | 8                                        | 0x00     | Channel B active power offset adjust     |

| UX | .10      | b_WAITOS                 | IV/ VV | K      | 0                                        | UXUU     | register                                 |

|    | 1.7      | WA CDEED                 | D/III  | D      | 0                                        | 0.00     | Active power no-load threshold           |

| UX | 17       | WA_CREEP                 | R/W    | R      | 8                                        | 0x0B     | register                                 |

| 0x | 18       | MODE                     | R/W    | R      | 16                                       | 0x0000   | User mode selection register             |

|    | 10       | SOFT_RES                 | D/W    | D      | 2.4                                      | 0.000000 | When 0x5A5A5A is written, the user       |

| UX | 19       | ET                       | R/W    | R      | 24                                       | 0x000000 | area register is reset to default        |

|    |          |                          |        |        |                                          |          | Write protection register. After writing |

|    | 1 4      | USR_WRPR                 |        | 0      | 0x55, the user operation register can be |          |                                          |

| UX | 1A       | OT                       | R/W    | R      | 8                                        | 8 0x00   | written. Write other values, user        |

|    |          |                          |        |        |                                          |          | operated register area is not writable   |

| 0x | 1B       | TPS_CTRL                 | R/W    | R      | 16                                       | 0x07FF   | Temperature mode control register        |

|    | 1.0      | TTD G 2                  | D/III  | -      |                                          | 0.0000   | External temperature sensor gain         |

| 0x | 1C       | TPS2_A                   | R/W    | R      | 8                                        | 0x0000   | coefficient adjust register              |

|    |          |                          |        | _      |                                          |          | External temperature sensor offset       |

| 0x | 1D       | TPS2_B                   | R/W    | R      | 8                                        | 0x0000   | coefficient adjust register              |

|    |          | IB FAST R                |        |        |                                          | 0xFFFF   |                                          |

| 0x | 1E       | MS CTRL                  | R/W    | R      | 16                                       |          | Channel B fast RMS control register      |

|    | 1D<br>1E | TPS2_B IB_FAST_R MS_CTPL | R/W    | R<br>R | 8                                        | 0x0000   | External temperature sensor offset       |

# 8.2 Special Register Description

# 8.2.1 User mode selection register (Note: X indicates either 0 or 1)

| 0x18  | MODE     | User mode selection register |                                              |                                              |  |  |  |  |

|-------|----------|------------------------------|----------------------------------------------|----------------------------------------------|--|--|--|--|

| No.   | name     | default value                | default value description                    |                                              |  |  |  |  |

|       |          |                              |                                              | 00 : High pass, AC measurement 01:same as 00 |  |  |  |  |

| [1:0] | IA_F_SEL | 0600                         | Current waveform IA selection through filter | 10 : Low pass, DC measurement                |  |  |  |  |

|       |          |                              |                                              | 11 : Full wave, AC/DC measurement            |  |  |  |  |

|       |          |                              |                                              | 00 : High pass, AC measurement               |  |  |  |  |

| [3:2] | IB_F_SEL | 0b00                         | Current waveform IB selection through filter | 01:same as 00  10 : Low pass, DC measurement |  |  |  |  |

|       |          |                              |                                              | 11: Full wave, AC/DC measurement             |  |  |  |  |

|       |          |                              | Voltage waveform                             | 00 : High pass, AC measurement               |  |  |  |  |

| [5:4] | V_F_SEL  | 0ь00                         | selection through filter                     | 01:same as 00  10 : Low pass, DC measurement |  |  |  |  |

# SSP1839

|           | •                  |       |                                                           |                                                                                                      |  |

|-----------|--------------------|-------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

|           |                    |       |                                                           | 11: Full wave, AC/DC measurement                                                                     |  |

| 6         | L_F_SEL            | 0b0   | Channel A/B fast effective value selection through filter | <ul><li>0: High pass filter front output</li><li>1: High pass filter behind output</li></ul>         |  |

| 7         | L_WAVE_SEL         | 0b0   | IB_WAVE waveform register output selection                | IB channel waveform     IB fast channel     waveform                                                 |  |

| 8         | RMS_UPDATE_SE<br>L | 0b0   | RMS register update rate                                  | 0: 400ms<br>1: 800ms                                                                                 |  |

| 9         | AC_FREQ_SEL        | 0b0   | AC frequency select                                       | 0: 50Hz<br>1: 60Hz                                                                                   |  |

| 10        | Reserved           | 0b0   | rese                                                      | rved                                                                                                 |  |

| 11        | CF_SEL             | 0b0   | CF pin output power pulse selection                       | 0: Channel A 1: Channel B                                                                            |  |

| 12        | CF_UNABLE          | 0Ь0   | CF output function selection                              | 0: Electric pulse, enable by MODE[11] configured 1: alarm function enable by TPS_CTRL[14] configured |  |

| 13~1<br>5 | reserved           | 3b000 | reserved                                                  |                                                                                                      |  |

# 8.2.2 Temperature mode control register

| 0x1B | TPS_CTRL |                  | Temperature mode co                                                                        | ntrol register                                                                                                                     |

|------|----------|------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| No.  | name     | default<br>value | des                                                                                        | cription                                                                                                                           |

|      |          |                  | [15] Temperature switch, default 0b0,Open the temperature measurement                      | 0: on<br>1: off                                                                                                                    |

|      |          |                  | [14] Alarm switch, default 0b0,                                                            | Temperature alarm on     Channel A over-current and leakage alarm on                                                               |

| 0x1B | TPS_CTRL | 0x07FF           | [13:12]] Temperature measurement selection, default 0b00 Automatic temperature measurement | 00: Automatic temperature measurement 01: the same as 00 10: Internal temperature measurement 11: External temperature measurement |

|      |          |                  | [11:10]Temperature<br>measurement interval default<br>0b01 100ms                           | 00: 50ms<br>01: 100ms<br>10: 200ms<br>11: 400ms                                                                                    |

|  | [ 9:0] External temperature |                                   |

|--|-----------------------------|-----------------------------------|

|  | measurement alarm threshold | Alarm when TPS2 register value is |

|  | setting, default 0x3FF,not  | greater than or equal to it.      |

|  | alarm                       |                                   |

### 9. Theory of Operation

SSP1839 is composed of analog signal processing module and digital signal processing module. The analog module includes three-channel PGA, three-channel sigma-delta ADC, internal clock, power on/reset monitor, temperature sensor, LDO and other related analog modules. The digital module is digital signal processing module (DSP).

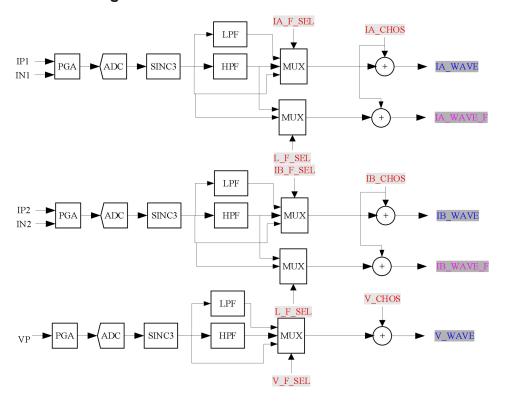

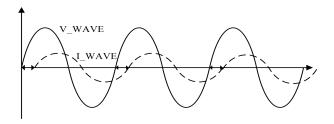

#### 9.1 Current and voltage transient waveform measurement

Figure 4

As shown in the figure above, two channels of current and one channel of voltage pass through the analog module amplifier (PGA) and the high-precision analog-to-digital conversion (ADC) respectively to get three channels of 1bit PDM to the digital module. The digital module passes through the SINC3 filter (SINC3), optional high-pass filter (HPF) or low-pass filter (LPF) and channel offset correction modules. Obtain the required current waveform data and voltage waveform data (IA\_WAVE, IB\_WAVE, V WAVE).

HPF and LPF are optional for the three channels. HPF is an AC measurement mode, LPF is a DC measurement mode, and full-wave measurement mode is a full-wave measurement mode if neither of them is passed. Set through user MODE register MODE[5:0].

SSP1839 has three high-precision ADCs, and the current is input by two-terminal differential signals: A current channel IP1/IN1, B current channel IP2/IN2, and voltage channel VP.

The current and voltage waveform data are updated at a rate of 7.8kbps. Each sampled data is 20bit signed value, which are saved in waveform registers (IA\_WAVE, IB\_WAVE, V\_WAVE). The waveform value can be read continuously when the SPI rate is greater than 375Kbps.

| Addmass | Symbol  | External | Internal | Bits | Default | Description                |  |

|---------|---------|----------|----------|------|---------|----------------------------|--|

| Address | Symbol  | R/W      | R/W      | Dits | Default | Description                |  |

| 0x01    | IA WAVE | R        | W        | 20   | 0x00000 | Channel A current waveform |  |

| UXU1    | IA_WAVE | K        | VV       | 20   | 0x00000 | register                   |  |

| 0x02    | IB WAVE | R        | W        | 20   | 0x00000 | Channel B current waveform |  |

| 0x02    | ID_WAVE | K        | VV       | 20   | 000000  | register                   |  |

| 0x03    | V_WAVE  | R        | W        | 20   | 0x00000 | Voltage waveform register  |  |

#### 9.2 Channel offset correction

The SSP1839 contains two 8-bit calibration registers (IA\_CHOS, IB\_CHOS) with a default value of 00H. They eliminate the deviation caused by the analog-to-digital conversion of the current channel and the voltage channel respectively by the data in the form of the complement of 2, Bit[7]is a symbol Bit.The deviation here may be due to the offset generated by the input and the ANALOG-to-digital conversion circuit itself. The offset correction allows the waveform offset to be 0 without load.

| Address | Symbol  | External | Internal | Bits | Default | Description                 |

|---------|---------|----------|----------|------|---------|-----------------------------|

| Audiess | Symbol  | R/W      | R/W      | Dits | Detault | Description                 |

| 0 11    | IA CHOC | R/W      | R        | 8    | 000     | Current channel A DC offset |

| 0x11    | IA_CHOS | K/W      | K        | 0    | 0x00    | correction                  |

| 0.12    | ID CHOC | D/XX     | D        | 0    | 0.00    | Current channel B DC offset |

| 0x12    | IB_CHOS | R/W      | R        | 8    | 0x00    | correction                  |

These registers are used for DC measurement mode, IA/IB/V LPF SEL=1.

Correction formula: CHOS =  $\frac{\text{WAVE-WAVE0}}{2^4}$

WAVE is the corrected waveform value, WAVE0 is the uncorrected waveform value;

Corresponding RMS value: RMS = RMS0 +  $\frac{3125*CHOS}{4}$

RMS is the corrected valid value, RMS0 is the uncorrected valid value.

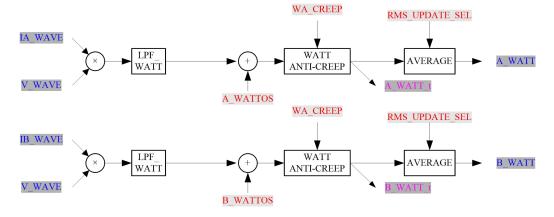

#### 9.3 Active Power

Figure 5

| Addmoss | Cymbol | External | Internal | Bits | Default  | Description                     |  |

|---------|--------|----------|----------|------|----------|---------------------------------|--|

| Address | Symbol | R/W      | R/W      | Dits | Delault  | Description                     |  |

| 0x08    | A_WATT | R        | W        | 24   | 0x000000 | Channel A active power register |  |

| 0x09    | B_WATT | R        | W        | 24   | 0x000000 | Channel B active power register |  |

Formula for calculating active power: A/B\_WATT =  $\frac{4046*I(A)*V(V)*COS~(\phi)}{Vref^2}$

I(A) and V(V) are the voltage RMS of analog input PIN(IP&IN, VP&GND),  $\varphi$  is the phase angle between I(A) and V(V) (AC signal), Vref is the on-chip reference voltage, the typical value is 1.218V.

This register indicates whether the active power is positive or negative. Bit[23] is the symbol Bit. Bit[23]=0 means the current power is positive and Bit[23]=1 means the current power is negative, in complement form.

#### 9.4 Active power offset correction

SSP1839 has two 8-bit active power offset adjust registers (A\_WATTOS, B\_WATTOS), default value is 00H. It eliminate the offset of active power in the measurement of electric energy with the data in the form of complement of 2. Bit[7] is the symbol Bit. The offset may come from board level noise or crosstalk. Offset adjustment can make the values in the active power register close to 0 with no load.

| Address | Symbol   | External R/W | Internal<br>R/W | Bits | Default | Description                                   |

|---------|----------|--------------|-----------------|------|---------|-----------------------------------------------|

| 0x15    | A_WATTOS | R/W          | R               | 8    | 0x00    | Channel A active power offset adjust register |

| 0x16    | B_WATTOS | R/W          | R               | 8    | 0x00    | Channel B active power offset adjust register |

$$WATTOS = \frac{WATT - WATT0}{8 \times 3.05172}$$

WATT is the active power after adjustment, and WATT0 is the active power before adjustment.

#### 9.5 Active power anti-creep

SSP1839 has the patented power anti-creep function, which ensures that the power of board level noise will not accumulate when there is no load.

This active power no-load threshold register(WA\_CREEP) is 8bit unsigned data, default value is 0BH. The corresponding relationship between this value and the active power register value is shown in the following formula. When the absolute value of the input active power signal is less than this value, the output active power is set to 0. This can make the value of the active power register is 0 and the energy does not accumulate in the case of no load, even if there is a tiny noise signal.

| Address | Symbol                                 | External<br>R/W | Internal<br>R/W | Bits | Default | Description                    |

|---------|----------------------------------------|-----------------|-----------------|------|---------|--------------------------------|

| 0x17    | WA CREEP                               | R/W             | R               | 8    | 0x0B    | Active power no-load threshold |

| 01117   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 10              | 1.              |      | 01102   | register                       |

Set WA\_CREEP based on the value of the power register A\_WATT, their corresponding relationship as below:

$$WA\_CREEP = \frac{WATT}{3.0517578125*8}$$

When the channel is in the anti-creep state, the RMS current register of this channel is also set to 0.

#### 9.6 Energy Measurement

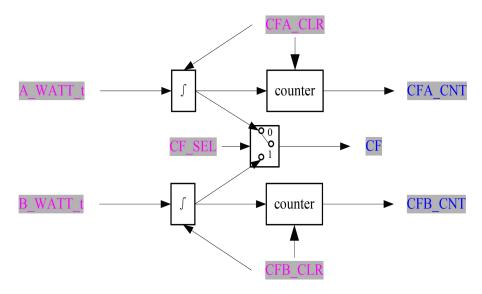

SSP1839 provides energy pulse measurement. The active instantaneous power is integrated by time to get active energy and output calibration pulse CF in proportion. CFA\_CNT and CFB\_CNT register saves the count of output energy pulse.

Figure 6

| 0x18 | MODE      | User mode selection register |                                     |                                                                                                       |  |  |  |  |

|------|-----------|------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| No.  | name      | default<br>value             | descript                            | tion                                                                                                  |  |  |  |  |

| 10   | Reserved  | 0b0                          | reserve                             | ed                                                                                                    |  |  |  |  |

| 11   | CF_SEL    | 060                          | CF pin output power pulse selection | 0: Channel A 1: Channel B                                                                             |  |  |  |  |

| 12   | CF_UNABLE | 0b0                          | CF output function selection        | 0: Electric pulse, enable by MODE[11] configured  1: alarm function enable by TPS_CTRL[14] configured |  |  |  |  |

Firstly, set MODE[12]=0 to select CF pin to output power pulse, and then set MODE[11] to select power pulse of channel A or channel B to output.

| Address           | Symbol   | External | Internal | Bits | Default   | Description                   |

|-------------------|----------|----------|----------|------|-----------|-------------------------------|

| Audress           | Symbol   | R/W      | R/W      | Dits | Delault   | Description                   |

| 0x0A              | CFA CNT  | R        | W        | 24   | 0x000000  | Channel A active energy pulse |

| UXUA              | CIA_CIVI | K        | VV       | 24   | 0.000000  | count, unsigned               |

| O <sub>w</sub> OD | CED CNT  | R        | W        | 24   | 0**000000 | Channel B active energy pulse |

| 0x0B              | CFB_CNT  | K        | VV       | 24   | 0x000000  | count, unsigned               |

The count of active energy pulses corresponds to the consumption of electricity. The result is stored in two registers, CFA\_CNT and CFB\_CNT. The count of pulses can be counted directly from the CF pin through I/O interruption. When the period of CF is less than 180ms, the pulse is 50% duty cycle. When it is greater than or equal to 180ms, the fixed pulse width of high-level is 90ms.

Note: CFA\_CNT, CFB\_CNT is pulse algebraic sum accumulation. It means that pulse plus at positive energy and minus at negative energy.

The cumulative time of each CF pulse:  $t_{CF} = \frac{1638.4*256}{WATT}$

WATT is the corresponding active power register value (A WATT, B WATT)

#### 9.7 Current and Voltage RMS

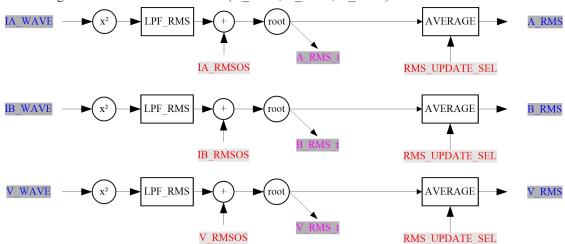

The RMS of three channels is shown in the figure below. After the square circuit  $(X^2)$ , the low-pass filter (LPF\_RMS) and the ROOT circuit (ROOT), the instantaneous value RMS\_t of RMS is calculated, and then the average value of the three channels (A RMS, B RMS, V RMS) is calculated.

Figure 7

| Address | Symbol  | External | Internal | Bits | Default  | Description                     |  |  |  |

|---------|---------|----------|----------|------|----------|---------------------------------|--|--|--|

| Address | Symbol  | R/W      | R/W      | Dits | Delault  | Description                     |  |  |  |

| 0x04    | IA RMS  | R        | W        | 24   | 0x000000 | Channel A current RMS register, |  |  |  |

| 0x04    | IA_KWIS | K        | VV       | 24   | 0x000000 | unsigned                        |  |  |  |

| 005     | ID DMC  | R        | W        | 24   | 0000000  | Channel B current RMS register, |  |  |  |

| 0x05    | IB_RMS  | K        | W        | 24   | 0x000000 | unsigned                        |  |  |  |

| 0x06    | V_RMS   | R        | W        | 24   | 0x000000 | Voltage RMS register, unsigned  |  |  |  |

| 0x18 | MODE           | User mode selection register |                          |                      |  |  |

|------|----------------|------------------------------|--------------------------|----------------------|--|--|

| No.  | name           | default description value    |                          |                      |  |  |

| 8    | RMS_UPDATE_SEL | 0ь0                          | RMS register update rate | 0: 400ms<br>1: 800ms |  |  |

Set MODE[8].RMS\_UPDAT\_SEL, the average refresh time of RMS can be selected as 400ms or 800ms, and the default value is 400ms. When a current channel is in anti-creep state, the RMS of the current channel is 0.

The current RMS conversion formula: IA/B\_RMS =  $\frac{324004*I(A)}{Vref}$

The voltage RMS conversion formula:  $V_RMS = \frac{79931*V(V)}{Vref}$

Vref is the reference voltage, the typical value is 1.218V.

I(A) is the input signal between IP1 and IN1 pins (mV), and V(V) is the input signal of VP pins (mV).

#### 9.8 RMS offset calibration of current and voltage

SSP1839 has two 8-bit RMS offset register (IA\_RMSOS and IB\_RMSOS), whose default value is 00H. It is used to calibrate the deviation in RMS with the complement form of 2. This deviation may come from the input noise.Because there is a square operation in calculating the RMS, this may introduce DC offset caused by noise.The deviation calibration can make the value in the RMS register close to 0 without load.

| Adduses | Cymhol    | External | Internal | D:4a | Default | Dogovintion                  |

|---------|-----------|----------|----------|------|---------|------------------------------|

| Address | Symbol    | R/W      | R/W      | Bits | Default | Description                  |

| 0x13    | IA RMSOS  | R/W      | R        | 8    | 0x00    | Channel A current RMS offset |

| 0X13    | IA_KWISOS | IC/ W    | K        | 0    | UXUU    | adjust register              |

| 0-:14   | ID DMCOC  | D/W      | D        | 0    | 000     | Channel B current RMS offset |

| 0x14    | IB_RMSOS  | R/W      | R        | 8    | 0x00    | adjust register              |

Calibration formula: RMSOS =  $\frac{RMS^2 - RMS0^2}{9.3132 \times 2^{15}}$

RMS0 is the RMS current value before correcting and RMS is the RMS current value after correcting o

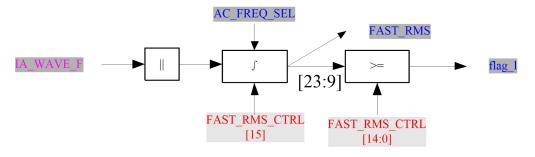

#### 9.9 Leakage/Over-current Detection

SSP1839 has two channels A/B of fast RMS register, which can detect half cycle or cycle RMS. This function can be used for leakage or over-current detection. The source of waveform L\_WAVE is shown below.

HPF can be passed or not passed, HPF is not passed by default, can get the absolute value of IA/B\_WAVE\_F accumulate by half-cycle or one cycle time, which is selected by FAST\_RMS\_CTRL[15]. Cycle accumulation is selected by default, The maximum response time is 40ms (50Hz) or 33mS (60Hz), Note that the runout of IA/IB\_FAST\_RMS register is relatively large when half cycle wave accumulation occurs. Distinguish between 50Hz and 60Hz half-cycle time (AC FREQ SEL).

Figure 8

| Address | Symbol               | External | Internal | Bits | Dofoult | Description                                 |

|---------|----------------------|----------|----------|------|---------|---------------------------------------------|

| Address | Symbol               | R/W      | R/W      | DIUS | Default |                                             |

| 0x10    | IA_FAST_RMS_CT<br>RL | R/W      | R        | 16   | 0xFFFF  | Channel A fast current RMS control register |

| 0x1E    | IB_FAST_RMS_CT<br>RL | R/W      | R        | 16   | 0xFFFF  | Channel B fast current RMS control register |

Set the refresh time to half-cycle or cycle by IA\_FAST\_RMS\_CTRL and IB\_FAST\_RMS\_CTRL, and set the fast RMS threshold (Leakage or over-current threshold).

| 0x10 | MODE                    | Fast RMS register         |                                |               |  |

|------|-------------------------|---------------------------|--------------------------------|---------------|--|

| No.  | name                    | default value description |                                |               |  |

|      |                         |                           | [15]Channel A fast RMS refresh | 0: half-cycle |  |

| 010  | 0x10 IA_FAST_RMS_CTRL 0 | 0xFFFF                    | time                           | 1: cycle      |  |

| UXIU |                         | UXFFFF                    | [14:0]Channel A fast RMS       |               |  |

|      |                         |                           | threshold                      |               |  |

|      |                         |                           | [15]Channel B fast RMS         | 0: half-cycle |  |

| 0x1E | ID EAST DMS CTDI        | 0xFFFF                    | refresh time                   | 1: cycle      |  |

| UXIE | IB_FAST_RMS_CTRL        | UXFFFF                    | [14:0]Channel B fast RMS       |               |  |

|      |                         |                           | threshold                      |               |  |

Set AC frequency by MODE[9].

| 0x18 | MODE          | User mode selection register |              |         |  |  |

|------|---------------|------------------------------|--------------|---------|--|--|

| No.  | name          | default value                | description  |         |  |  |

| 0    | 9 AC_FREQ_SEL | 01-0                         | AC frequency | 0: 50Hz |  |  |

| 9    |               | 0ь0                          | selection    | 1: 60Hz |  |  |

Refresh the 24-bit unsigned RMS register according to one cycle or half cycle, Bit[23:9] of the FAST\_RMS register compare with the leakage/over-current threshold FAST\_RMS\_CTRL [14:0], if the value is greater than or equal to the set threshold, then leakage/over-current alarm output pin will be high level.

| Address            | Symbol      | External<br>R/W | Internal<br>R/W | Bits | Default  | Description                          |

|--------------------|-------------|-----------------|-----------------|------|----------|--------------------------------------|

| 0x00               | IA FAST RMS | R               | W               | 24   | 0x000000 | Channel A fast current               |

|                    |             |                 |                 |      |          | RMS, unsigned Channel A fast current |

| $0x07$   IB_FAST_R | IB_FAST_RMS | R               | W               | 24   | 0x000000 | RMS, unsigned                        |

Channel B leakage/over-current alarm output indicator pin is I\_leak, it can be directly output without configuration.

Channel A leakage/over-current alarm output indicator pin is CF, set MODE[12]=1 and TPS CTRL[14]=1 before use it.

| 0x18 | MODE         | User mode selection register |                    |                            |  |  |

|------|--------------|------------------------------|--------------------|----------------------------|--|--|

| No.  | name         | default value                | description        |                            |  |  |

| 12   | 12 CF_UNABLE | 060                          | CF output function | 0: energy pulse, enable by |  |  |

| 12   |              | 0.00                         | selection          | MODE[11] configured        |  |  |

|  |  | 1: Temperature               |

|--|--|------------------------------|

|  |  | measurement/Leakage alarm,   |

|  |  | enable by TPS[14] configured |

| 0x1B | TPS_CTRL      | Temperature mode control register |                 |                                         |  |

|------|---------------|-----------------------------------|-----------------|-----------------------------------------|--|

| No.  | name          | default value                     | description     |                                         |  |

|      |               |                                   | A 10 mm         | 0: Temperature alarm on                 |  |

| 14   | 14 ALERT_CTRL | 0b0                               | Alarm selection | 1: Channel A leakage/over-current alarm |  |

|      |               |                                   | SCICCHOIL       | on                                      |  |

Since the fast effective values are updated by cycle or half-cycle, the interrupt response time is up to 2 cycles or 2 half-cycles.

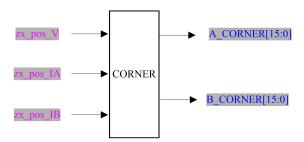

## 9.10 Phase Angle Calculation

SSP1839 has phase angle measurement function. The reactive quadrant can be indicated by the angle of A/B current and voltage respectively by calculating the positive zero-crossing time difference between current and voltage. It is updated to the register CORNER\_A/CORNER\_B when the current is positive zero crossing. The register is a 16-bit unsigned number.

Figure 9

| Address | Symbol   | External<br>R/W | Internal<br>R/W | Bits | Default | Description                                             |

|---------|----------|-----------------|-----------------|------|---------|---------------------------------------------------------|

| 0x0C    | A_CORNER | R               | W               | 16   | 0x0000  | Channel A current voltage waveform phase angle register |

| 0x0D    | B_CORNER | R               | W               | 16   | 0x0000  | Channel B current voltage waveform phase angle register |

Figure 10

Phase Angle conversion formula:  $2*pi*A/B\_CORNER*\frac{f_c}{f_0}$ , The unit is radian

Among them,  $f_c$  is the frequency of the AC signal source, the default value is 50Hz.  $f_0$  is the sampling frequency, the typical value is 1MHz.

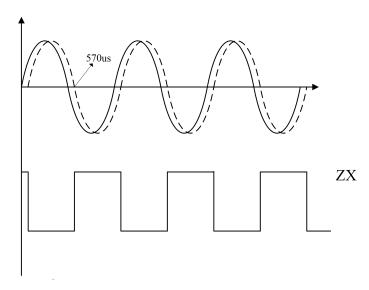

#### 9.11 Zero Crossing Detection

SSP1839 has the voltage zero-crossing detection function, and the zero-crossing signal is directly output by pin ZX. When ZX=0, it indicates the positive half cycle of the waveform, and when ZX=1, it indicates the negative half cycle of the waveform. The delay between the zero-crossing signal and the actual input signal is about 570us.

Figure 11

# 9.12 Temperature Measurement

SSP1839 supports internal temperature measurement and external temperature measurement.

External temperature measurement, optional output alarm indicator, Turn on the alarm function, CF pin selection output alarm signal, the CF pin will output high-level if the TPS2 is greater than or equal to the alarm threshold, Temperature indicator alarm. when the temperature value is lower than the alarm value or the alarm function is turned off, Exit alarm indicator.

| 0x1B | TPS_CTRL |                                     | Temperature mode control register                                                        |                                                                                                                                    |  |  |  |  |

|------|----------|-------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| No.  | name     | default value                       | description                                                                              | on                                                                                                                                 |  |  |  |  |

|      |          |                                     | [15] Temperature measurement switch, default 0b0,Open the temperature measurement        | 0: on 1: off                                                                                                                       |  |  |  |  |

| 0.15 |          | [14] Alarm selection , default 0b0, | 0: Temperature alarm on 1: Channel A leakage/over-current alarm on                       |                                                                                                                                    |  |  |  |  |

| 0x1B | TPS_CTRL | PS_CTRL 0x07FF                      | [13:12]Temperature measurement selection, default 0b00 Automatic temperature measurement | 00: Automatic temperature measurement 01: the same as 00 10: internal temperature measurement 11: external temperature measurement |  |  |  |  |

| inte | 1:10]Temperature measurement<br>erval selection , default 0b01 | 01:<br>10: | 50ms<br>100ms<br>200ms<br>400ms |

|------|----------------------------------------------------------------|------------|---------------------------------|

| [ 9: | [ 9:0]External temperature alarm                               |            |                                 |

| thre | eshold, default 0x3FF                                          |            |                                 |

First set MODE[12]=1, and then set TPS\_CTRL[14]=0, then CF pin is turned on to output external temperature alarm indicator.

| 0x18 | MODE      | User mode selection register |                              |                                                                                                                |  |  |

|------|-----------|------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| No.  | name      | default value description    |                              |                                                                                                                |  |  |

| 12   | CF_UNABLE | 0b0                          | CF output function selection | 0: energy pulse, enable by MODE[11] configured  1: Temperature measurement alarm, enable by TPS[14] configured |  |  |

The external and internal temperature values are saved in the TPS2 and TPS1 registers respectively.

| Addussa | Cymahal | External | Internal | Bits Default |         | Degenintien                             |  |

|---------|---------|----------|----------|--------------|---------|-----------------------------------------|--|

| Address | Symbol  | R/W      | R/W      | Bits         | Delault | Description                             |  |

| 0x0E    | TPS1    | R        | W        | 10           | 0x0000  | Internal temperature register, unsigned |  |

| 0x0F    | TPS2    | R        | W        | 10           | 0x0000  | External temperature register, unsigned |  |

Internal temperature measurement formula: Tx=(170/448)(TB/2-32)-45

TB is the value in TPS1.

The external temperature is measured by SAR ADC. The maximum input signal of the VT pin is 0.55\*VDD (V), The TPS2 register value is the corresponding AD sampling value, full scale is 1024.

| Address           | Symbol       | External | Internal     | D:4a         | Dofoult | Description                        |                                   |

|-------------------|--------------|----------|--------------|--------------|---------|------------------------------------|-----------------------------------|

|                   |              | R/W      | R/W          | Bits Default |         | Description                        |                                   |

| 0x1C              | TPS2 A       | R/W      | R            | o            | 0x00    | External temperature sensor gain   |                                   |

| UXIC              | IFSZ_A       | IV W     | IV/ VV       | K            | 0       | UXUU                               | coefficient correction A register |

| 0 <sub>w</sub> 1D | D TPS2 B R/W | D/W      | D            | 8            | 0**00   | External temperature sensor offset |                                   |

| 0x1D              | 1PS2_B       | K/W      | R/W R 8 0x00 |              | 0x00    | coefficient correction B register  |                                   |

# 10. Communication Interface

Register data are sent as 3 bytes (24bit). The data is fixed 3 bytes, if valid data bytes are less than 3 bytes, invalid bits are filled with 0.

#### 10.1 SPI

- Select by pin UART\_SELL, multiplex with UART

- Slave mode

- •Half-duplex communication, the communication rate can be configured, the maximum communication rate is 900khz

- 8-bit data transmission, MSB first, LSB last

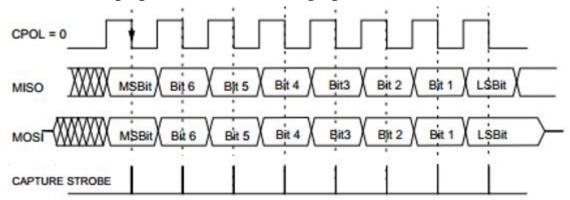

• Clock polarity / phase (CPOL = 0, CPHA = 1)

#### 10.1.1 Operation Mode

The master device works in Mode1: CPOL=0, CPHA=1, In idle state, SCLK is at low-level. Data is transmitted on the first edge, which is the transition from low level to high level of SCLK, so data is received on the falling edge and data is sent on the rising edge.

Figure 12

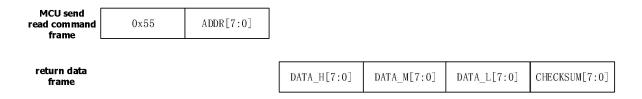

#### 10.1.2 Frame Structure

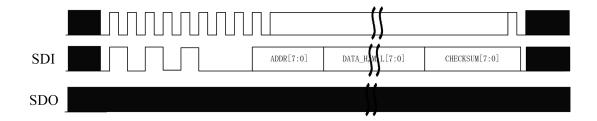

In SPI communication mode, MCU send 8-bit identification byte (0x55) or (0xA5). (0x55) is the read operation identification byte and (0xA5) is the write operation identification byte. Then send the address byte of the register will be accessed (refer to SSP1839 register list). The below figure shows the data transfer sequence for read and write operations respectively. After one frame of data is transmitted, SSP1839 re-enters the communication mode. The number of SCLK pulses required for each reading and writing operation is 48 bits.

There are two types of frame structures, which are explained as follows:

1) Write operation frame

| Write operation | 0xA5                                   | ADDR[7:0] | DATA_H[7:0] | DATA_M[7:0] | DATA_L[7:0] | CHECKSUM[7:0] |

|-----------------|----------------------------------------|-----------|-------------|-------------|-------------|---------------|

| frame           | B0000000000000000000000000000000000000 |           |             |             |             |               |

The checksum byte is ((0xA5 + ADDR + DATA\_H + DATA\_M+ DATA\_L)& 0xFF) and then bitwise inverted.

2) Read operation frame

The checksum byte is ((0x55 + ADDR + DATA\_H + DATA\_M+ DATA\_L)& 0xFF) and then bitwise

inverted.

#### 10.1.3 Write Operation Timing

The serial write timing is performed as follows. The frame identification byte {0xA5} indicates that the data communication operation is data writing. The MCU need make the data ready before the lower edge of SCLK, and shift the data at the lower edge of this clock. All remaining bits of the data are also shifted left on the lower edge of this SCLK (Figure 13).

Figure 13

#### 10.1.4 Read Operation Timing

During the data read operation, SSP1839 shifts the corresponding data to the DOUT pin on the rising edge of SCLK. DOUT keeps unchanged during SCLK =1.MCU can sample DOUT value before the next falling edge. MCU must send a read command frame first before read operation.

Figure 14

When SSP1839 is in communication mode, the frame identification byte {0x55} indicates that the data communication operation is data reading. After receiving the register address, SSP1839 starts to shift out the data in the register on the rising edge of SCLK (Figure 14). All remaining bits of the register data are shifted out on subsequent rising SCLK edges. Therefore, On the falling edge of SCLK, an external device can sample the output data of the SPI. Once the read operation is completed, SPI re-enters the communication mode. SDO enters a high-impedance state on the falling edge of the last SCLK signal.

#### 10.1.5 Fault-tolerant mechanism of SPI interface

SPI supports soft reset function, reset SPI interface individually by sending 6 bytes of 0xFF.

Note: SPI communication does not support chip selection. If 20PIN package is selected, A4A2 should be grounded and A3A1 connected to high level.

#### 10.2 UART Communication methods

#### 10.2.1 Summarize

SSP1839 supports UART communication. The UART interface only requires two low speed optocouplers to achieve isolated communication.

Baud rate: 4800bps Check bits: None Data bits: 8 Stop bits: 1.5 Slave mode, half-duplex communication.

Both packages have UART communication, 20 PIN package with chip selection address [A4 A3 A2 A1], device address 00 to 15 can be set.

#### 10.2.2 Description

UART port Settings: Communication baud rate is 4800bps, no parity, stop bit 1.5.

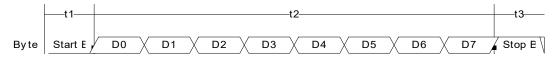

#### 10.2.3 Byte Formation

Start bit low duration: t1=208us;

Valid data bit duration: t2=208\*8=1664us Stop bit high duration: t3=208us+104us

#### 10.2.4 Write Timing

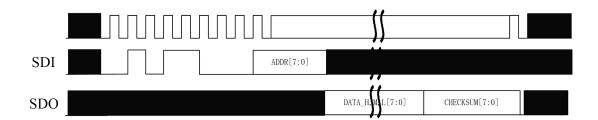

The data write sequence of the host UART is shown in the figure below. The host sends command bytes (0xA,{A4,A3,A2,A1}) first, then write address bytes (ADDR), then sends data bytes in sequence, and finally checksum bytes.

(0xA,{A4,A3,A2,A1}) is the frame identification byte for the write operation. If [A4: A1]=0101, the device address is 5 and the frame identification byte is 0xA5.

ADDR is the internal target register in SSP1839 corresponding to the write operation.

The checksum byte is(((0xA,{A4,A3,A2,A1})+ADDR+Data\_L+Data\_M+Data\_H)& 0xFF) and then bitwise inverted.

Note: The address of SSP1839-SOP16 is 5, that is, the first byte is 0xA5.

#### 10.2.5 Read Timing

The timing of reading data is shown below. MCU first sends the command bte (0x5,{A4,A3,A2,A1}) and the address of the target register (ADDR), and then SSP1839 sends data bytes in sequence. Finally sends the checksum byte.

(0x5,{A4,A3,A2,A1}) is the frame identification byte for the read operation. If [A4: A1]=0101, the device address is 5 and the frame identification byte is 0x55.

ADDR is the internal target register in SSP1839 corresponding to the read operation.

The checksum byte is (((0x5,{A4,A3,A2,A1})+ADDR+Data\_L+Data\_M+Data\_H)& 0xFF) and then bitwise inverted.

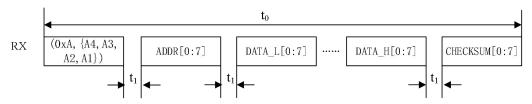

#### 10.2.6 Timing Description

|    | Description                                                          | Min | Type | Max | Unit |

|----|----------------------------------------------------------------------|-----|------|-----|------|

| t1 | Interval between MCU sending bytes                                   | 0   |      | 20  | mS   |

| t2 | Frame interval                                                       | 0.5 |      |     | uS   |

| t3 | Interval between the end of MCU sending register address and SSP1839 |     | 72   |     | uS   |

|    | sending byte during read operation                                   |     |      |     |      |

| t4 | Interval between SSP1839 sending bytes                               |     | 116  |     | uS   |

#### 10.2.7 Packet sending mode

After received the command " $(0x5, \{A4, A3, A2, A1\})$  + 0xAA", SSP1839 will return a full electrical parameter data packet. The returned data packet has a total of 35 bytes, and 4800bps takes 77ms. The specific format is: Frame head (1byte head)  $\rightarrow$ Current A fast effective value (3byte IA\_FAST\_RMS)  $\rightarrow$ Current A effective value (3byte IA\_RMS)  $\rightarrow$ Current B effective value (3byte IB\_RMS)  $\rightarrow$ Current B fast effective value (3byte IB\_FAST\_RMS)  $\rightarrow$ Channel A power value (3byte A\_WATT)  $\rightarrow$ Channel B power value (3byte B\_WATT)  $\rightarrow$ Channel A pulse meter value (3byte CFA\_CNT)  $\rightarrow$ Channel B pulse meter value (3byte CFB\_CNT)  $\rightarrow$ Internal thermometer value (2byte TPS1 + 1byte 0)  $\rightarrow$ External thermometer value (2byte TPS2 + 1byte 0)  $\rightarrow$ Checksum value (1byte CHECKSUM).

#### 10.2.8 Full electrical parameter data packet format

| Name        | No. | Value         | Name    | No. | Value     |

|-------------|-----|---------------|---------|-----|-----------|

| Frame head  | 0   | Head (0x55)   |         | 19  | B_WATT_1  |

|             | 1   | IA_FAST_RMS_1 | B_WATT  | 20  | B_WATT_m  |

| IA_FAST_RMS | 2   | IA_FAST_RMS_m |         | 21  | B_WATT_h  |

|             | 3   | IA_FAST_RMS_h |         | 22  | CFA_CNT_1 |

|             | 4   | IA_RMS_1      | CFA_CNT | 23  | CFA_CNT_m |

| IA_RMS      | 5   | IA_RMS_m      |         | 24  | CFA_CNT_h |

|             | 6   | IA_RMS_h      |         | 25  | CFB_CNT_1 |

|             | 7   | IB_RMS_1      | CFB_CNT | 26  | CFB_CNT_m |

| IB_RMS      | 8   | IB_RMS_m      |         | 27  | CFB_CNT_h |

|             | 9   | IB_RMS_h      | TPS1    | 28  | TPS1_1    |

|             | 10 | V_RMS_1       |          | 29 | TPS1_m   |

|-------------|----|---------------|----------|----|----------|

| V_RMS       | 11 | V_RMS_m       |          | 30 | 0x00     |

|             | 12 | V_RMS_h       |          | 31 | TPS2_1   |

|             | 13 | IB_FAST_RMS_1 | TPS2     | 32 | TPS2_m   |

| IB_FAST_RMS | 14 | IB_FAST_RMS_m |          | 33 | 0x00     |

|             | 15 | IB_FAST_RMS_h | checksum | 34 | checksum |

|             | 16 | A_WATT_1      |          |    |          |

| A_WATT      | 17 | A_WATT_m      |          |    |          |

|             | 18 | A_WATT_h      |          |    |          |

checksum= $(((0x5, \{A4,A3,A2,A1\}) + 0x55 + data1_l + data1_m + data1_h + .....)$ & 0xff) and then bitwise inverted.

#### 10.2.9 Protection mechanism of UART interface

UART communication has a timeout protection mechanism. If the interval between bytes exceeds 18.5ms, the UART interface will automatically reset.

If the frame identification byte is incorrect or the checksum byte is incorrect, the frame data will be discarded.

UART module reset: The RX pin is pulled high after the low-level exceeds 6.65mS, and the UART module will be reset.

# 11. Package Information

#### SOP16L

#### SSOP20L

NOM MAX

1.75 0.25

1.50

0.70

0.31

0.24

6.20

4.00

0.80

8\*

0.20 0.21

# 12. Special Instructions

The company reserves the right of final interpretation of this specification.

## **Version Change Description**

Version: V1.03 Author: Lifeng Liu Time: 2021.9.09

Modify the record:

1. Re-typesetting the manual and checking some data

# Statement

The information in the usage specification is correct at the time of publication, Shanghai Siproin Microelectronics Co. has the right to change and interpret the specification, and reserves the right to modify the product without prior notice. Users can obtain the latest version information from our official website or other effective channels before confirmation, and verify whether the relevant information is complete and up to date.

With any semiconductor product, there is a certain possibility of failure or failure under certain conditions. The buyer is responsible for complying with safety standards and taking safety measures when using the product for system design and complete machine manufacturing. The product is not authorized to be used as a critical component in life-saving or life-sustaining products or systems, in order to avoid potential failure risks that may cause personal injury or property loss.