# Ultra-Low Power Integrated 300-510MHz Transceiver

# **General Description**

The RF64 is a low cost single-chip transceiver operating in the frequency ranges from 300MHz to 510MHz. The RF64 is optimized for very low power consumption (3mA in receiver mode). It incorporates a baseband modem with data rates up to 150 kb/s. Data handling features include a sixty-four byte FIFO, packet handling, automatic CRC generation and data whitening. Its highly integrated architecture allows for minimum external component count whilst maintaining design flexibility. All major RF communication parameters are programmable and most of them may be dynamically set. It complies with European (ETSI EN 300-220 V2.1.1) and North American (FCC part 15.247 and 15.249) regulatory standards.

# **Ordering Information**

Table 1: Ordering Information

| Part number | Delivery    | Minimum Order<br>Quantity / Multiple |

|-------------|-------------|--------------------------------------|

| RF64        | Tape & Reel | 3000 pieces                          |

- TQFN-32 package Operating range [-40;+85°C]

- Trefers to Lead Free packaging

- This device is WEEE and RoHS compliant

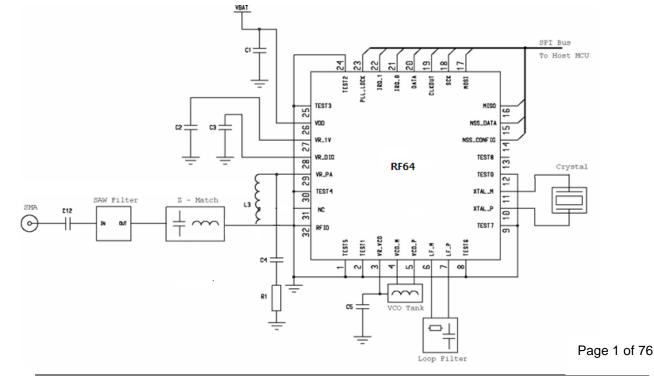

# **Application Circuit Schematic**

# Features

- Low Rx power consumption: 3mA

- Low Tx power consumption: 25 mA @ +10 dBm

- Good reception sensitivity: down to -104 dBm at 25 kb/s in FSK, -110 dBm at 2kb/s in OOK

- Programmable RF output power: up to +12.5 dBm in 8 steps

- Packet handling feature with data whitening and automatic CRC generation

- RSSI (Received Signal Strength Indicator)

- Bit rates up to 150 kb/s, NRZ coding

- On-chip frequency synthesizer

- FSK and OOK modulation

- Incoming sync word recognition

- Built-in Bit-Synchronizer for incoming data and clock synchronization and recovery

- 5 x 5 mm TQFN package

- Optimized Circuit Configuration for Low-cost applications

# Applications

- Wireless alarm and security systems

- Wireless sensor networks

- Automated Meter Reading

- Home and building automation

- Industrial monitoring and control

- Remote Wireless Control

- Active RFID PHY

# **Table of Contents**

| 1. General Description                       |

|----------------------------------------------|

| 1.1. Simplified Block Diagram5               |

| 1.2. Pin Diagram                             |

| 1.3. Pin Description7                        |

| 2. Electrical Characteristics                |

| 2.1. ESD Notice                              |

| 2.2. Absolute Maximum Ratings                |

| 2.3. Operating Range                         |

| 2.4. Chip Specification                      |

| 2.4.1. Power Consumption                     |

| 2.4.2. Frequency Synthesis                   |

| 2.4.3. Transmitter                           |

| 2.4.4. Receiver                              |

| 2.4.5. Digital Specification                 |

| 3. Architecture Description                  |

| 2.1 Dower Supply Strategy 12                 |

| 3.1. Power Supply Strategy                   |

| 3.2. Frequency Synthesis Description         |

| 3.2.1. Reference Oscillator                  |

| 3.2.2. CLKOUT Output                         |

| 3.2.3. PLL Architecture                      |

| 3.2.4. PLL Tradeoffs 14                      |

| 3.2.5. Voltage Controlled Oscillator15       |

| 3.2.6. PLL Loop Filter 16                    |

| 3.2.7. PLL Lock Detection Indicator          |

| 3.2.8. Frequency Calculation                 |

| 3.3. Transmitter Description                 |

| 3.3.1. Architecture Description              |

| 3.3.2. Bit Rate Setting                      |

| 3.3.3. Alternative Settings 19               |

| 3.3.4. Fdev Setting in FŠK Mode 19           |

| 3.3.5. Fdev Setting in OOK Mode              |

| 3.3.6. Interpolation Filter                  |

| 3.3.7. Power Amplifier                       |

| 3.3.8. Common Input and Output Front-End     |

| 3.4. Receiver Description                    |

| 3.4.1. Architecture                          |

| 3.4.2. LNA and First Mixer                   |

| 3.4.3. IF Gain and Second I/Q Mixer          |

| 3.4.4. Channel Filters                       |

| 3.4.5. Channel Filters Setting in FSK Mode   |

| 3.4.6. Channel Filters Setting in OOK Mode   |

|                                              |

| 3.4.7. RSSI                                  |

| 3.4.8. Fdev Setting in Receive Mode          |

| 3.4.9. FSK Demodulator                       |

| 3.4.10. OOK Demodulator                      |

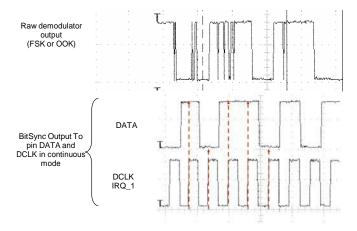

| 3.4.11. Bit Synchronizer                     |

| 3.4.12. Alternative Settings 32              |

| 3.4.13. Data Output 32                       |

| 4. Operating Modes                           |

| 4.1. Modes of Operation 33                   |

| 4.2. Digital Pin Configuration vs. Chip Mode |

| 5. Data Processing                           |

| 5.1. Overview                                |

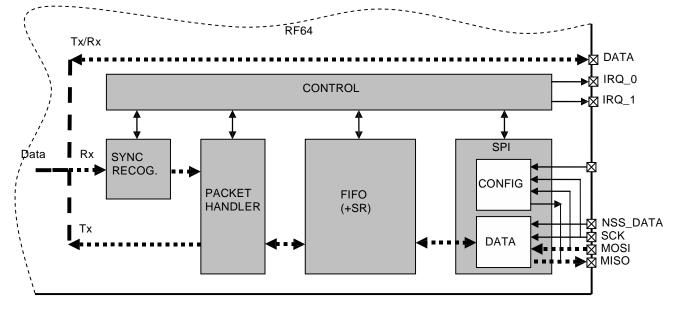

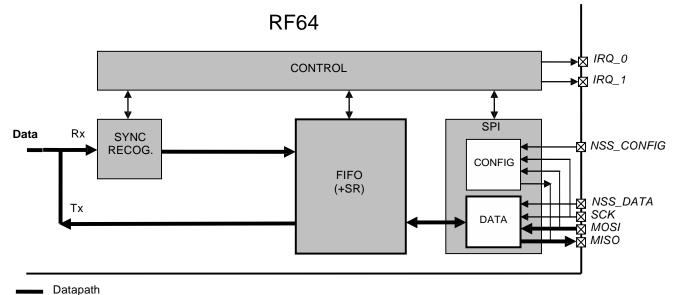

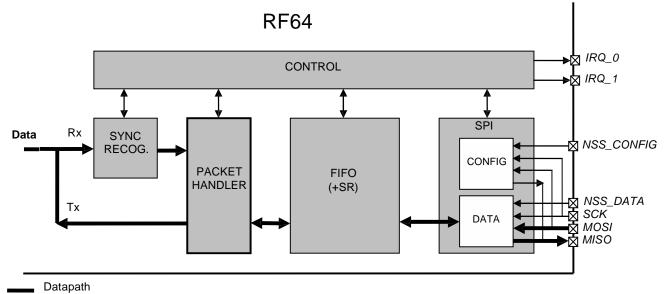

| 5.1.1. Block Diagram 34                      |

| 5.1.2. Data Operation Modes                  |

| 5.2. Control Block Description               |

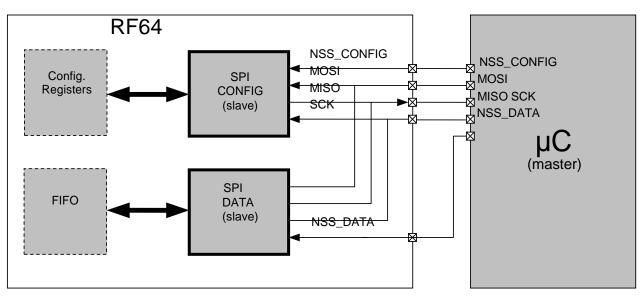

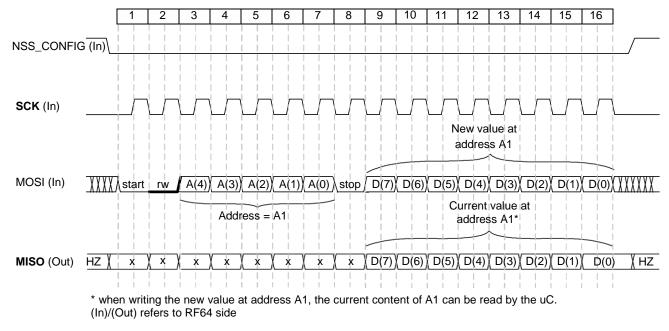

| 5.2.1. SPI Interface                         |

| 5.2.2. FIFO                                  |

| 5.2.3. Sync Word Recognition                 |

| 5.2.4. Packet Handler                        |

|                                              |

| 5.2.5. Control40                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

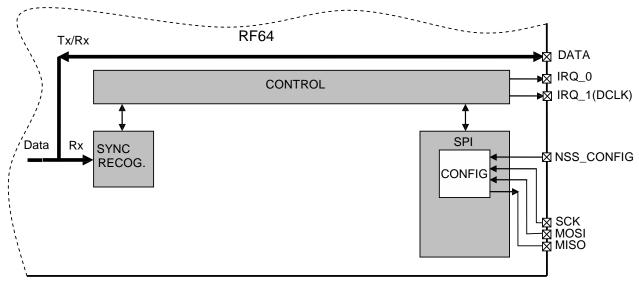

| 5.3. Continuous Mode41                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.3.1. General Description41                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.3.2. Tx Processing                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.3.3. Rx Processing                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.3.4. Interrupt Signals Mapping42                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.3.5. uC Connections                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.3.6. Continuous Mode Example                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.4. Buffered Mode                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.4.1. General Description44                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4.2. Tx Processing                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.4.3. Rx Processing                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.4.4. Interrupt Signals Mapping                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.4.5. uC Connections47                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.4.6. Buffered Mode Example47                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.5. Packet Mode                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.5.1. General Description49                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.5.2. Packet Format49                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.5.3. Tx Processing51                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.5.4. Rx Processing51                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.5.5. Packet Filtering52                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.5.6. DC-Free Data Mechanisms53                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.5.7. Interrupt Signal Mapping54                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5.8. uC Connections                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.5.9. Packet Mode Example56                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.5.10. Additional Information56                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6. Configuration and Status Registers                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.1. General Description                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.2. Main Configuration Register - MCParam                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.3. Interrupt Configuration Parameters - IRQParam                                                                                                                                                                                                                                                                                                                                                                               |

| 6.4. Receiver Configuration parameters - RXParam                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.5. Sync Word Parameters - SYNCParam                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.6. Transmitter Parameters - TXParam                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.7. Oscillator Parameters - OSCParam                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.8. Packet Handling Parameters – PKTParam                                                                                                                                                                                                                                                                                                                                                                                       |

| 7. Application Information                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.1. Crystal Resonator Specification                                                                                                                                                                                                                                                                                                                                                                                             |

| 7.2. Software for Frequency Calculation                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.2.1. GUI                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.2.2dll for Automatic Production Bench                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.3. Switching Times and Procedures                                                                                                                                                                                                                                                                                                                                                                                              |

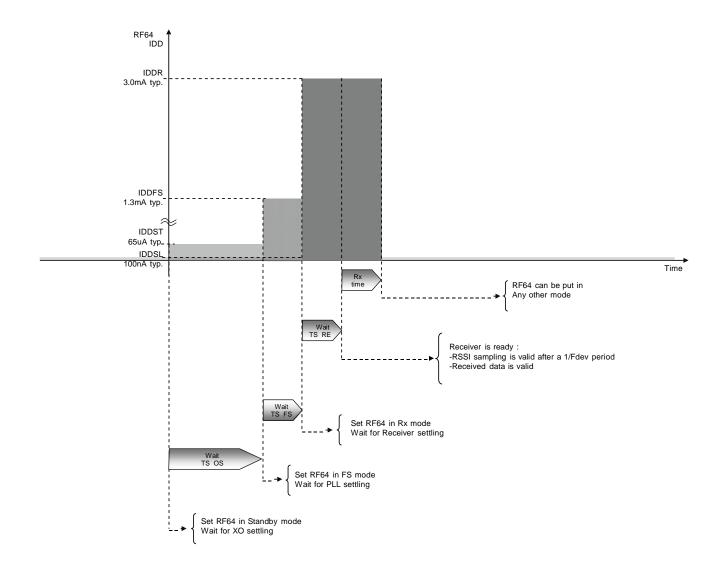

| 7.3.1. Optimized Receive Cycle                                                                                                                                                                                                                                                                                                                                                                                                   |

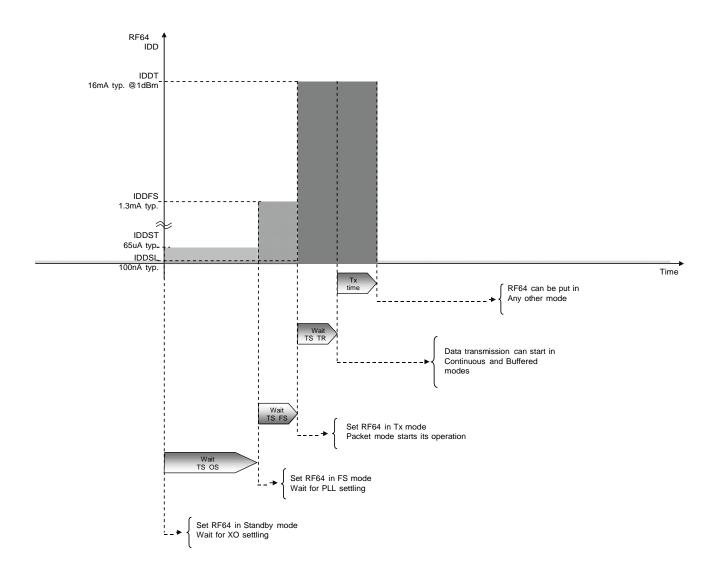

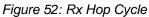

| 7.3.2. Optimized Transmit Cycle                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                  |

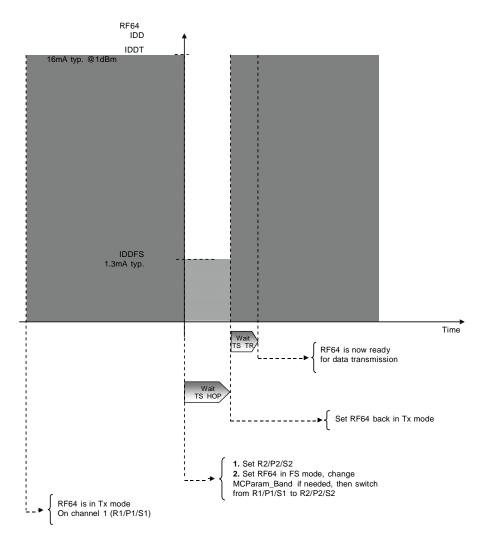

| 7.3.3. Transmitter Frequency Hop Optimized Cycle69                                                                                                                                                                                                                                                                                                                                                                               |

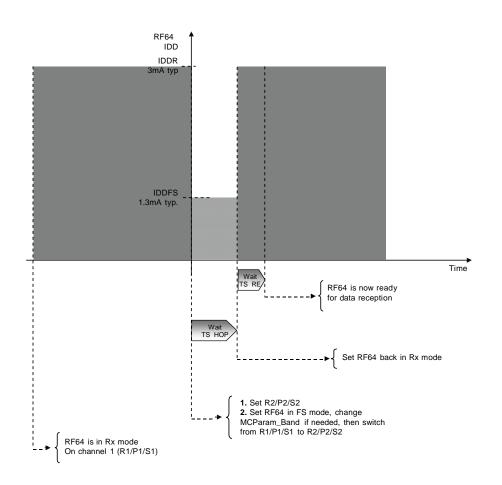

| 7.3.4. Receiver Frequency Hop Optimized Cycle                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.3.4. Receiver Frequency Hop Optimized Cycle70<br>7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles71                                                                                                                                                                                                                                                                                                                                        |

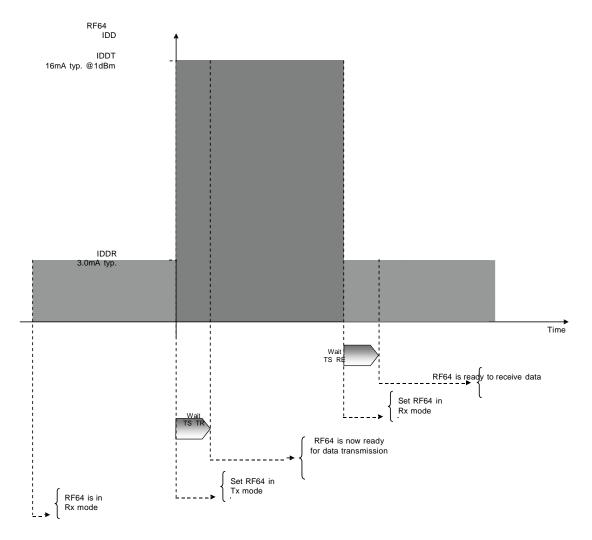

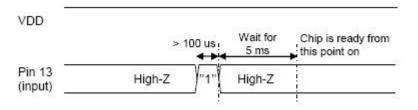

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72                                                                                                                                                                                                                                                                             |

| 7.3.4. Receiver Frequency Hop Optimized Cycle                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72                                                                                                                                                                                                            |

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72         7.5. Reference Design       73                                                                                                                                                                     |

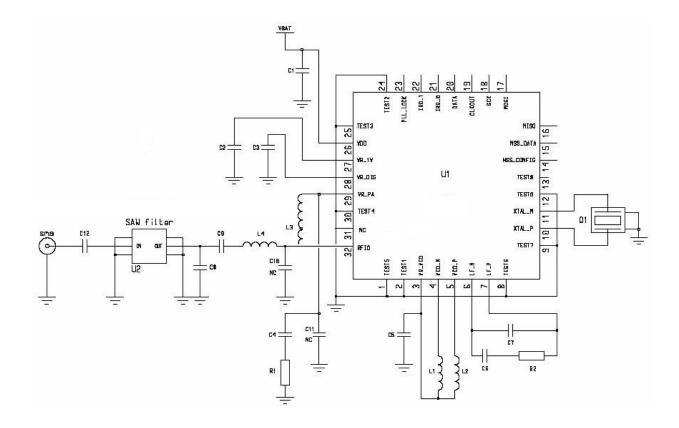

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72         7.5. Reference Design       73         7.5.1. Application Schematic       73                                                                                                                       |

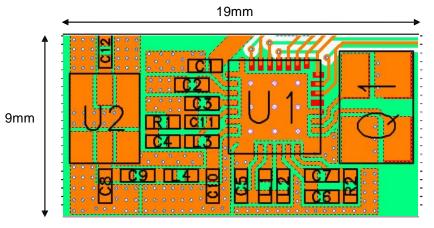

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72         7.5. Reference Design       73         7.5.1. Application Schematic       73         7.5.2. PCB Layout       73                                                                                    |

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72         7.5. Reference Design       73         7.5.1. Application Schematic       73                                                                                                                       |

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72         7.5. Reference Design       73         7.5.1. Application Schematic       73         7.5.2. PCB Layout       73         7.5.3. Bill Of Material       74                                           |

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72         7.5. Reference Design       73         7.5.1. Application Schematic       73         7.5.2. PCB Layout       73                                                                                    |

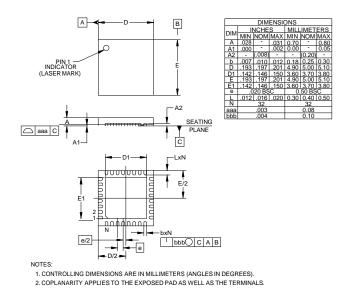

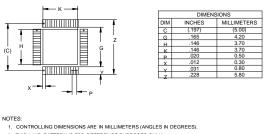

| 7.3.4. Receiver Frequency Hop Optimized Cycle       70         7.3.5. Rx=>Tx and Tx=>Rx Jump Cycles       71         7.4. Reset of the Chip       72         7.4.1. POR       72         7.4.2. Manual Reset       72         7.5. Reference Design       73         7.5.1. Application Schematic       73         7.5.2. PCB Layout       73         7.5.3. Bill Of Material       74         8. Packaging Information       75 |

| 7.3.4. Receiver Frequency Hop Optimized Cycle                                                                                                                                                                                                                                                                                                                                                                                    |

# **Index of Figures**

| Figure 1: RF64 Simplified Block Diagram               | 5  |

|-------------------------------------------------------|----|

| Figure 2: RF64 Pin Diagram                            |    |

| Figure 3: RF64 Detailed Block Diagram                 | 12 |

| Figure 4: Power Supply Breakdown                      |    |

| Figure 5: Frequency Synthesizer Description           | 14 |

| Figure 6: LO Generator                                | 14 |

| Figure 7: Loop Filter                                 | 16 |

| Figure 8: Transmitter Architecture                    |    |

| Figure 9: I(t), Q(t) Overview                         | 18 |

| Figure 10: PA Control                                 | 21 |

| Figure 11: Optimal Load Impedance Chart               |    |

| Figure 12: Recommended PA Biasing and Output Matching | 22 |

| Figure 13: Front-end Description                      |    |

| Figure 14: Receiver Architecture                      |    |

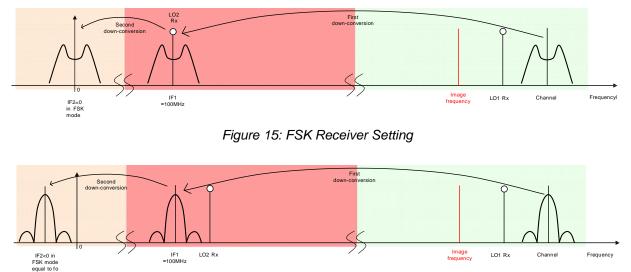

| Figure 15: FSK Receiver Setting                       |    |

| Figure 16: OOK Receiver Setting                       | 23 |

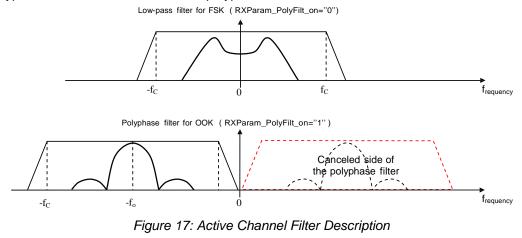

| Figure 17: Active Channel Filter Description          | 24 |

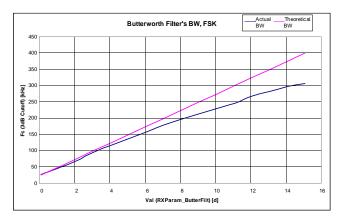

| Figure 18: Butterworth Filter's Actual BW             | 26 |

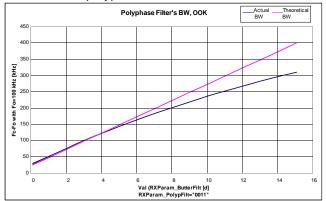

| Figure 19: Polyphase Filter's Actual BW               | 26 |

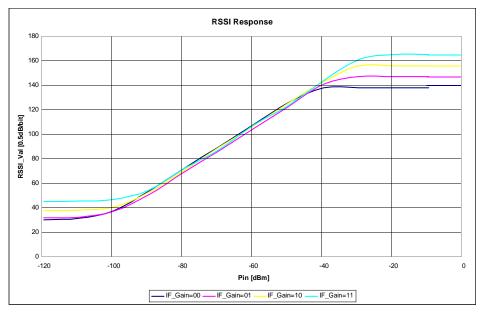

| Figure 20: RSSI Dynamic Range                         | 27 |

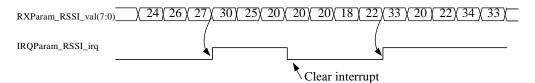

| Figure 21: RSSI IRQ Timings                           |    |

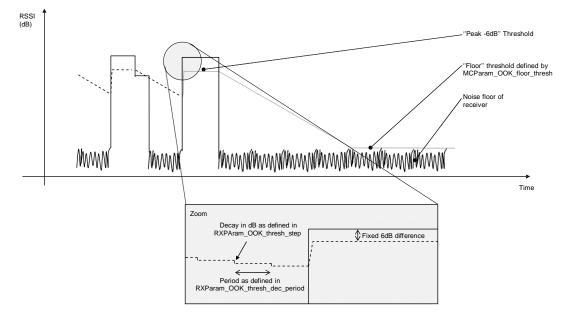

| Figure 22: OOK Demodulator Description                |    |

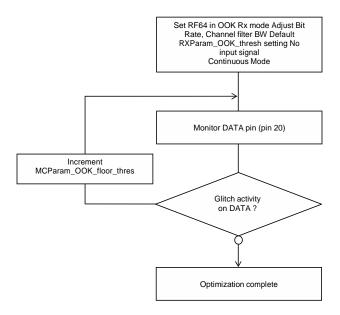

| Figure 23: Floor Threshold Optimization               |    |

| Figure 24: BitSync Description                        |    |

| Figure 25: RF64's Data Processing Conceptual View     |    |

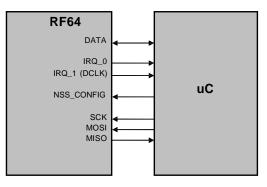

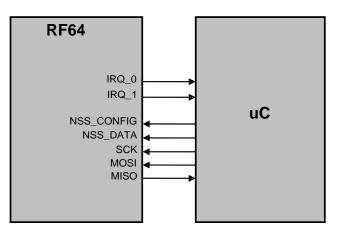

| Figure 26: SPI Interface Overview and uC Connections  |    |

| Figure 27: Write Register Sequence                    |    |

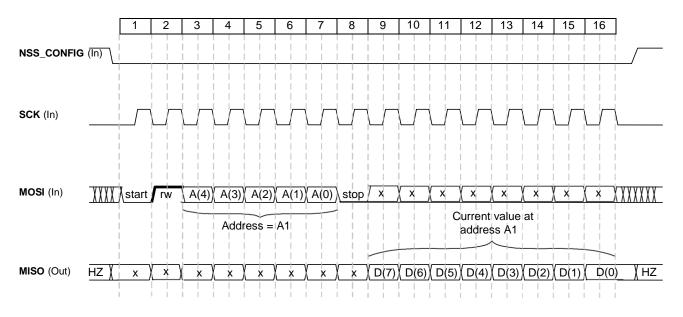

| Figure 28: Read Register Sequence                     |    |

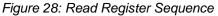

| Figure 29: Write Bytes Sequence (ex: 2 bytes)         |    |

| Figure 30: Read Bytes Sequence (ex: 2 bytes)          |    |

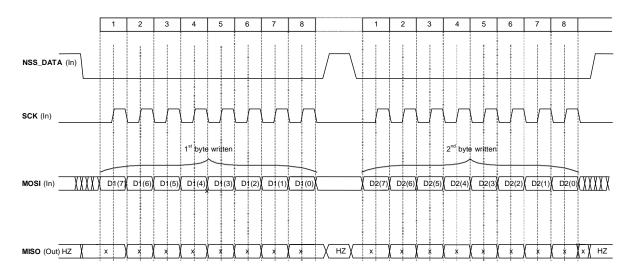

| Figure 31: FIFO and Shift Register (SR)               |    |

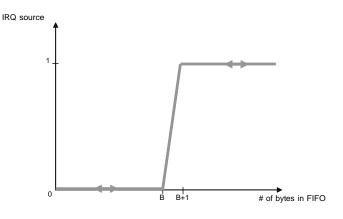

| Figure 32: FIFO Threshold IRQ Source Behavior         | 39 |

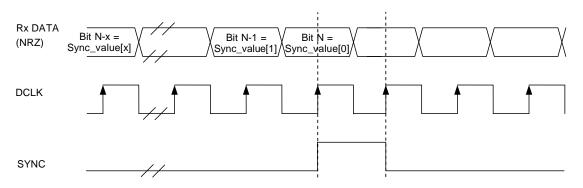

| Figure 33: Sync Word Recognition                           | 40 |

|------------------------------------------------------------|----|

| Figure 34: Continuous Mode Conceptual View                 |    |

| Figure 35: Tx Processing in Continuous Mode                |    |

| Figure 36: Rx Processing in Continuous Mode                |    |

| Figure 37: uC Connections in Continuous Mode               |    |

| Figure 38: Buffered Mode Conceptual View                   |    |

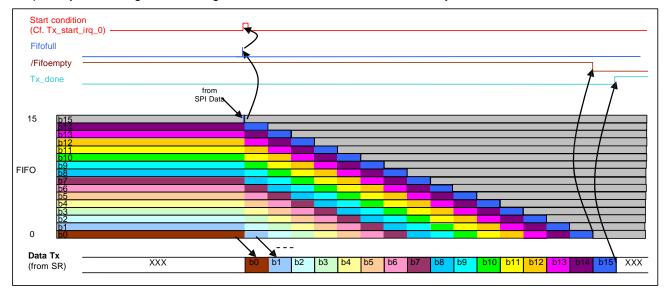

| Figure 39: Tx processing in Buffered Mode (FIFO size = 16, |    |

| Tx_start_irq_0=0)                                          | 45 |

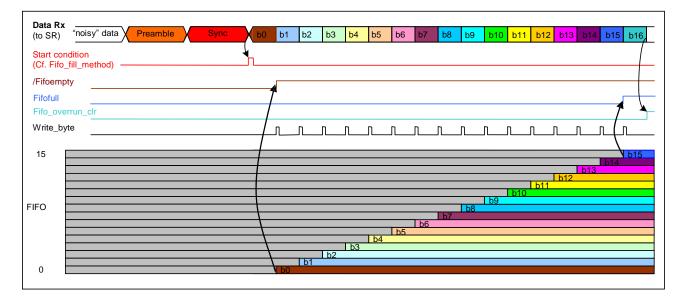

| Figure 40: Rx Processing in Buffered Mode (FIFO size=16,   |    |

| Fifo_fill_method=0)                                        | 46 |

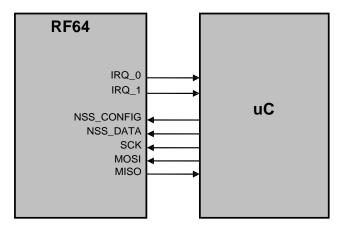

| Figure 41: uC Connections in Buffered Mode                 |    |

| Figure 42: Packet Mode Conceptual View                     | 49 |

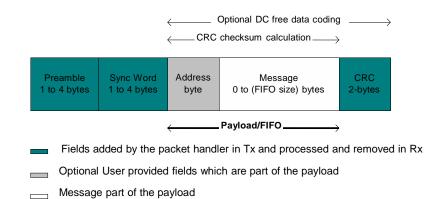

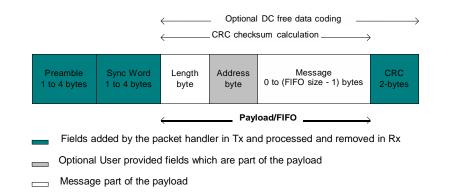

| Figure 43: Fixed Length Packet Format                      | 50 |

| Figure 44: Variable Length Packet Format                   |    |

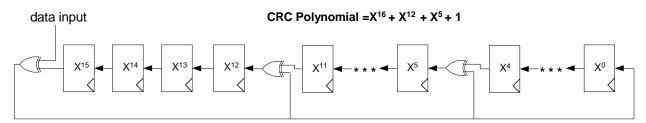

| Figure 45: CRC Implementation                              | 53 |

| Figure 46: Manchester Encoding/Decoding                    |    |

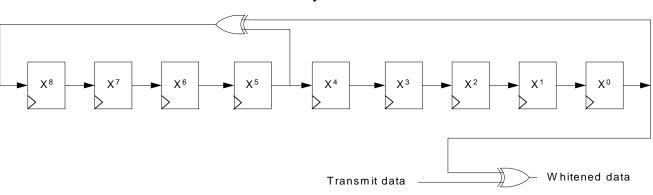

| Figure 47: Data Whitening                                  | 54 |

| Figure 48: uC Connections in Packet Mode                   | 55 |

| Figure 49: Optimized Rx Cycle                              |    |

| Figure 50: Optimized Tx Cycle                              | 68 |

| Figure 51: Tx Hop Cycle                                    |    |

| Figure 52: Rx Hop Cycle                                    | 70 |

| Figure 53: Rx => Tx => Rx Cycle                            | 71 |

| Figure 54: POR Timing Diagram                              |    |

| Figure 55: Manual Reset Timing Diagram                     |    |

| Figure 56: Reference Design Circuit Schematic              |    |

| Figure 57: Reference Design's Stackup                      | 74 |

| Figure 58: Reference Design Layout (top view)              | 74 |

| Figure 59: Package Outline Drawing                         |    |

| Figure 60: PCB Land Pattern                                | 75 |

# **Index of Tables**

| Table 1: Ordering Information                             | 1  |

|-----------------------------------------------------------|----|

| Table 2: RF64 Pinouts                                     | 7  |

| Table 3: Absolute Maximum Ratings                         | 8  |

| Table 4: Operating Range                                  | 8  |

| Table 5: Power Consumption Specification                  | 8  |

| Table 6: Frequency Synthesizer Specification              | 9  |

| Table 7: Transmitter Specification                        | 9  |

| Table 8: Receiver Specification                           |    |

| Table 9: Digital Specification                            |    |

| Table 10: MCParam_Freq_band Setting                       | 15 |

| Table 11: PA Rise/Fall Times                              | 20 |

| Table 12: Operating Modes                                 | 33 |

| Table 13: Pin Configuration vs. Chip Mode                 |    |

| Table 14: Data Operation Mode Selection                   | 35 |

| Table 15: Config vs. Data SPI Interface Selection         | 36 |

| Table 16: Status of FIFO when Switching Between Different |    |

| Modes of the Chip                                         | 39 |

| Table 17: Interrupt Mapping in Continuous Rx Mode         | 42 |

| Table 18: Interrupt Mapping in Continuous Tx Mode         |    |

# Acronyms

| BOM   | Bill Of Materials                                                       |

|-------|-------------------------------------------------------------------------|

| BR    | Bit Rate                                                                |

| BW    | Bandwidth                                                               |

| CCITT | Comité Consultatif International<br>Téléphonique et Télégraphique - ITU |

| CP    | Charge Pump                                                             |

| CRC   | Cyclic Redundancy Check                                                 |

| DAC   | Digital to Analog Converter                                             |

| DDS   | Direct Digital Synthesis                                                |

| DLL   | Dynamically Linked Library                                              |

| ERP   | Equivalent Radiated Power                                               |

| ETSI  | European Telecommunications Standards<br>Institute                      |

| FCC   | Federal Communications Commission                                       |

| Fdev  | Frequency Deviation                                                     |

| FIFO  | First In First Out                                                      |

| FS    | Frequency Synthesizer                                                   |

| FSK   | Frequency Shift Keying                                                  |

| GUI   | Graphical User Interface                                                |

| IC    | Integrated Circuit                                                      |

| ID    | IDentificator                                                           |

| IF    | Intermediate Frequency                                                  |

| IRQ   | Interrupt ReQuest                                                       |

| ITU   | International Telecommunication Union                                   |

| LFSR  | Linear Feedback Shift Register                                          |

| LNA   | Low Noise Amplifier                                                     |

| Table 19: Relevant Configuration Registers in Continuous Mod   |      |

|----------------------------------------------------------------|------|

| (data processing related only)                                 | 43   |

| Table 20: Interrupt Mapping in Buffered Rx and Stby Modes      | 46   |

| Table 21: Interrupt Mapping in Tx Buffered Mode                | 46   |

| Table 22: Relevant Configuration Registers in Buffered Mode (d | data |

| processing related only)                                       | 47   |

| Table 23: Interrupt Mapping in Rx and Stby in Packet Mode      | 55   |

| Table 24: Interrupt Mapping in Tx Packet Mode                  | 55   |

| Table 25: Relevant Configuration Registers in Packet Mode (da  |      |

| processing related only)                                       | 56   |

| Table 26: Registers List                                       |      |

| Table 27: MCParam Register Description                         |      |

| Table 28: IRQParam Register Description                        | 60   |

| Table 29: RXParam Register Description                         | 62   |

| Table 30: SYNCParam Register Description                       | 63   |

| Table 31: TXParam Register Description                         | 64   |

| Table 32: OSCParam Register Description                        | 64   |

| Table 33: PKTParam Register Description                        | 65   |

| Table 34: Crystal Resonator Specification                      | 66   |

| Table 35: Reference Design BOM                                 |      |

| LO   | Local Oscillator                   |

|------|------------------------------------|

| LSB  | Least Significant Bit              |

| MSB  | Most Significant Bit               |

| NRZ  | Non Return to Zero                 |

| NZIF | Near Zero Intermediate Frequency   |

| OOK  | On Off Keying                      |

| PA   | Power Amplifier                    |

| PCB  | Printed Circuit Board              |

| PFD  | Phase Frequency Detector           |

| PLL  | Phase-Locked Loop                  |

| POR  | Power On Reset                     |

| RBW  | Resolution BandWidth               |

| RF   | Radio Frequency                    |

| RSSI | Received Signal Strength Indicator |

| Rx   | Receiver                           |

| SAW  | Surface Acoustic Wave              |

| SPI  | Serial Peripheral Interface        |

| SR   | Shift Register                     |

| Stby | Standby                            |

| Tx   | Transmitter                        |

| uC   | Microcontroller                    |

| VCO  | Voltage Controlled Oscillator      |

| XO   | Crystal Oscillator                 |

| XOR  | eXclusive OR                       |

This product datasheet contains a detailed description of the RF64 performance and functionality.

# **1. General Description**

The RF64 is a single chip FSK and OOK transceiver capable of operation in the 300 to 510MHz license free ISM frequency bands. It complies with both the relevant European and North American standards, EN 300-220 V2.1.1 (June 2006 release) and FCC Part 15 (10-1-2006 edition). A unique feature of this circuit is its extremely low current consumption in receiver mode of only 3mA (typ).

The RF64 comes in a 5x5 mm TQFN-32 package.

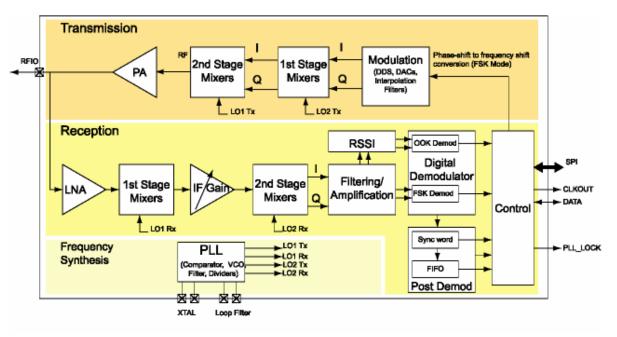

# 1.1. Simplified Block Diagram

Figure 1: RF64 Simplified Block Diagram

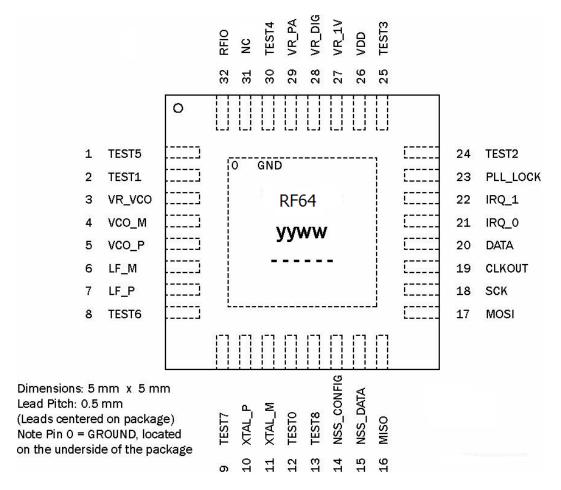

# 1.2. Pin Diagram

The following diagram shows the pins arrangement of the QFN package, top view.

Figure 2: RF64 Pin Diagram

Notes:

- yyww refers to the date code

- ----- refers to the lot number

Page 6 of 76

# 1.3. Pin Description

Table 2: RF64 Pinouts

| Number | Name       | Туре | Description                                 |

|--------|------------|------|---------------------------------------------|

| 0      | GND        | I    | Exposed ground pad                          |

| 1      | TEST5      | I/O  | Connect to GND                              |

| 2      | TEST1      | I/O  | Connect to GND                              |

| 3      | VR_VCO     | 0    | Regulated supply of the VCO                 |

| 4      | VCO_M      | I/O  | VCO tank                                    |

| 5      | VCO_P      | I/O  | VCO tank                                    |

| 6      | LF_M       | I/O  | PLL loop filter                             |

| 7      | LF_P       | I/O  | PLL loop filter                             |

| 8      | TEST6      | I/O  | Connect to GND                              |

| 9      | TEST7      | I/O  | Connect to GND                              |

| 10     | XTAL_P     | I/O  | Crystal connection                          |

| 11     | XTAL_M     | I/O  | Crystal connection                          |

| 12     | TEST0      | l    | Connect to GND                              |

| 13     | TEST8      | I/O  | POR. Do not connect if unused               |

| 14     | NSS_CONFIG | I    | SPI CONFIG enable                           |

| 15     | NSS_DATA   | l    | SPI DATA enable                             |

| 16     | MISO       | 0    | SPI data output                             |

| 17     | MOSI       | l    | SPI data input                              |

| 18     | SCK        | I    | SPI clock input                             |

| 19     | CLKOUT     | 0    | Clock output                                |

| 20     | DATA       | I/O  | NRZ data input and output (Continuous mode) |

| 21     | IRQ_0      | 0    | Interrupt output                            |

| 22     | IRQ_1      | 0    | Interrupt output                            |

| 23     | PLL_LOCK   | 0    | PLL lock detection output                   |

| 24     | TEST2      | 0    | No connect                                  |

| 25     | TEST3      | I/O  | Connect to GND                              |

| 26     | VDD        | I    | Supply voltage                              |

| 27     | VR_1V      | 0    | Regulated supply of the analog circuitry    |

| 28     | VR_DIG     | 0    | Regulated supply of digital circuitry       |

| 29     | VR_PA      | 0    | Regulated supply of the PA                  |

| 30     | TEST4      | I/O  | Connect to GND                              |

| 31     | NC         | -    | Connect to GND                              |

| 32     | RFIO       | I/O  | RF input/output                             |

Note: pin 13 (Test 8) can be used as a manual reset trigger. See section 7.4.2 for details on its use.

# 2. Electrical Characteristics

# 2.1. ESD Notice

The RF64 is a high performance radio frequency device. It satisfies:

- Class 2 of the JEDEC standard JESD22-A114-B (Human Body Model), except on pins 3-4-5-27-28-29-32 where it satisfies Class 1A.

- Class III of the JEDEC standard JESD22-C101C (Charged Device Model) on all pins. It should thus be handled with all the necessary ESD precautions to avoid any permanent damage.

# 2.2. Absolute Maximum Ratings

Stresses above the values listed below may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

Table 3: Absolute Maximum Ratings

| Symbol | Description         | Min  | Max | Unit |

|--------|---------------------|------|-----|------|

| VDDmr  | Supply voltage      | -0.3 | 3.7 | V    |

| Tmr    | Storage temperature | -55  | 125 | °C   |

| Pmr    | Input level         | -    | 0   | dBm  |

# 2.3. Operating Range

Table 4: Operating Range

| Symbol | Description    | Min | Max | Unit |

|--------|----------------|-----|-----|------|

| VDDop  | Supply Voltage | 2.1 | 3.6 | V    |

| Trop   | Temperature    | -40 | +85 | °C   |

| ML     | Input Level    | -   | 0   | dBm  |

# 2.4. Chip Specification

Conditions: Temp = 25 °C, VDD = 3.3 V, crystal frequency = 12.8 MHz, carrier frequency = 434 MHz, modulation FSK, data rate = 25 kb/s, Fdev = 50 kHz, fc = 100 kHz, unless otherwise specified.

## 2.4.1. Power Consumption

| Symbol | Description                                        | Conditions                                                              | Min | Тур | Max | Unit |

|--------|----------------------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| IDDSL  | Supply current in sleep mode                       |                                                                         | -   | 0.1 | 2   | μA   |

| IDDST  | Supply current in standby<br>mode, CLKOUT disabled | Crystal oscillator running                                              | -   | 65  | 85  | μA   |

| IDDFS  | Supply current in FS mode                          | Frequency synthesizer<br>running                                        | -   | 1.3 | 1.7 | mA   |

| IDDR   | Supply current in receiver<br>mode                 |                                                                         | -   | 3.0 | 3.5 | mA   |

| IDDT   | Supply current in                                  | Output power = $+10 \text{ dBm}$<br>Output power = $1 \text{dBm}^{(1)}$ | -   | 25  | 30  | mA   |

|        | transmitter mode                                   | Output power = 1dBm <sup>(1)</sup>                                      | -   | 16  | 21  | mA   |

<sup>(1)</sup> Guaranteed by design and characterization

Page 8 of 76

# 2.4.2. Frequency Synthesis

Table 6: Frequency Synthesizer Specification

| Symbol | Description                                                                     | Conditions                            | Min  | Тур  | Max | Unit |

|--------|---------------------------------------------------------------------------------|---------------------------------------|------|------|-----|------|

|        |                                                                                 |                                       | 300  | -    | 330 | MHz  |

|        |                                                                                 |                                       | 320  | -    | 350 | MHz  |

| FR     | Frequency ranges                                                                | Programmable ,                        | 350  | -    | 390 | MHz  |

|        | Thequency ranges                                                                | (may require specific BOM)            | 390  | -    | 430 | MHz  |

|        |                                                                                 |                                       | 430  | -    | 470 | MHz  |

|        |                                                                                 |                                       | 470  | -    | 510 | MHz  |

| BR_F   | Bit rate (FSK)                                                                  | NRZ                                   | 0.78 | -    | 150 | Kb/s |

| BR_O   | Bit rate (OOK)                                                                  | NRZ                                   | 0.78 | -    | 32  | Kb/s |

| FDA    | Frequency deviation (FSK)                                                       |                                       | 33   | 50   | 200 | kHz  |

| XTAL   | Crystal oscillator frequency                                                    |                                       | 9    | 12.8 | 15  | MHz  |

| FSTEP  | Frequency synthesizer<br>step                                                   | Variable, depending on the frequency. | -    | 2    | -   | kHz  |

| TS_OSC | Oscillator wake-up time                                                         | From Sleep mode <sup>(1)</sup>        | -    | 1.5  | 5   | ms   |

| TS_FS  | Frequency synthesizer<br>wake-up time at most<br>10 kHz away from the<br>target | From Stby mode                        | -    | 500  | 800 | μs   |

|        |                                                                                 | 200 kHz step                          | -    | 180  | -   | μs   |

|        |                                                                                 | 1 MHz step                            | -    | 200  | -   | μs   |

|        | Frequency synthesizer hop                                                       | 5 MHz step                            | -    | 250  | -   | μs   |

| TS_HOP | time at most 10 kHz away                                                        | 7 MHz step                            | -    | 260  | -   | μs   |

|        | from the target                                                                 | 12 MHz step                           | -    | 290  | -   | μs   |

|        |                                                                                 | 20 MHz step                           | -    | 320  | -   | μs   |

|        |                                                                                 | 27 MHz step                           | -    | 340  | -   | μs   |

<sup>(1)</sup>Guaranteed by design and characterization

# 2.4.3. Transmitter

Table 7: Transmitter Specification

| Symbol                | Description                              | Conditions                                                                              | Min | Тур   | Max | Unit   |

|-----------------------|------------------------------------------|-----------------------------------------------------------------------------------------|-----|-------|-----|--------|

| RFOP                  | RF output power,                         | Maximum power setting                                                                   | -   | +12.5 | -   | dBm    |

| RFUP                  | programmable with 8 steps<br>of typ. 3dB | Minimum power setting                                                                   | -   | -8.5  | -   | dBm    |

| PN                    | Phase noise                              | Measured with a 600 kHz<br>offset, at the transmitter<br>output.                        | -   | -112  | -   | dBc/Hz |

| SPT                   | Transmitted spurious                     | At any offset between<br>200 kHz and 600 kHz,<br>unmodulated carrier, Fdev<br>= 50 kHz. | -   | -     | -47 | dBc    |

| TS_TR <sup>(1)</sup>  | Transmitter wake-up time                 | From FS to Tx ready.                                                                    | -   | 120   | 500 | μs     |

| TS_TR2 <sup>(1)</sup> | Transmitter wake-up time                 | From Stby to Tx ready.                                                                  | -   | 600   | 900 | μs     |

<sup>(1)</sup>Guaranteed by design and characterization

Page 9 of 76

### 2.4.4. Receiver

On the following table, fc and fo describe the bandwidth of the active channel filters as described in section 3.4.4.2. All sensitivities are measured receiving a PN15 sequence, for a BER of 0.1.%

Table 8: Receiver Specification

| Symbol                  | Description                             | Conditions                                       | Min | Тур  | Max    | Unit  |

|-------------------------|-----------------------------------------|--------------------------------------------------|-----|------|--------|-------|

| -                       |                                         | 434 MHz, BR=25 kb/s, Fdev<br>=50 kHz, fc=100 kHz | -   | -104 | -      | dBm   |

| RFS_F                   | Sensitivity (FSK)                       |                                                  | -   | -    | -      |       |

|                         | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                  | -   | -    | -      |       |

|                         |                                         |                                                  | -   | -    | -      |       |

|                         |                                         | 434 MHz, 2kb/s NRZ<br>fc-fo=50 kHz, fo=50 kHz    | -   | -110 | -      | dBm   |

| RFS_O                   | Sensitivity (OOK)                       |                                                  | -   | -    | -      |       |

|                         |                                         |                                                  | -   | -    | -      |       |

|                         |                                         |                                                  | -   | -    | -      |       |

| CCR                     | Co-channel rejection                    | Modulation as wanted signal                      | -   | -12  | -      | dBc   |

|                         | Adjacent channel                        | Offset = 300 kHz                                 | -   | -    | -      | dB    |

| ACR                     | rejection                               | Offset = 600 kHz                                 | -   | 42   | -      | dB    |

|                         | Tejection                               | Offset = 1.2 MHz                                 | -   | 53   | -      | dB    |

|                         | Blocking immunity                       | Offset = 1 MHz,                                  | _   | 53   | -      | dBc   |

|                         |                                         | unmodulated                                      | -   | - 55 | -      | UDC   |

| BI                      |                                         | Offset = 2 MHz,                                  | -   | _    | _      |       |

| Ы                       |                                         | unmodulated, no SAW                              | _   | -    | -      |       |

|                         |                                         | Offset = 10 MHz,                                 | -   | -    | -      |       |

|                         |                                         | unmodulated, no SAW                              | _   | _    | _      |       |

| RXBW F <sup>(1,2)</sup> | Receiver bandwidth in                   | Single side BW                                   | 50  | -    | 250    | kHz   |

|                         | FSK mode                                | Polyphase Off                                    | 00  |      | 200    | 1012  |

| RXBW_O <sup>(1,2)</sup> | Receiver bandwidth in                   | Single side BW                                   | 50  | 50 - | 400    | kHz   |

| 10/211_0                | OOK mode                                | Polyphase On                                     | 00  |      | 100    | 14.12 |

| IIP3                    | Input 3 <sup>rd</sup> order intercept   | Interferers at 1MHz and                          | -   | -28  | -      | dBm   |

|                         | point                                   | 1.950 MHz offset                                 |     | _    |        |       |

| TS_RE <sup>(1)</sup>    | Receiver wake-up time                   | From FS to Rx ready                              | -   | 280  | 500    | μs    |

| TS_RE2 <sup>(1)</sup>   | Receiver wake-up time                   | From Stby to Rx ready                            | -   | 600  | 900    | μs    |

|                         |                                         | 200 kHz step                                     | -   | 400  | -      | μs    |

|                         |                                         | 1MHz step                                        | -   | 400  | -      | μs    |

|                         | Receiver hop time from                  | 5MHz step                                        | -   | 460  | -      | μs    |

| TS_RE_HOP               | Rx ready to Rx ready with               | 7MHz step                                        | -   | 480  | -      | μs    |

|                         | a frequency hop                         | 12MHz step                                       | -   | 520  | -      | μs    |

|                         |                                         | 20MHz step                                       | -   | 550  | -      | μs    |

|                         |                                         | 27MHz step                                       | -   | 600  | -      | μs    |

| TS_RSSI                 | RSSI sampling time                      | From Rx ready                                    | -   | -    | 1/Fdev | S     |

| DR_RSSI                 | RSSI dynamic Range                      | Ranging from sensitivity                         | -   | 70   | -      | dB    |

<sup>(1)</sup> Information from design and characterization <sup>(2)</sup> This reflects the whole receiver bandwidth, as described in sections 3.4.4.1 and 3.4.4.2

# 2.4.5. Digital Specification

Conditions: Temp = 25 °C, VDD = 3.3 V, crystal frequency = 12.8 MHz, unless otherwise specified.

Table 9: Digital Specification

| Symbol     | Description                                                                | Conditions | Min     | Тур | Max     | Unit |

|------------|----------------------------------------------------------------------------|------------|---------|-----|---------|------|

| VIH        | Digital input level high                                                   |            | 0.8*VDD | -   | -       | V    |

| VIL        | Digital input level low                                                    |            | -       | -   | 0.2*VDD | V    |

| VOH        | Digital output level high                                                  | Imax=1mA   | 0.9*VDD | -   | -       | V    |

| VOL        | Digital output level low                                                   | Imax=-1mA  | -       | -   | 0.1*VDD | V    |

| SCK_CONFIG | SPI Config. clock frequency                                                |            | -       | -   | 6       | MHz  |

| SCK_DATA   | SPI data clock frequency                                                   |            | -       | -   | 1       | MHz  |

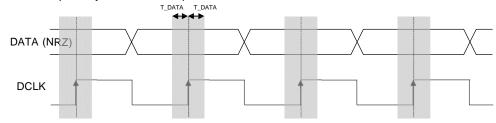

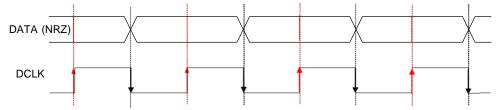

| T_DATA     | DATA hold and setup time                                                   |            | 2       | -   | -       | μs   |

| T_MOSI_C   | MOSI setup time for SPI Config.                                            |            | 250     | -   | -       | ns   |

| T_MOSI_D   | MOSI setup time for SPI Data.                                              |            | 312     | -   | -       | ns   |

| T_NSSC_L   | NSS_CONFIG low to SCK rising edge.<br>SCK falling edge to NSS_CONFIG high. |            | 500     | -   | -       | ns   |

| T_NSSD_L   | NSS_DATA low to SCK rising edge.<br>SCK falling edge to NSS_DATA high.     |            | 625     | -   | -       | ns   |

| T_NSSC_H   | NSS_CONFIG rising to falling edge.                                         |            | 500     | -   | -       | ns   |

| T_NSSD_H   | NSS_DATA rising to falling edge.                                           |            | 625     | -   | -       | ns   |

Note: on pin 10 (XTAL\_P) and 11 (XTAL\_N), maximum voltages of 1.8V can be applied.

# 3. Architecture Description

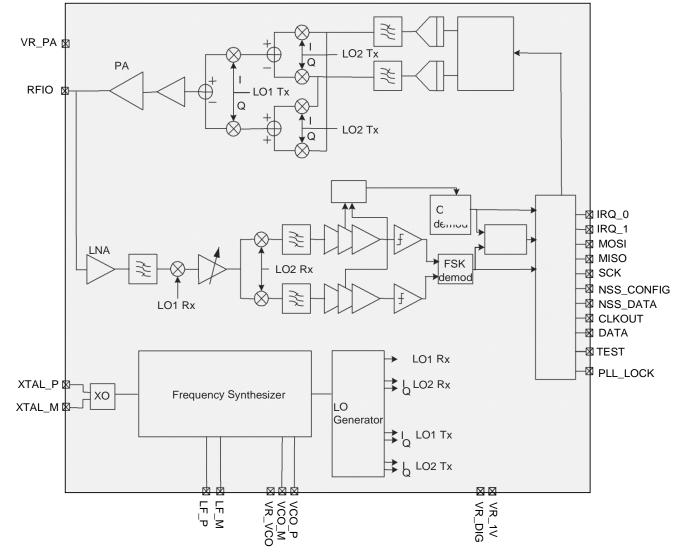

This section describes in depth the architecture of this ultra low-power transceiver:

Figure 3: RF64 Detailed Block Diagram

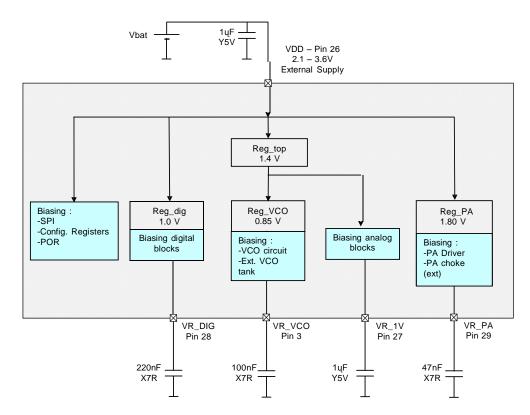

# 3.1. Power Supply Strategy

To provide stable sensitivity and linearity characteristics over a wide supply range, the RF64 is internally regulated. This internal regulated power supply structure is described below:

Figure 4: Power Supply Breakdown

To ensure correct operation of the regulator circuit, the decoupling capacitor connection shown in Figure 4 is required. These decoupling components are recommended for any design.

# 3.2. Frequency Synthesis Description

The frequency synthesizer of the RF64 is a fully integrated integer-N type PLL. The PLL circuit requires only five external components for the PLL loop filter and the VCO tank circuit.

## 3.2.1. Reference Oscillator

The RF64 embeds a crystal oscillator, which provides the reference frequency for the PLL. The recommended crystal specification is given in section 7.1.

## 3.2.2. CLKOUT Output

The reference frequency, or a sub-multiple of it, can be provided on CLKOUT (pin 19) by activating the bit OSCParam\_Clkout\_on. The division ratio is programmed through bits OSCParam\_Clkout\_freq. The two applications of the CLKOUT output are:

- To provide a clock output for a companion uC, thus saving the cost of an additional oscillator. CLKOUT can be made available in any operation mode, except Sleep mode, and is automatically enabled at power-up.

- To provide an oscillator reference output. Measurement of the CLKOUT signal enables simple software trimming of the initial crystal tolerance.

Note: To minimize the current consumption of the RF64, ensure that the CLKOUT signal is disabled when unused.

Page 13 of 76

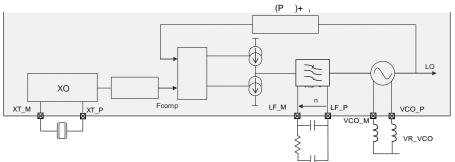

## 3.2.3. PLL Architecture

The crystal oscillator (XO) forms the reference oscillator of an Integer-N Phase Locked Loop (PLL), whose operation is discussed in the following section. Figure 5 shows a block schematic of the RF64 PLL. Here the crystal reference frequency and the software controlled dividers R, P and S determine the output frequency of the PLL.

Figure 5: Frequency Synthesizer Description

The VCO tank inductors are connected on an external differential input. Similarly, the loop filter is also located externally. However, there is an internal 8pF capacitance at VCO input that should be subtracted from the desired loop filter capacitance.

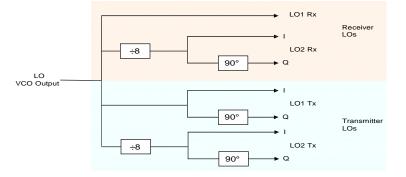

The output signal of the VCO is used as the input to the local oscillator (LO) generator stage, illustrated in Figure 6. The VCO frequency is subdivided and used in a series of up (down) conversions for transmission (reception).

Figure 6: LO Generator

## 3.2.4. PLL Tradeoffs

With an integer-N PLL architecture, the following criterion must be met to ensure correct operation:

The comparison frequency, Fcomp, of the Phase Frequency Detector (PFD) input must remain higher than six times the PLL bandwidth (PLLBW) to guarantee loop stability and to reject harmonics of the comparison frequency Fcomp. This is expressed in the inequality:

$$PLLBW \leq \frac{Fcomp}{6}$$

- However the PLLBW has to be sufficiently high to allow adequate PLL lock times

- Because the divider ration R determines Fcomp, it should be set close to 119, leading to Fcomp≈100 kHz which will ensure suitable PLL stability and speed.

With the recommended Bill Of Materials (BOM) of the reference design of section 7.5.3, the PLL prototype is the following:

- 64 ≤ R ≤ 169

- S < P+1

- LLBW = 15 kHz nominal

- Startup times and reference frequency spurs as specified.

## 3.2.5. Voltage Controlled Oscillator

The integrated VCO requires only two external tank circuit inductors. As the input is differential, the two inductors should have the same nominal value. The performance of these components is important for both the phase noise and the power consumption of the PLL. It is recommended that a pair of high Q factor inductors is selected. These should be mounted orthogonally to other inductors (in particular the PA choke) to reduce spurious coupling between the PA and VCO. In addition, such measures may reduce radiated pulling effects and undesirable transient behavior, thus minimizing spectral occupancy. Note that ensuring a symmetrical layout of the VCO inductors will further improve PLL spectral purity.

For best performance wound type inductors, with tight tolerance, should be used as described in section 7.5.3.

#### 3.2.5.1. SW Settings of the VCO

To guarantee the optimum operation of the VCO over the RF64's frequency and temperature ranges, the following settings should be programmed into the RF64:

| Target channel | 300- | 320- | 350- | 390- | 430- | 470- |

|----------------|------|------|------|------|------|------|

| (MHz)          | 330  | 350  | 390  | 430  | 470  | 510  |

| Freq_band      | 000  | 001  | 010  | 011  | 100  | 101  |

Table 10: MCParam\_Freq\_band Setting

#### 3.2.5.2. Trimming the VCO Tank by Hardware and Software

To ensure that the frequency band of operation may be accurately addressed by the R, P and S dividers of the synthesizer, it is necessary to ensure that the VCO is correctly centered. Note that for the reference design (see section 7.5) no centering is necessary. However, any deviation from the reference design may require the optimization procedure, outlined below, to be implemented. This procedure is simplified thanks to the built-in VCO trimming feature which is controlled over the SPI interface. This tuning does not require any RF test equipment, and can be achieved by simply measuring Vtune, the voltage between pins 6 (LFM) and 7 (LFP).

The VCO is centered if the voltage is within the range:

$100 \leq V tune(mV) \leq 200$

Note that this measurement should be conducted when in transmit mode at the center frequency of the desired band (for example ~315 MHz in the 300-330 MHz band), with the appropriate MCParam\_Freq\_band setting.

If this inequality is not satisfied then adjust the MCParam\_VCO\_trim bits from 00 whilst monitoring Vtune. This allows the VCO voltage to be trimmed in + 60 mV increments. Should the desired voltage range be inaccessible, the voltage may be adjusted further by changing the tank circuit inductance value. Note that an increase in inductance will result in an increase Vtune.

Page 15 of 76

<u>Note for mass production</u>: The VCO capacitance is piece to piece dependant. As such, the optimization proposed above should be verified on several prototypes, to ensure that the population is centered on 150 mV.

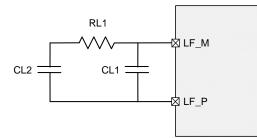

## 3.2.6. PLL Loop Filter

To adequately reject spurious components arising from the comparison frequency Fcomp, an external 2<sup>nd</sup> order loop filter is employed.

Figure 7: Loop Filter

Following the recommendations made in section 3.2.4, the loop filter proposed in the reference design's bill of material on section 7.5.3 should be used. The loop filter settings are frequency band independent and are hence relevant to all implementations of the RF64.

### 3.2.7. PLL Lock Detection Indicator

The RF64 also features a PLL lock detect indicator. This is useful for optimizing power consumption, by adjusting the synthesizer wake up time (TS\_FS), since the PLL startup time is lower than specified under nominal conditions. The lock status can be read on bit IRQParam\_PLL\_lock, and must be cleared by writing a "1" to this same register. In addition, the lock status can be reflected in pin 23 PLL\_LOCK, by setting the bit IRQParam\_Enable\_lock\_detect.

## 3.2.8. Frequency Calculation

As shown in Figure 5 the PLL structure comprises three different dividers, R, P and S, which set the output frequency through the LO. A second set of dividers is also available to allow rapid switching between a pair of frequencies: R1/P1/S1 and R2/P2/S2. These six dividers are programmed by six bytes of the register MCParam from addresses 6 to 11.

#### 3.2.8.1. FSK Mode

The following formula gives the relationship between the local oscillator, and R, P and S values, when using FSK modulation.

$$Frf, fsk = \frac{9}{8}Flo$$

$$Frf, fsk = \frac{9 Fxtal}{8 R+1} [75(P+1)+S)]$$

#### 3.2.8.2. OOK Mode

Due to the manner in which the baseband OOK symbols are generated, the signal is always offset by the FSK frequency deviation (Fdev - as programmed in MCParam\_Freq\_dev). Hence, the center of the transmitted OOK signal is:

Page 16 of 76

$$Frf, ook, tx = \frac{9}{8}Flo - Fdev$$

$$Frf, ook, tx = \frac{9}{8}\frac{Fxtal}{R+1}[75(P+1)+S)] - Fdev$$

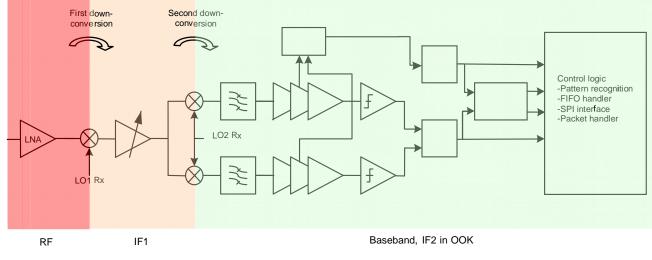

Consequently, in receive mode, due to the low intermediate frequency (Low-IF) architecture of the RF64 the frequency should be configured so as to ensure the correct low-IF receiver baseband center frequency, IF2.

$$Frf, ook, rx = \frac{9}{8}Flo - IF2$$

Frf, ook, rx =  $\frac{9}{8}\frac{Fxtal}{R+1}[75(P+1)+S)] - IF2$

Note that from Section 3.4.4, it is recommended that IF2 be set to 100 kHz.

Page 17 of 76

# 3.3. Transmitter Description

The RF64 is set to transmit mode when MCParam\_Chip\_mode = 100.

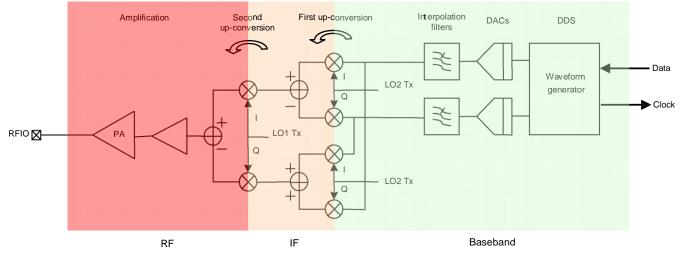

Figure 8: Transmitter Architecture

## 3.3.1. Architecture Description

The baseband I and Q signals are digitally generated by a DDS whose digital to analog converters (DAC) followed by two anti-aliasing low-pass filters transform the digital signal into analog in-phase (I) and quadrature (Q) components whose frequency is the selected frequency deviation (Fdev).

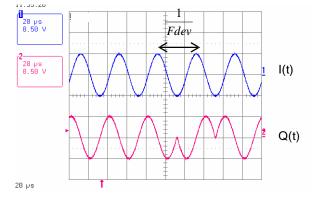

Figure 9: I(t), Q(t) Overview

In FSK mode, the relative phase of I and Q is switched by the input data between -90° and +90° with continuous phase. The modulation is therefore performed at this initial stage, since the information contained in the phase difference will be converted into a frequency shift when the I and Q signals are up-converted in the first mixer stage. This first up-conversion stage is duplicated to enhance image rejection. The FSK convention is such that:

$$DATA = "1" \otimes Frf + Fdev$$

$DATA = "0" \otimes Frf - Fdev$

Page 18 of 76

In OOK mode, the phase difference between the I and Q channels is kept constant (independent of the transmitted data). Thus, the first stage of up-conversion creates a fixed frequency signal at the low IF = Fdev (This explains why the transmitted OOK spectrum is offset by Fdev).

OOK Modulation is accomplished by switching on and off the PA and PA regulator stages. By convention:

$$DATA = "1" \Rightarrow PAon$$

$DATA = "0" \Rightarrow PAoff$

After the interpolation filters, a set of four mixers combines the I and Q signals and converts them into a pair of complex signals at the second intermediate frequency, equal to 1/8 of the LO frequency, or 1/9 of the RF frequency. These two new I and Q signals are then combined and up-converted to the final RF frequency by two quadrature mixers fed by the LO signal. The signal is pre-amplified, and then the transmitter output is driven by a final power amplifier stage.

## 3.3.2. Bit Rate Setting

In Continuous transmit mode, setting the Bit Rate is useful to determine the frequency of DCLK. As explained in section 5.3.2, DCLK will trigger an interrupt on the uC each time a new bit has to be transmitted.

$$BR = \frac{F_{XTAL}}{2*[1+val(MCParam\_BR\_C)]*[1+val(MCParam\_BR\_D)]}$$

### 3.3.3. Alternative Settings

Bit rate, frequency deviation and TX interpolation filter settings are a function of the reference oscillator crystal frequency, F<sub>XTAL</sub>. Settings other than those programmable with a 12.8 MHz crystal can be obtained by selection of the correct reference oscillator frequency.

### 3.3.4. Fdev Setting in FSK Mode

The frequency deviation, Fdev, of the FSK transmitter is programmed through bits MCParam\_Freq\_dev:

$$Fdev = \frac{F_{XTAL}}{32^* [1 + val(MCParam_Freq\_dev)]}$$

For correct operation the modulation index ß should be such that:

$$\beta = 2 * \frac{Fdev}{BR} \ge 2$$

It should be noted that for communications between a pair of RF64s, that Fdev should be at least 33 kHz to ensure a correct operation on the receiver side.

### 3.3.5. Fdev Setting in OOK Mode

Fdev has no physical meaning in OOK transmit mode. However, as has been shown - due to the DDS baseband signal generation, the OOK signal is always offset by "-Fdev" (see formulas is section 3.2.8). It is suggested that Fdev retains its default value of 100 kHz in OOK mode.

Page 19 of 76

### 3.3.6. Interpolation Filter

After digital to analog conversion, both I and Q signals are smoothed by interpolation filters. This block low-pass filters the digitally generated signal, and prevents the alias signals from entering the modulators. Its bandwidth can be programmed with the register RXParam\_InterpFiltTx, and should be set to:

$$BW \cong 3^* \left[ Fdev + \frac{BR}{2} \right]$$

Where Fdev is the programmed frequency deviation as set in MCParam\_Freq\_dev, and BR is the physical Bit Rate of transmission.

Notes:

- Low interpolation filter bandwidth will attenuate the baseband I/Q signals thus reducing the power of the FSK signal. Conversely, excessive bandwidth will degrade spectral purity.

- For the wideband FSK modulation, for example when operating in DTS mode, the recommended filter setting can not be reached. However, the impact upon spectral purity will be negligible, due to the already wideband channel.

## 3.3.7. Power Amplifier

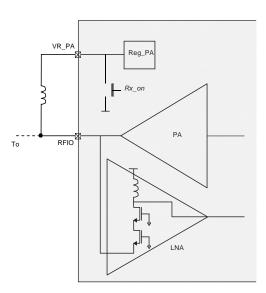

The Power Amplifier (PA) integrated in the RF64 operates under a regulated voltage supply of 1.8 V. The external PA choke inductor is biased by an internal regulator output made available on pin 29 (VR\_PA). Thanks to these features, the PA output power is consistent over the power supply range. This is important for mobile applications where this allows both predictable RF performance and battery life.

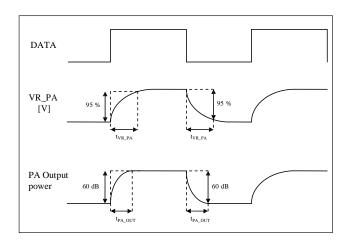

#### 3.3.7.1. Rise and Fall Times Control

In OOK mode, the PA ramp times can be accurately controlled through the MCParam\_PA\_ramp register. Those bits directly control the slew rate of VR\_PA output (pin 29).

Table 11: PA Rise/Fall Times

| MCParam_PA_ramp | t <sub>VR_PA</sub> | t <sub>PA_OUT</sub> (rise / fall) |

|-----------------|--------------------|-----------------------------------|

| 00              | 3 us               | 2.5 / 2 us                        |

| 01              | 8.5 us             | 5 / 3 us                          |

| 10              | 15 us              | 10 / 6 us                         |

| 11              | 23 us              | 20 / 10 us                        |

Figure 10: PA Control

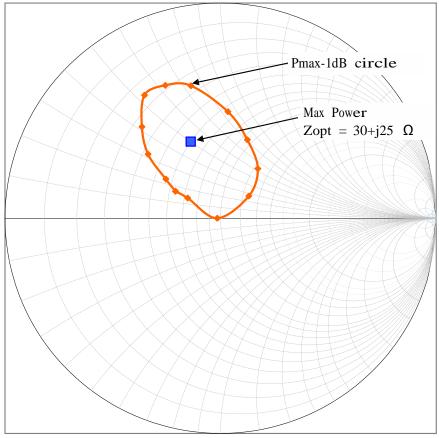

#### 3.3.7.2. Optimum Load Impedance (value to confirm)

As the PA and the LNA front-ends in the RF64 share the same Input/Output pin, they are internally matched to approximately 50  $\Omega$ .

Figure 11: Optimal Load Impedance Chart

Please refer to the reference design section for an optimized PA load setting.

#### 3.3.7.3. Suggested PA Biasing and Matching

The recommended PA bias and matching circuit is illustrated below:

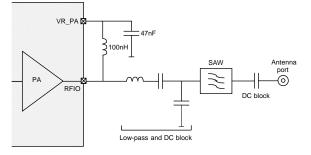

Figure 12: Recommended PA Biasing and Output Matching

Please refer to section 7.5.3 of this document for the optimized matching arrangement for each frequency band.

### 3.3.8. Common Input and Output Front-End