# **Applications Note: SY5867**

Dimming Interface Converter Compatible With 0/1~10V Dimming Resistor Dimming And PWM Dimming

## **General Description**

SY5867 is a dimming interface converter whose input signal can be a 0/1~10V dimming signal, resistor, or PWM signal. It recognizes the signal automatically. The final output of SY5867 is a PWM signal which is used to control a dimmable CC regulator or drive an optocoupler to achieve isolated dimming. The frequency of output PWM signal and the source current to drive passive 0~10V dimmer/Resistor can be set by external capacitor and resistor.

## **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY5867FAC       | SO8          |      |

### **Features**

- Compatible with 0/1~10V Dimming, Resistor Dimming and PWM Dimming.

- Recognize Different Dimming Dignal Automatically.

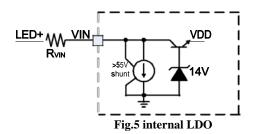

- Integrate 60V LDO Module to Simplify External Circuit

- The Source Current for Passive 0/1~10V Dimmer Can Be Set.

- The Frequency of Output Can Be Set.

- Compact Package: SO8

## **Applications**

• LED Lighting

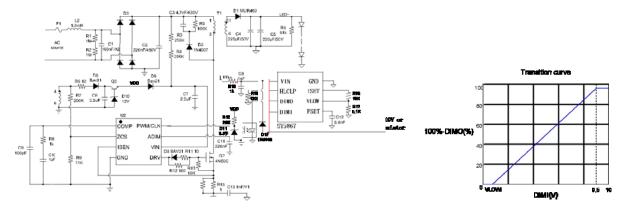

## **Typical Applications**

Fig.1 High clamp mode application Schematic

Fig.2 Low clamp mode application Schematic

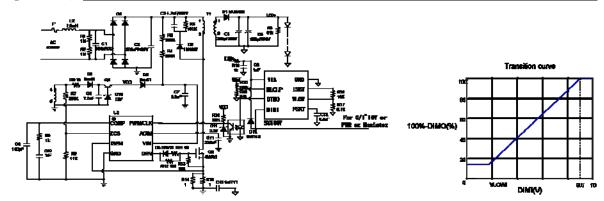

# $Pinout \ ({\sf top \ view})$

Top Mark: BKRxyz, (Device code: BKR; x=year code, y=week code, z= lot number code)

| Pin Name | Pin number | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | 1          | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ISET 2   |            | Source current setting pin.  V <sub>ISET</sub> is a 1.5V voltage source.  This pin is used to set the source current of DIMI pin for passive dimmer or resistor. $I_{DIMI} = \frac{5 \times 1.5}{R}$ The zero coordinate setting pin                                                                                                                                                                                                                                                                                                                                                                                                             |

| VLOW     | 3          | The zero coordinate setting pin. This pin is used to set the lowest input voltage which corresponds to 0% duty. The real minimum $0\sim10\text{V}$ input is $V_{LOWI} = 1.55 \cdot K1 \cdot V_{LOW} - K1 \cdot 0.926 + 0.2$ $K1 = 1 \text{ ; (Low clamp mode)}$ $K1 = \frac{14.58}{52.85 + 14.58} \frac{52.85 + (14.58 //R_{HLCLPD})}{14.58 //R_{HLCLPD}} \text{ ; (H igh clamp m ode)}$                                                                                                                                                                                                                                                         |

| FSET     | 4          | Dimming frequency setting pin.  This pin is used o set the frequency of DIMO pin. $F_{DIM} = \frac{30 \cdot 10^{-6}}{(6 \cdot 6 - V_{LOW}) \cdot C_{FSET}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DIMI     | 5          | Dimm ng input pin. Dimming signal is connected to this pin. It maybe is a 0/1~10V analog sig al, resistor or a PWM signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DIMO     | 6          | Dimming output pin.  This pin will output a PWM signal to driver opto-coupler for separation dimming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HLCLP    | 7          | High clamp and low clamp mode setting pin.  If the voltage of HLCLP pin is larger than 100mV during IC start-up, it enters into low clamp mode, else it works in high clamp mode.  In low clamp mode, if V <sub>DIMI</sub> is less than the setting value, it is clamped internally. $V = \frac{9.3}{2} \cdot (V_{HLCLP} - 0.2) + 0.2$ In High clamp mode, the clamp voltage is 9.5V fixedly, and the resistor connected to HLCLP is used to adjust the max duty. $D = \frac{67.79 \cdot R_{HLCLPD}}{67.43 \cdot R_{HLCLPD} + 770.59}$ For Example $R_{HCLP} = 510 \text{k ohm}$ $D = \frac{67.79 \cdot 510}{67.43 \cdot 510 + 770.59} = 98.3\%$ |

| VIN      | 8          | Power supply pin. This pin provides power supply for IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

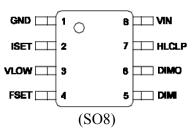

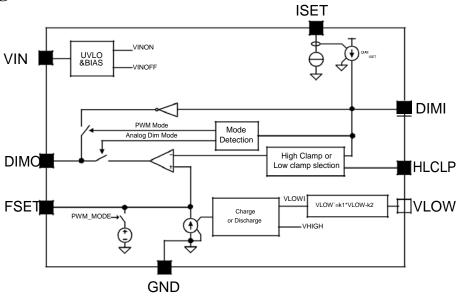

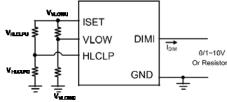

# **Block Diagram**

Fig.3 Block Diagram

# Absolute Maximum Ratings (Note 1)

| VIN                                   |                |

|---------------------------------------|----------------|

| IIN                                   | 10mA           |

| ISET, FSET, VLOW                      | -0.3V~3.6V     |

| DIMI,DIMO                             | 0.3V~20V       |

| Power Dissipation, @ TA = 25°C SO8    | 0.8W           |

| Package Thermal Resistance (Note 2)   |                |

| $SO8,\theta J_{A}$                    | 88°C/W         |

| SO8, θ <sub>JC</sub>                  | 45°C/W         |

| Maximum Junction Temperature          | 125°C          |

| Lead Temperature (Soldering, 10 sec.) | 260°C          |

| Storage Temperature Range             | -65°C to 150°C |

|                                       |                |

## **Recommended Ope ating Conditions**

| VIN                        | - V <sub>VIN.ON</sub> ~55V |

|----------------------------|----------------------------|

| Junction Temperature Range | 0°C to 125°C               |

### **Electrical Characteristics**

$(V_{IN} = 15V, T_A = 25^{\circ}C \text{ unless otherwise specified})$

| Parameter                        | Symbol               | Test Conditions | Min     | Тур        | Max   | Unit |  |

|----------------------------------|----------------------|-----------------|---------|------------|-------|------|--|

| Power Supply Section             |                      |                 |         |            |       |      |  |

| VIN Voltage Range                | $V_{ m VIN}$         |                 | Vvin_on |            | 55    | V    |  |

| VIN Turn-on Threshold            | Vvin_on              |                 | 8.4     | 9.2        | 10.2  | V    |  |

| VIN Turn-off Threshold           | Vvin_off             |                 |         | VIN_ON-1.7 |       | V    |  |

| VIN Over Voltage Protection      | VVIN_OVP             |                 | 52      | 55         | 59    | V    |  |

| DIMI Section                     |                      |                 |         |            |       |      |  |

| Range of Minimum Dimming voltage | VLOW_Range           |                 | 0       |            | Viset | V    |  |

| Ref Voltage of ISET              | VISET                |                 | 1.45    | 1.5        | 1.55  | V    |  |

| MAX DIMI Source Current          | Isr_max              | ISET=3.75K      | 1.85    | 2.0        | 2.15  | mA   |  |

| Maximum Dimming Voltage          | VHIGH                |                 | 9.2     | 9.5        | 9.8   | V    |  |

| Max Duty of PWM                  | DPWM_MAX             |                 |         | 99(note 3) |       | %    |  |

| PWM ON Voltage Threshold         | VPWM_ON              |                 | 2.3     |            |       | V    |  |

| PWM OFF Voltage Threshold        | V <sub>PWM_OFF</sub> |                 |         |            | 0.8   | V    |  |

| PWM Frequency Range              | fрwм                 |                 | 400     |            | 10k   | Hz   |  |

| Thermal Section                  | Thermal Section      |                 |         |            |       |      |  |

| Thermal Shut Down Temperature    | Tsd                  |                 |         | 145        |       | °C   |  |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not mpl ed. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $f_{JA}$  is measured in the natural c nvection at  $T_A = 25^{\circ}\text{C}$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Test condition: Device mounted on 2" x 2" FR-4 substrate PCB, 20z copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

Note 3: Increase VIN pin voltage gradually higher than  $V_{VIN\ ON}$  voltage then turn down to 12V.

### **Operation**

SY5867 is a dimming interface converter whose input signal can be a 0/1~10V dimming signal, resistor, or PWM signal. It recognizes the signal automatically.

When input signal is  $0/1\sim10V$  dimming signal, It will be converted into a PWM signal to driver opto-coupler or dimmable IC.

When input signal is a resistor, there is a current flowing out from DIMI pin to produce a voltage at the resistor. Then It works as same as 0/1~10V dimming input.

When input signal is a PWM signal, it is converted into a reverse PWM signal.

There are two working modes.

Low-clamp is used to clamp the minimum duty cycle. High-clamp is used to clamp the maximum duty cycle. More detail information is discussed below.

## **Applications Information**

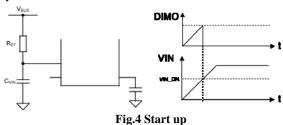

#### Start up

Supposing DIMI is floating.

DIMO follow VIN before VIN reach  $V_{IN\ ON}$ . After reaching  $V_{IN\ ON}$ , IC begin to work and DIMO is regulated by DIMI.

IC integrates a 60V LDO for simplifying peripheral device. There is a shunt current if VIN voltage is larger than 55V which helps to protect IC when power voltage is high than 55V.

#### 2. Dimming Input

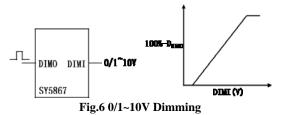

#### (1) 0/1~10V Dimming

If input signal of DIMI pin is  $0/1\sim10\text{V}$ , it is converted into reversed duty signal.

#### (2) Resistor Dimming

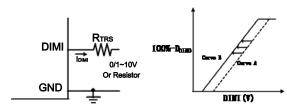

Fig.7 Resistor Dimming

If DIMI is connected with a variable resistor, there is a current flow from DIMI pin to drive the resistor and produce 0~10V signal. Also, the current exists in 0/1~10V dimming application.

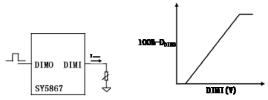

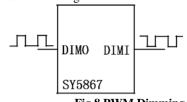

### (3) PWM Dimming

Fig.8 PWM Dimming

If input dimming signal is PWM signal, IC converts it into a reversed PWM signal.

#### 3. Working Mode

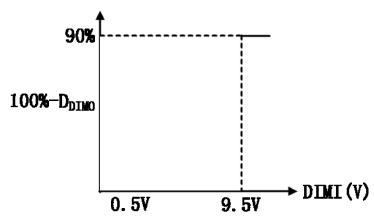

#### (1) High clamp mode

Fig.9 High clamp mode setting

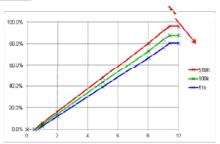

Fig.10 High clamp mode design result

As showed above, High clamp mode is used to set the maximum duty which can regulate the full load current in some special application.

If the voltage of HLCLP pin is less than  $V_{HLCLP\_MODE}$  when VIN firstly reach  $V_{VIN\_ON}$ , the high clamp mode is selected. To ensure IC enters into high clamp mode,  $R_{HLCLPU}$  should not be connected.

The turning point of DIMI is always 9.5V, and the maximum duty can be calculated by the following formula.

$$D_{\text{\tiny MAX}} = \frac{1}{2.2 - 0.2} \cdot \frac{(9.5 - 0.2) \cdot \frac{14.58 \cdot R_{HLCLPD}}{14.58 \cdot R_{HLCLPD}}}{\frac{14.58 \cdot R_{HLCLPD}}{14.58 \cdot R_{HLCLPD}}} + 52.85})$$

Or

$$D_{MAX} = \frac{67.79 \cdot R_{HLCLPD}}{67.43 \cdot R_{HLCLPD} + 770.59}$$

With different R<sub>HLCLPD</sub>, the maximum duty is changed. The design result is showed above.

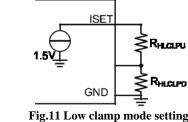

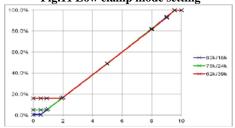

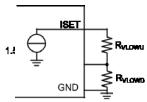

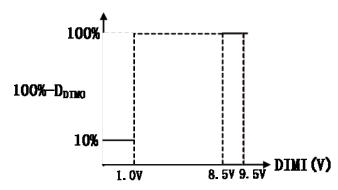

#### (2) Low Clamp Mode

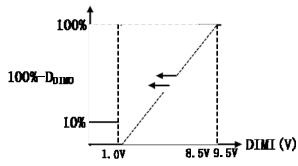

Fig.12 Low clamp mode design result

Low clamp mode is used to clamp the minimum duty as showed above.

If the voltage of HLCLP pin is larger than  $V_{HLCLP\_MODE}$  when VIN reach  $V_{VIN\_ON}$ , the low clamp mode is selected. To ensure IC enters into low clamp mode, please ensure:

ensure:

$$\frac{V \cdot \kappa}{R}_{\frac{ISET}{HLCLPD}} + R$$

$> V$   $\frac{ILCLPD}{HLCLPD}_{HLCLPD} + U.11$

The turning point of DIMI pin is set by

$$V_{LCLP} = \frac{9.3}{2} \cdot (V_{LCLP} - 0.2) + 0.2$$

$$= \frac{9.3}{2} \cdot (\frac{ISET}{K} + K_{LCLPD} - 0.2) + 0.2$$

With different Rugging and Rugging the minimum of the property of the minimum of the property of the minimum of the property of the prop

With different Rhlclpu and Rhlclpd, the minimum duty is set. The design result is showed above.

#### (3) Special low clamp mode

If there is no need to work in high clamp mode or low clamp mode, It can s t by that:

$$V_{LCLP} = 0.2$$

It means that:

$V \cdot K$

ISET HLCLPD

$$R + R = 0.2$$

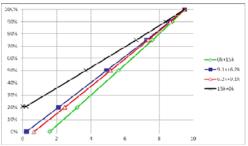

#### 4. Zero coordinate setting

Fig.13 zero coordinate setting

Fig.13 zero coordinate design result

Adjust the zero cross point of the curve by setting the voltage of VLOW. The formula is showed below.

$$V_{LOWI} = 1.55 \cdot K1 \cdot V_{LOW} - K1 \cdot 0.926 + 0.2$$

K1 is a compensation for high clamp mode. *K*1=1; (Low clamp mode)

$$K1 = \frac{14.58}{52.85 + 14.58} \cdot \frac{52.85 + (14.58 / / R_{HLCLPD})}{14.58 / R_{HLCLPD}}$$

; (High clamp mode)

If VLOWI is less than 0.2V, the duty is clamped when DIMI<0.2V.

And the

$$V_{LOW}$$

is set by:

$$V = \frac{V_{ISET} \cdot R_{VLOWD}}{R} + R_{VLOWD}$$

The design result is showed above.

#### **5.** Curve translation

Fig.14 curve translation setting

To translate the converted curve, R<sub>TRS</sub> is set. With greater Rtrs, converted curve is changed from A to B as showed above.

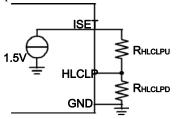

### 6. DIMI current set

Fig.15 DIMI current setting

If the dimmer is passive device or a resistor, there should be a drive current to power the dimmer.

The current is set by:

$$I_{DIMI} = \frac{5 \times 1.5}{R_{ISET}}$$

$$R = \left(R + R_{ISCLPU} + R_{ILCLPD}\right) / \left/ \left(R + R_{VLOWU} + R_{VLOWD}\right)$$

### 7. Frequ ncy setting

There is a 20uA current charge or discharge FSET capacitor to produce a reference triangle wave.

The frequency is set by:

$$F_{DIM} = \frac{20U}{2 \cdot (2.2 - \frac{1}{3} \cdot V) \cdot C}$$

$$FSET$$

## **Design Example**

A design example of typical application is shown below step by step.

### Example A

#1. Identify design specification

Fig.16 Target Curve

| Target parameter  |       |      |      |

|-------------------|-------|------|------|

| Idimi             | 500uA | Fs   | 1kHz |

| V <sub>LOWI</sub> | 0.5   | Dмах | 90%  |

(a). Mode Selection

As described above, high clamp mode is selected.

(b). DMAX calculation

$$D_{MAX} = \frac{67.79 \cdot R_{HCLPD}}{67.43 \cdot R_{HCLPD} + 770.59} = 90\%$$

$$HCLPU = NC$$

$$R_{HCLPD} = 97.6 K OHM \approx 100 K OHM$$

(c). VLOWI calculation

$$= \frac{14.58}{52.85 + 14.58} \cdot \frac{.52.85 + (14.58 / / R_{HLCLPD})}{14.58 / / R_{HLCLPD}}$$

$$= 1.114$$

$$V_{LOWI} = 1.55 \cdot K1 \cdot V_{LOW} - K1 \cdot 0.926 + 0.2 = 0.5$$

$$V = V \cdot K_{VLOWD} - K1 \cdot 0.926 + 0.2 = 0.5$$

$$V = R_{VLOWU} + R_{VLOWD} = 0.771$$

So,

$$R = 1.06 \cdot R$$

VLOWD VLOW

(d). I<sub>DIMI</sub> calculation

$$I_{DIMI} = \frac{5 \times 1.5}{R_{ISET}} = 500UA$$

$$R_{ISET} = (R_{HLCLPU} + R_{HLCLPD}) / / (R_{VLOWU} + R_{VLOWD}) = 15 KOHM$$

So,

$$R_{VLOWU} = 7.28 \text{ KOHM} \approx 7.2 \text{ KOHM}$$

$$R_{VLOWD} = 7.72 \text{ KOHM} \approx 7.8 \text{ KOHM}$$

(e). Fs calculation

$$F = \frac{20U}{2 \cdot (2.2 - \frac{1}{3} \cdot V) \cdot C} = 1 \text{KHZ}$$

So,

$$C$$

$$FSET = 5.1NF$$

### (f). The design Result

| Conditions |          |         |          |

|------------|----------|---------|----------|

| Rhlclpu    | NC       | RHLCLPD | 100k ohm |

| Rvlowu     | 7.2k ohm | Rvlowd  | 7.8k ohm |

| Cfset      | 5.1nF    |         |          |

### Example B

### #1. Identify design specification

Fig.17 Target Curve

| Target pa ameter  |       |      |      |

|-------------------|-------|------|------|

| Ідімі             | 500uA | Fs   | 1kHz |

| VLCLP             | 1.0   | Dmin | 10%  |

| V <sub>HCLP</sub> | 8.5   | Dmax | 90%  |

### (a). Mode Selection

As described above, Low clamp mode is selected.

#### (a). translation calculation

$$R_{TRS} = \frac{V}{I_{DIMI}} - \frac{9.5 - 8.5}{0.5} KOHM = 2 KOHM$$

Fig.18 Curve translation

(b). VLOWI calculation

Zero Cross point:

$$V_{LOWI} = \frac{8.5 - 1.0}{100\% - 10\%} (0 - 10\%) + 1.0 + I_{DIMI} \cdot R = 1.167 V$$

Due to,

$$V_{LOWI} = 1.55 \cdot V_{LOW} - 0.926 + 0.2 = 1.167$$

$$V_{LOW} = \frac{V_{LOWD}}{R_{VLOWD}} + R_{VLOWD} = 1.22$$

So,

$$R_{VLOWD} = 4.38 \cdot R_{VLOWD}$$

(c).Low clamp mode design

$$V_{LCLP} = \frac{9.3}{2} \cdot (V_{HLCLP} - 0.2) + 0.2$$

$$= \frac{9.3}{(R + R)} + \frac{1}{(R + R)} - 0.2 + 0.2 = V + I \cdot R$$

$$= \frac{1}{2} \cdot (R + R) + \frac{1}{2} \cdot R + \frac{1}{2} \cdot$$

So,

$$R_{_{HLCPD}} = 0.64 \cdot R_{_{HLLPU}}$$

If  $R_{HLCLPU} + R_{HLCLPD} = 100 \text{ KOHM}$

$$R_{HLCLPU} = 61.0 KOHM \approx 62 KOHM$$

$$R_{HLCLPD} = 39KOHM$$

(d).

$$I_{DIMI}$$

calculation  $5 \times 1.5$

$$I_{DIMI} = \frac{1}{R} = \frac{1}{R} = \frac{1500 \text{ UA}}{R_{ISET}} = \frac{1500 \text{ UA}}{R_{ISET}} = \frac{15 \text{ KOHM}}{R_{ISET}} = \frac{15$$

$$R_{VLOWU} = 3.3 KOHM$$

$$R_{VLOWD} = 14.4 KOHM \approx 15 KOHM$$

(e). Fs calculation

$$F = \frac{20U}{2 \cdot (2.2 - \frac{1}{3} \cdot V) \cdot C} = 1 \text{KHZ}$$

$$FSET = 5.1NF$$

(f). The design Result

| Conditions |          |         |         |

|------------|----------|---------|---------|

| RHLCLPU    | 62k ohm  | RHLCLPD | 39k ohm |

| Rvlowu     | 3.3k ohm | Rvlowd  | 15k ohm |

| Rtrs       | 2.0k ohm | Cfset   | 5.1nF   |

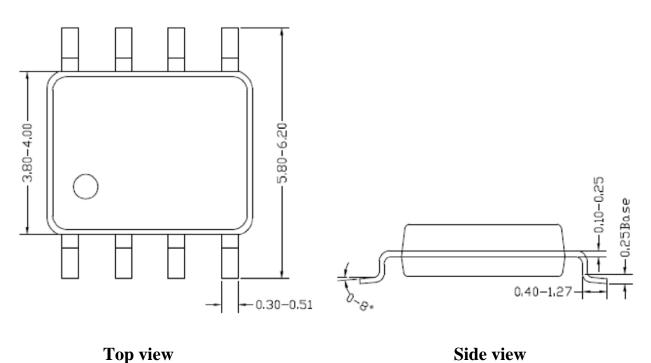

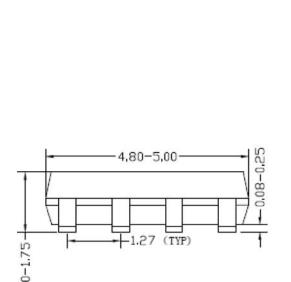

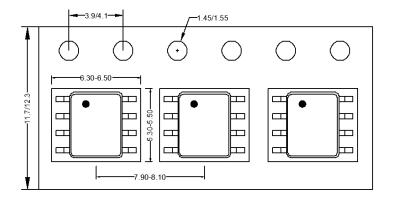

# SO8 Package outline & PCB layout design

Front view

**Recommended Pad Layout** (Reference only)

Notes: All dimension in millimeter and exclude mold flash & metal burr.

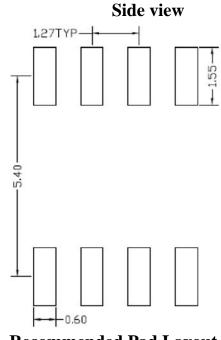

# **Taping & Reel Specification**

## 1. Taping orientation for packages (SO8)

Feeding direction ----

## 2. Carrier Tape & Reel specification for packages

| Package<br>type | Tape width (mm) | Pocket<br>pitch(mm) | Reel size<br>(Inch) | Trailer<br>length(mm) | Leader length (mm) | Qty per<br>reel |

|-----------------|-----------------|---------------------|---------------------|-----------------------|--------------------|-----------------|

| SO8             | 12              | 8                   | 13"                 | 400                   | 400                | 2500            |