## Ultra-Low Power Stereo CODEC with Audio Enhancement DSP, 1W Stereo Class D Speaker Drivers and Ground Referenced Headphone Drivers

### DESCRIPTION

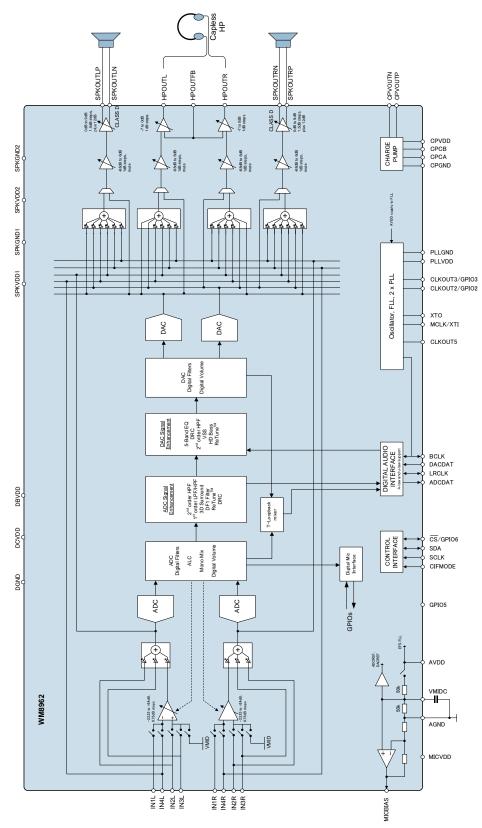

The WM8962 is a low power, high performance stereo CODEC designed for portable digital audio applications.

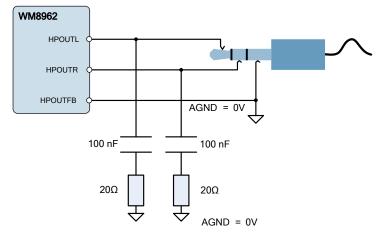

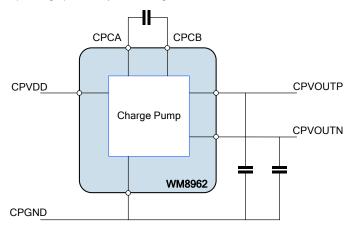

An integrated charge pump provides a ground referenced output which removes the need for DC-blocking capacitors on the headphone outputs, and uses the Wolfson 'Class-W' amplifier techniques - incorporating an innovative dual-mode charge pump architecture - to optimise efficiency and power consumption during playback. A DC Servo is used to reduce DC ground offsets. This improves power consumption and minimises pops and clicks.

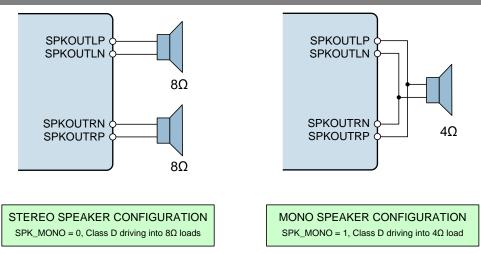

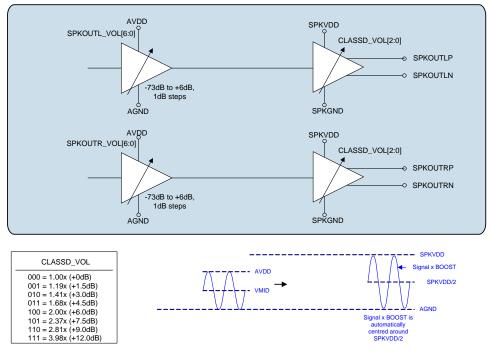

Stereo class D speaker drivers provide 1W per channel into  $8\Omega$  loads, or 2W mono into a  $4\Omega$  load, with a 5V supply. Low leakage, excellent PSRR and pop/click suppression mechanisms also allow direct battery connection to the speaker supply. Flexible speaker boost settings allow speaker output power to be maximised while minimising other analogue supply currents.

Control sequences for audio path setup can be pre-loaded and executed by an integrated sequencer to reduce software driver development and eliminate pops and clicks via SilentSwitch<sup>™</sup> technology.

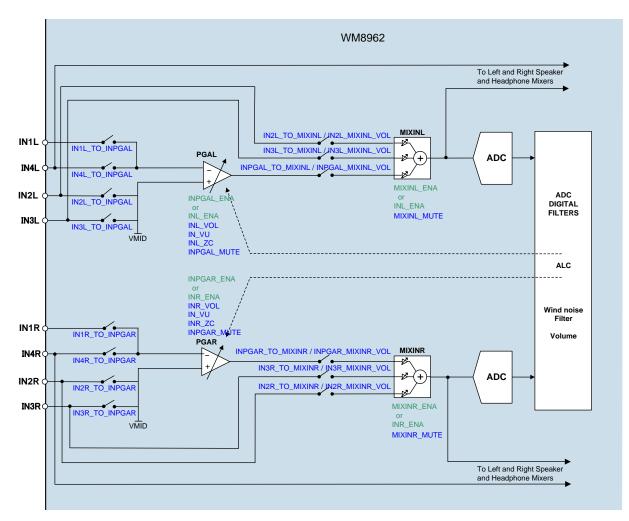

Flexible input configuration: four stereo inputs or eight mono inputs on Left or Right ADC, with a complete analogue (four single-ended stereo inputs) and digital microphone interface. External component requirements are drastically reduced as no separate microphone, speaker or headphone amplifiers are required. Advanced on-chip digital signal processing performs automatic level control for the microphone or line input.

Stereo 24-bit sigma-delta ADCs and DACs are used with low power over-sampling digital interpolation and decimation filters and a flexible digital audio interface.

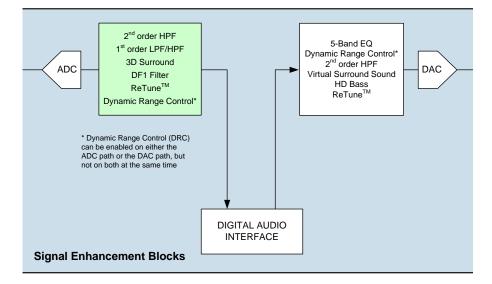

A programmable audio enhancement DSP is included with multiple preset algorithms. Virtual Surround Sound widens the stereo speaker audio image, HD Bass enhances low frequencies, and ReTune<sup>™</sup> flattens the frequency response of the speaker or microphone path. A configurable DSP includes additional functions such as 3D widening for recording, a 5-band parametric EQ and Dynamic Range Controller.

Two high performance PLLs and one Frequency Locked Loop (FLL) are integrated to enable the user to clock a full audio system.

The WM8962 operates at analogue supply voltages down to 1.7V, although the digital supplies can operate at voltages down to 1.62V to save power. The speaker supply can operate at up to 5.5V. Unused functions can be disabled using software control to save power.

The WM8962 is supplied in a very small W-CSP package, ideal for use in hand-held and portable systems.

### **FEATURES**

- DAC SNR 98dB ('A' weighted), THD -84dB at 48kHz, 1.8V

- ADC SNR 94dB ('A' weighted), THD -85dB at 48kHz, 1.8V

- Stereo Class D Speaker Driver

- 1W per channel into  $8\Omega$  BTL speakers

- 2W mono into  $4\Omega$  BTL speakers

- Flexible internal switching clock

- Wolfson 'Class-W' ultra-low power headphone driver

- Up to 31mW per channel output power at 1% THD+N

- Ground Referenced

- Low offset (+/- 1.2mV)

- Pop and click suppression

- Control sequencer for pop-minimised power-up/down

- Single register write for default start-up sequence

- Microphone Interface

- Single ended four stereo analogue input

- Integrated low noise MICBIAS

- Digital microphone interface

- Programmable ALC / Limiter and Noise Gate

- Programmable Audio Enhancement DSP with Presets

- Virtual Surround Sound

- HD Bass

- ReTune<sup>™</sup>

- Fixed Audio Processing DSP

- 3D stereo widening

- 5-band Parametric EQ

- Dynamic range controller

- Beep generator

- Two integrated PLLs enable clocking of full audio system

- Low Power Consumption

- 7.7mW headphone playback

- 8.3mW analogue record mode

- Low Supply Voltages

- Analogue 1.7V to 2.0V (Speaker supply up to 5.5V)

- Charge pump 1.7V to 2.0V

- MIC bias amp supply 1.7V to 3.6V

- Digital 1.62V to 2.0V

- 2-wire I2C and 3- or 4-wire SPI serial control interface

- Standard sample rates from 8kHz to 96kHz

- W-CSP, 3.6x3.9mm 49-pin

### APPLICATIONS

- Portable gaming, Voice recorders

- Mobile multimedia

- Stereo DSC-Camcorder

.

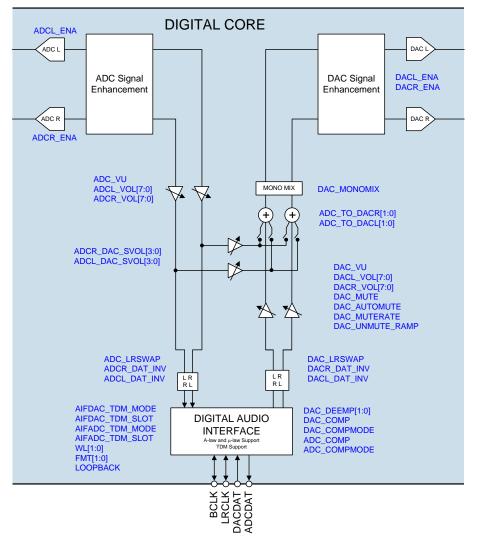

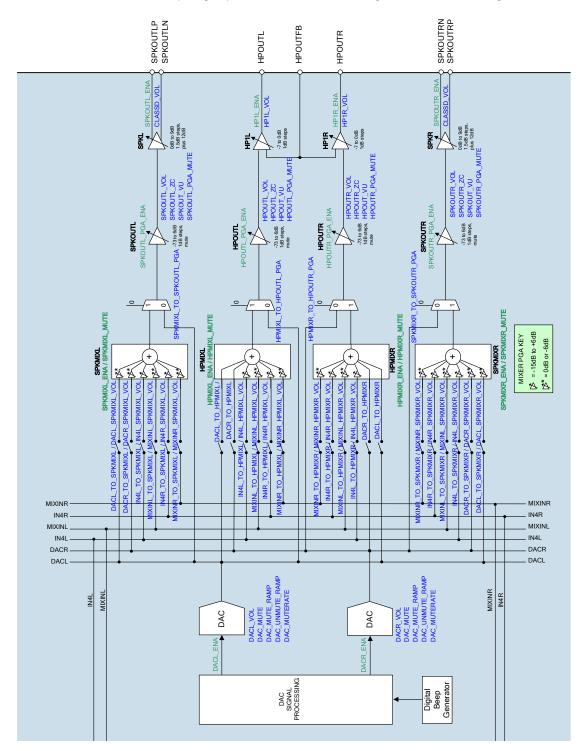

### **BLOCK DIAGRAM**

### TABLE OF CONTENTS

| DESCRIPTION                                                                   | 1  |

|-------------------------------------------------------------------------------|----|

| FEATURES                                                                      |    |

| APPLICATIONS                                                                  | 1  |

| BLOCK DIAGRAM                                                                 |    |

| TABLE OF CONTENTS.                                                            |    |

| PIN CONFIGURATION                                                             | -  |

| ORDERING INFORMATION                                                          |    |

| PIN DESCRIPTION                                                               |    |

| ABSOLUTE MAXIMUM RATINGS                                                      |    |

| RECOMMENDED OPERATING CONDITIONS                                              |    |

| ELECTRICAL CHARACTERISTICS                                                    |    |

| TERMINOLOGY                                                                   |    |

| TYPICAL PERFORMANCE                                                           |    |

| TYPICAL PERFORMANCE                                                           |    |

|                                                                               |    |

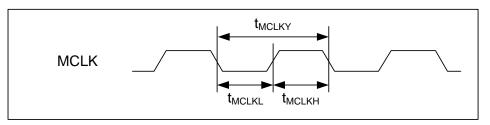

| SIGNAL TIMING REQUIREMENTS                                                    |    |

|                                                                               |    |

|                                                                               |    |

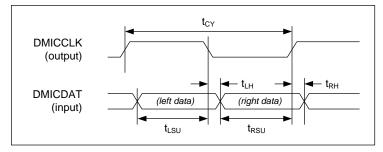

| DIGITAL MICROPHONE (DMIC) INTERFACE TIMING                                    |    |

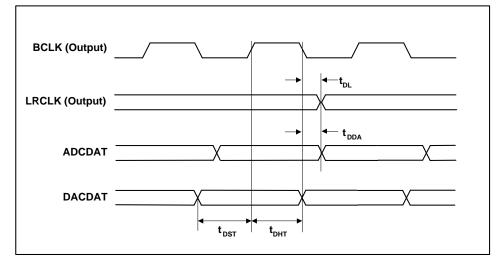

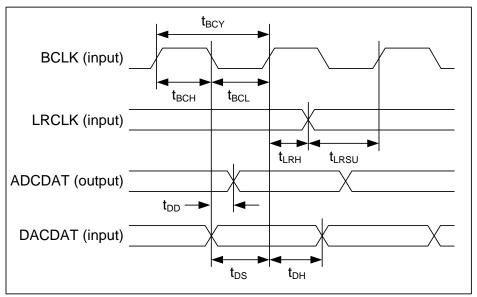

| DIGITAL AUDIO INTERFACE - MASTER MODE<br>DIGITAL AUDIO INTERFACE - SLAVE MODE |    |

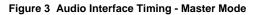

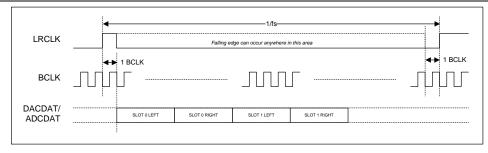

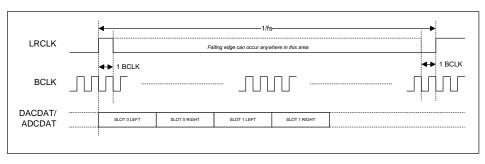

| DIGITAL AUDIO INTERFACE - SLAVE MODE<br>DIGITAL AUDIO INTERFACE - TDM MODE    |    |

| CONTROL INTERFACE TIMING                                                      |    |

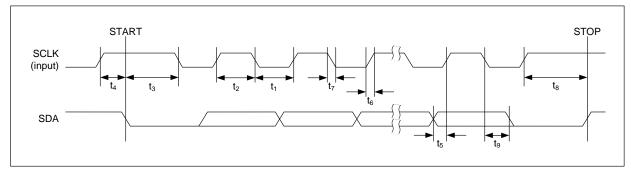

| 2-WIRE (I2C) CONTROL MODE                                                     |    |

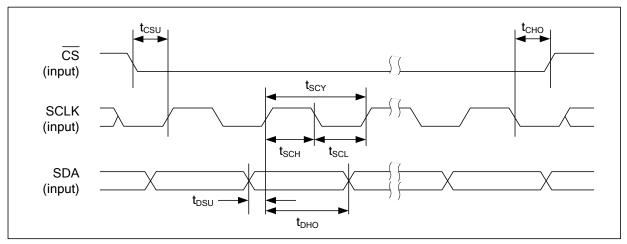

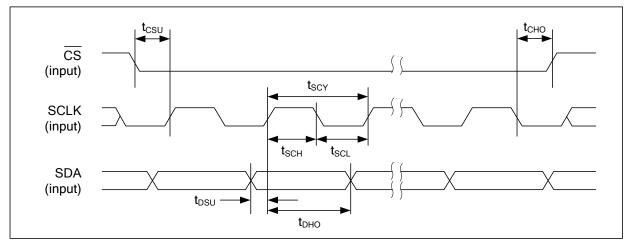

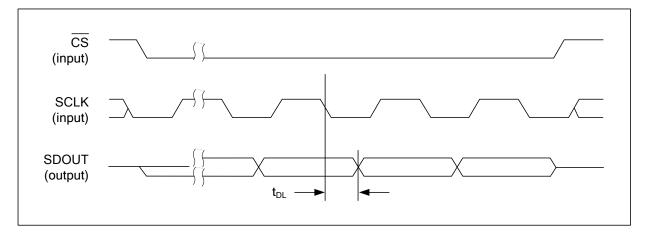

| 3-WIRE (SPI) CONTROL MODE                                                     |    |

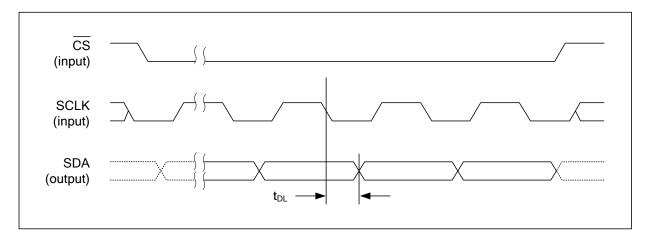

| 4-WIRE (SPI) CONTROL MODE                                                     |    |

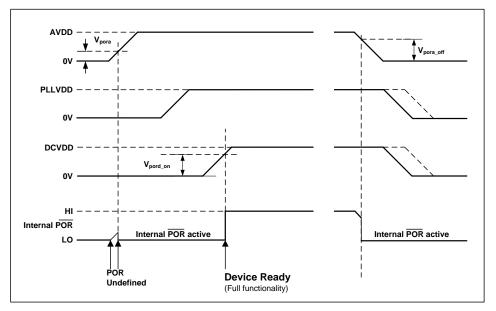

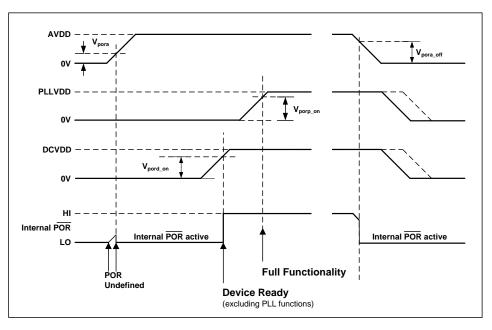

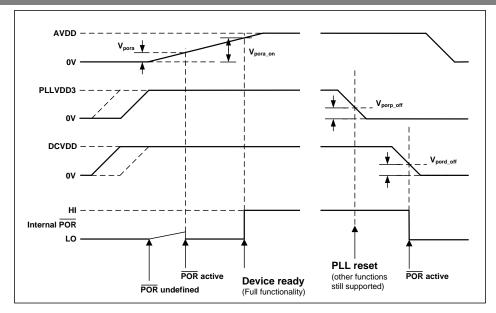

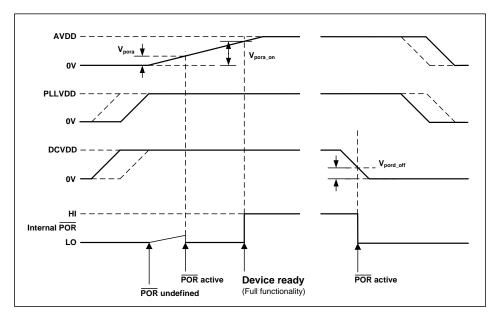

| POWER ON RESET TIMING                                                         |    |

| DEVICE DESCRIPTION                                                            | 36 |

| INTRODUCTION                                                                  |    |

| INPUT SIGNAL PATH                                                             | 37 |

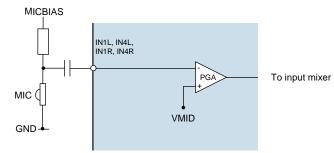

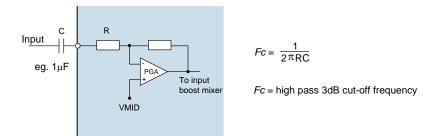

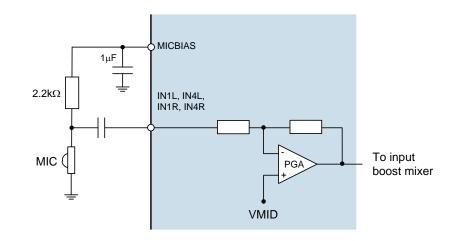

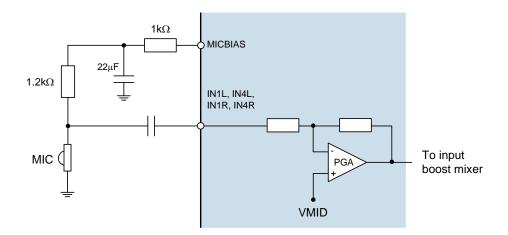

| MICROPHONE INPUT CONNECTION                                                   | 38 |

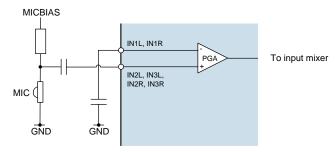

| LINE INPUT CONNECTION                                                         | 38 |

| MICROPHONE BIAS CONTROL                                                       |    |

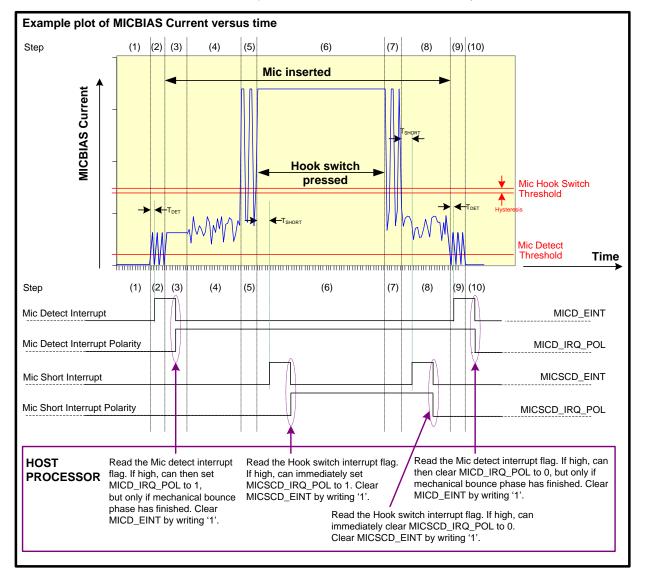

| MICBIAS CURRENT DETECT                                                        |    |

| MICBIAS CURRENT DETECT FILTERING                                              |    |

| MICROPHONE HOOK SWITCH DETECTION                                              |    |

|                                                                               |    |

| INPUT PGA CONFIGURATION<br>INPUT PGA VOLUME CONTROL                           |    |

| INPUT PGA VOLOME CONTROL                                                      |    |

| INPUT MIXER ENABLE                                                            |    |

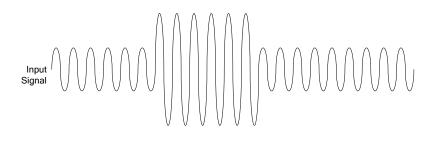

| AUTOMATIC LEVEL CONTROL (ALC)                                                 |    |

| LIMITER MODE                                                                  |    |

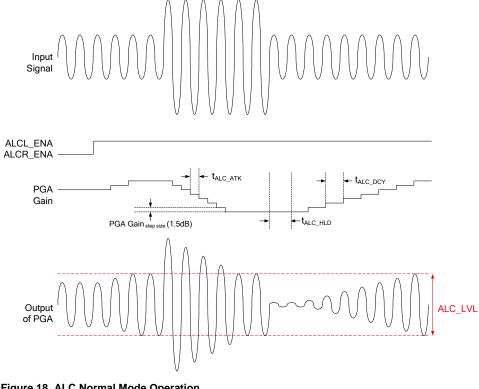

| ALC GAIN CONTROL                                                              |    |

| ALC DYNAMIC CHARACTERISTICS                                                   |    |

| PEAK LIMITER                                                                  | 56 |

| ALC NOISE GATE                                                                |    |

| ALC STATUS READBACK                                                           |    |

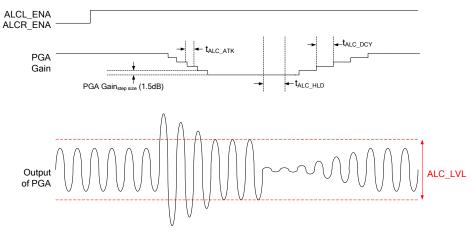

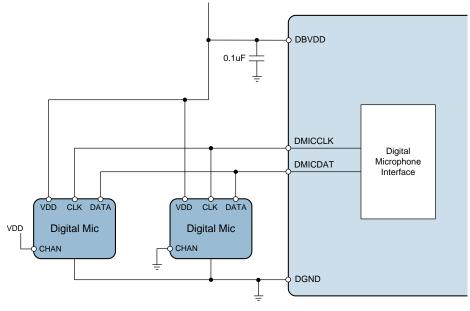

| DIGITAL MICROPHONE INTERFACE                                                  |    |

| ANALOGUE TO DIGITAL CONVERTER (ADC)                                           |    |

| ADC CLOCKING CONTROL                                                          |    |

| ADC DIGITAL VOLUME CONTROL                                                    | 66 |

| ADC OVERSAMPLING RATIO (OSR)                                 | 68  |

|--------------------------------------------------------------|-----|

| ADC MONOMIX                                                  | 68  |

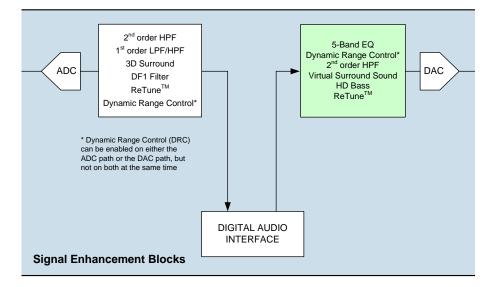

| DSP SIGNAL ENHANCEMENTS                                      | 69  |

| ENABLE SEQUENCE - ENHANCEMENTS INITIALLY DISABLED            | 69  |

| ENABLE / DISABLE SEQUENCE - ENHANCEMENTS INITIALLY ENABLED   | 70  |

| DISABLE ALL SOUND ENHANCEMENTS SEQUENCE                      | 71  |

| UPDATE / READBACK SEQUENCE - ENHANCEMENTS INITIALLY ENABLED  |     |

| UPDATE / READBACK SEQUENCE - ENHANCEMENTS INITIALLY DISABLED |     |

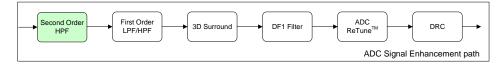

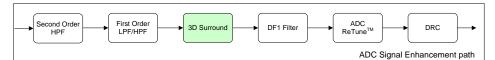

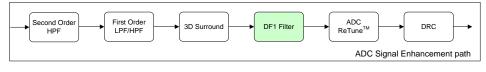

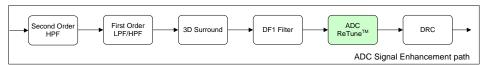

| ADC SIGNAL PATH ENHANCEMENTS                                 |     |

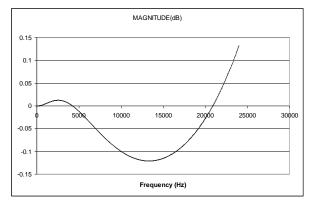

| ADC SECOND ORDER HIGH-PASS FILTER                            |     |

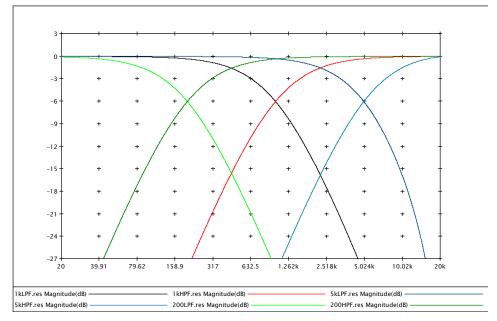

| LOW-PASS / HIGH-PASS FILTER (LPF/HPF)                        |     |

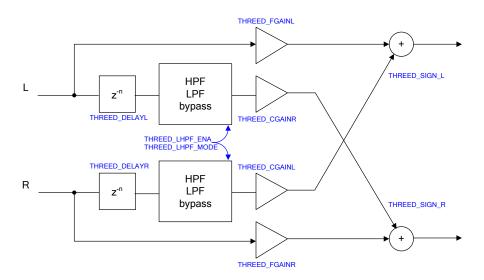

| 3D SURROUND                                                  |     |

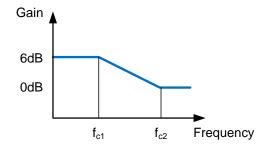

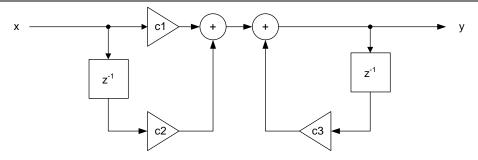

| DF1 FILTER                                                   |     |

| ADC RETUNE                                                   |     |

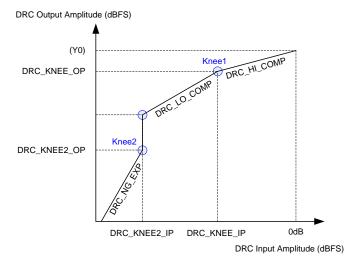

| DYNAMIC RANGE CONTROL (DRC)                                  |     |

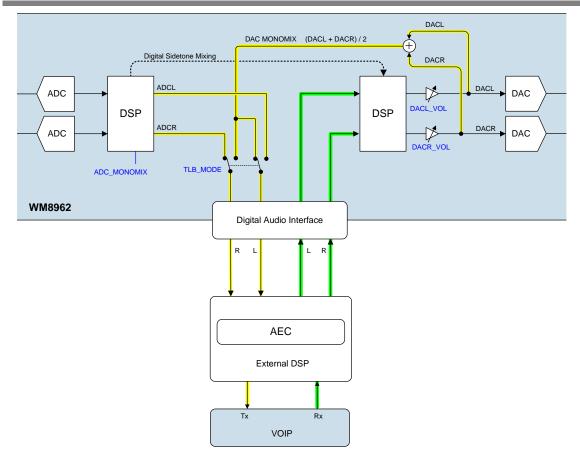

| DIGITAL MIXING                                               |     |

| DIGITAL MIXING PATHS                                         |     |

| DIGITAL MIXING FATTIS                                        |     |

| T-LOOPBACK                                                   |     |

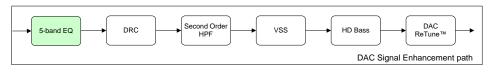

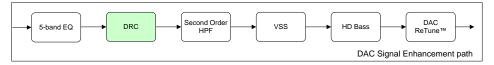

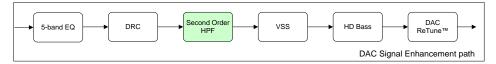

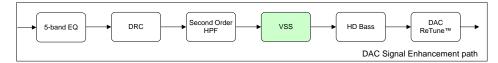

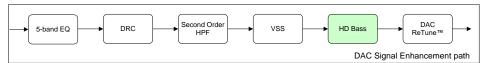

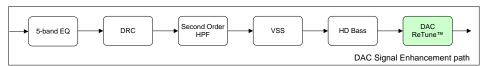

| DAC SIGNAL PATH ENHANCEMENTS                                 |     |

| 5-BAND EQ                                                    |     |

|                                                              |     |

|                                                              |     |

| DAC SECOND ORDER HIGH-PASS FILTER                            |     |

| VIRTUAL SURROUND SOUND (VSS)                                 |     |

| HD BASS                                                      |     |

|                                                              |     |

| DIGITAL-TO-ANALOGUE CONVERTER (DAC)                          |     |

| DAC CLOCKING CONTROL                                         |     |

| DAC DIGITAL VOLUME CONTROL                                   |     |

| DAC SOFT MUTE AND UN-MUTE                                    |     |

| DAC AUTO-MUTE                                                |     |

| DAC MONO MIX                                                 |     |

| DAC DE-EMPHASIS                                              |     |

| DAC OVERSAMPLING RATIO (OSR)                                 |     |

| DIGITAL BEEP GENERATOR                                       |     |

| OUTPUT SIGNAL PATH                                           |     |

| OUTPUT SIGNAL PATHS ENABLE                                   |     |

| SPEAKER OUTPUT PATHS                                         |     |

| SPEAKER MIXER CONTROL                                        |     |

| SPEAKER OUTPUT PGA CONTROL                                   |     |

| SPEAKER OUTPUT CONFIGURATIONS                                |     |

| HEADPHONE OUTPUT PATHS                                       | 123 |

| HEADPHONE SIGNAL PATHS ENABLE                                |     |

| HEADPHONE MIXER CONTROL                                      |     |

| HEADPHONE OUTPUT PGA CONTROL                                 | 128 |

| HEADPHONE OUTPUT CONFIGURATIONS                              |     |

| CHARGE PUMP                                                  |     |

| DC SERVO                                                     |     |

| DC SERVO ENABLE AND START-UP                                 |     |

| DC SERVO ACTIVE MODES                                        |     |

| REFERENCE VOLTAGES AND BIAS CONTROL                          |     |

| ANALOGUE REFERENCE AND MASTER BIAS                           |     |

| INPUT SIGNAL PATH BIAS CONTROL SETTINGS                      |     |

| OUTPUT SIGNAL PATH BIAS CONTROL SETTINGS                     |     |

|                                                              |     |

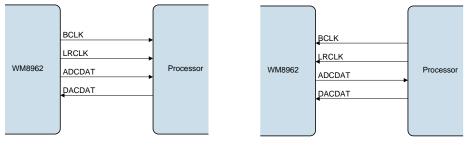

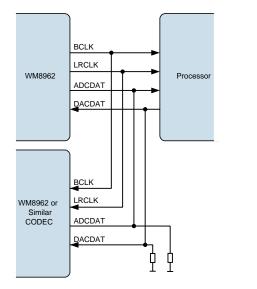

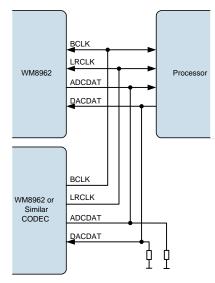

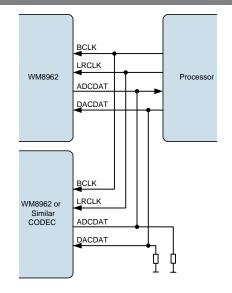

| DIGITAL AUDIO INTERFACE                                   | 137 |

|-----------------------------------------------------------|-----|

| MASTER AND SLAVE MODE OPERATION                           |     |

| OPERATION WITH TDM                                        | 138 |

| BCLK FREQUENCY                                            |     |

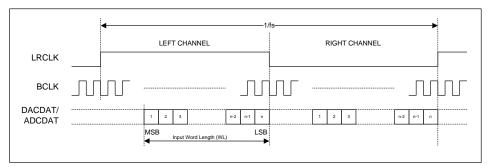

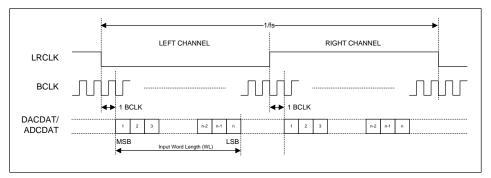

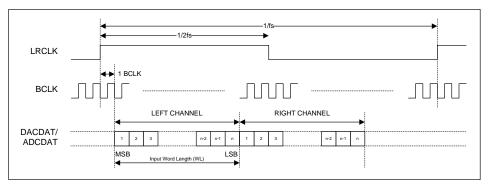

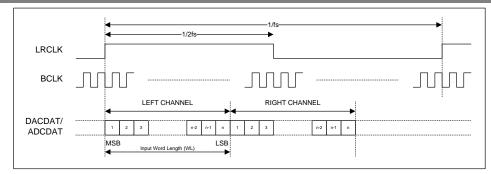

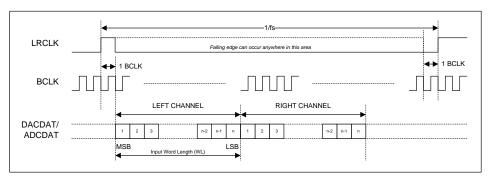

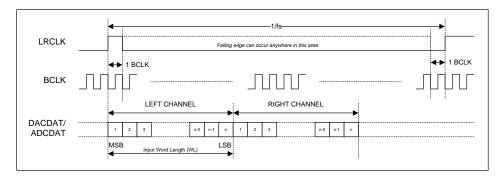

| AUDIO DATA FORMATS (NORMAL MODE)                          | 139 |

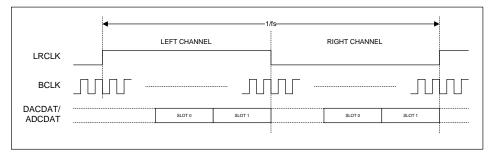

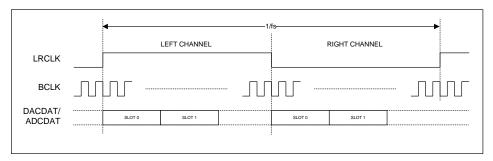

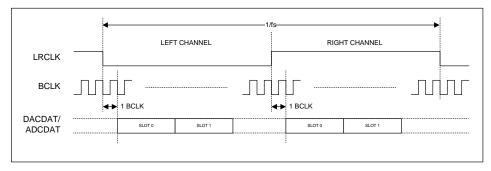

| AUDIO DATA FORMATS (TDM MODE)                             | 141 |

| DIGITAL AUDIO INTERFACE CONTROL                           |     |

| AUDIO INTERFACE TRI-STATE                                 | 144 |

| BCLK AND LRCLK CONTROL                                    | 144 |

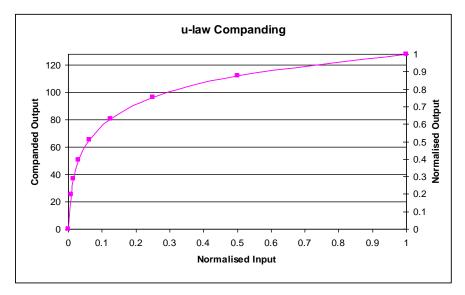

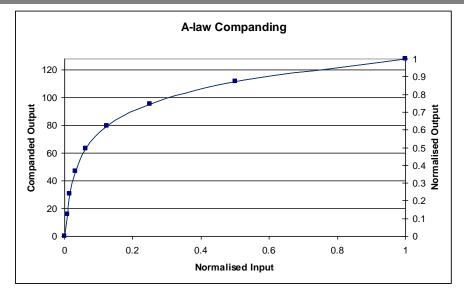

| COMPANDING                                                | 145 |

| LOOPBACK                                                  | 147 |

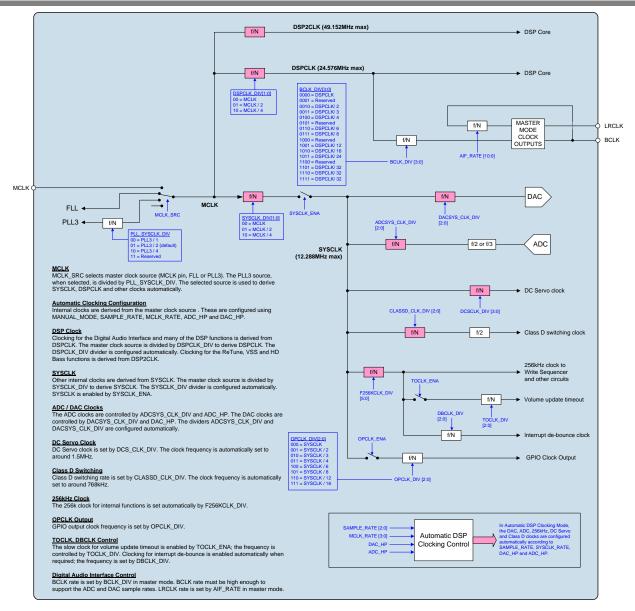

| CLOCKING AND SAMPLE RATES                                 | 148 |

| SYSCLK CONTROL                                            |     |

| AUTOMATIC CLOCKING CONFIGURATION                          | 151 |

| DSP, ADC, DAC CLOCK CONTROL                               | 153 |

| CLASS D, 256K, DC SERVO CLOCK CONTROL                     |     |

| OPCLK CONTROL                                             |     |

| TOCLK, DBCLK CONTROL                                      |     |

| BCLK AND LRCLK CONTROL                                    |     |

| CONTROL INTERFACE CLOCKING                                |     |

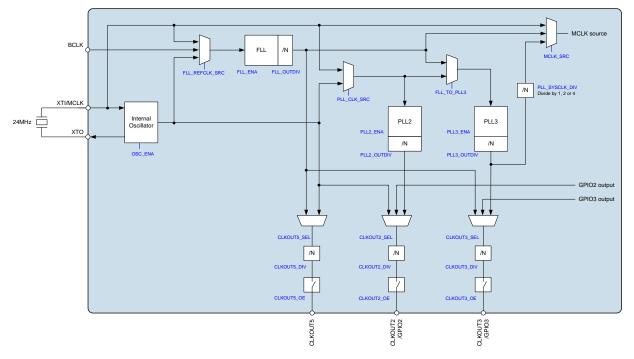

| INTERNAL / EXTERNAL CLOCK GENERATION                      |     |

| START-UP OPTIONS FOR INTERNAL / EXTERNAL CLOCK GENERATION |     |

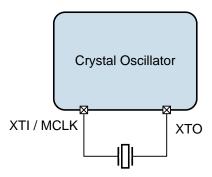

| INTERNAL OSCILLATOR CONTROL                               |     |

| CLKOUT CONTROL                                            |     |

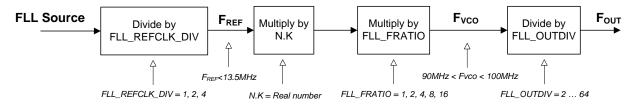

| FREQUENCY LOCKED LOOP (FLL)                               |     |

| FREE-RUNNING FLL CLOCK                                    |     |

| EXAMPLE FLL CALCULATION                                   |     |

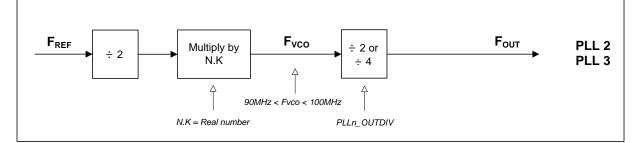

| PHASE LOCKED LOOP (PLL)                                   |     |

|                                                           |     |

| GENERAL PURPOSE INPUT/OUTPUT (GPIO)                       |     |

|                                                           |     |

| CONTROL INTERFACE                                         |     |

| SELECTION OF CONTROL INTERFACE MODE                       |     |

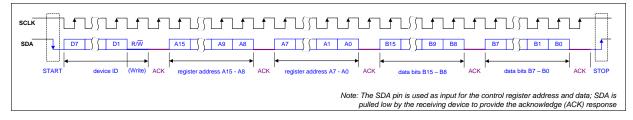

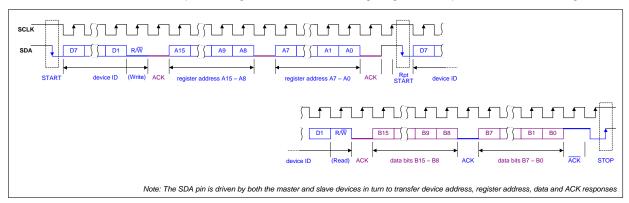

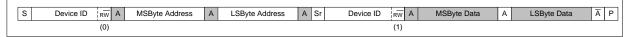

| 2-WIRE (I2C) CONTROL MODE                                 |     |

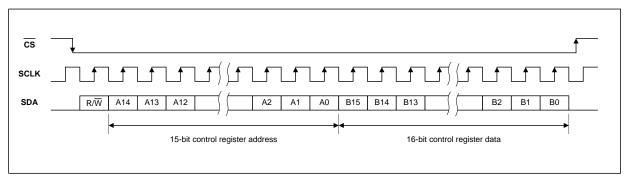

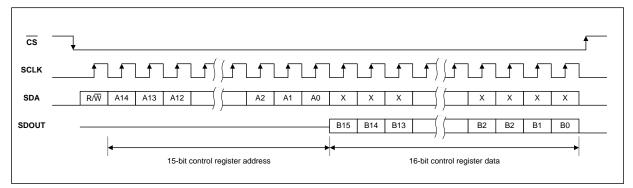

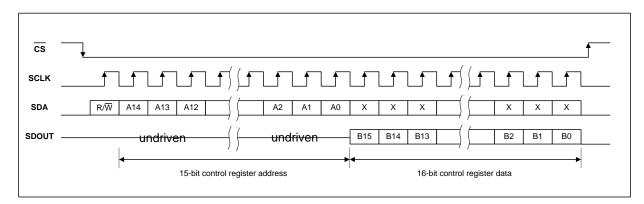

| 3-WIRE (SPI) CONTROL MODE                                 |     |

|                                                           |     |

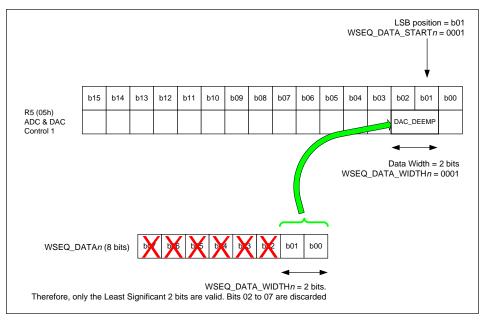

| CONTROL WRITE SEQUENCER                                   |     |

|                                                           |     |

| PROGRAMMING A SEQUENCE                                    |     |

|                                                           |     |

|                                                           |     |

| SOFTWARE RESET AND CHIP ID                                |     |

| REGISTER MAP                                              |     |

| REGISTER BITS BY ADDRESS                                  |     |

| DIGITAL FILTER CHARACTERISTICS                            |     |

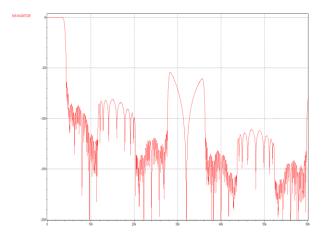

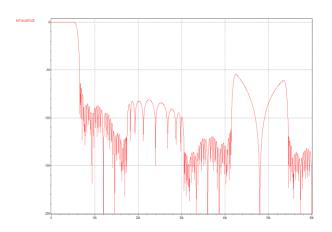

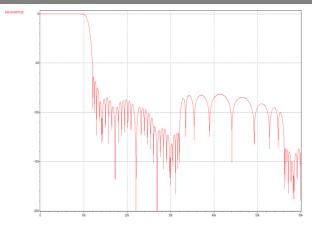

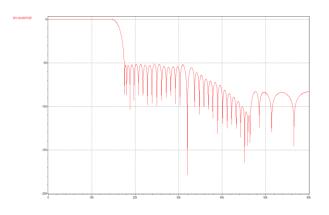

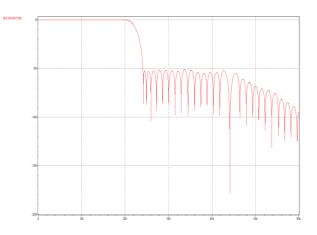

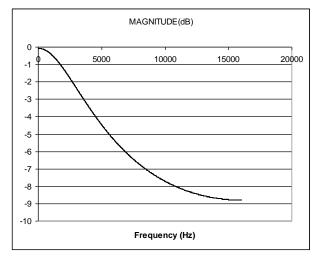

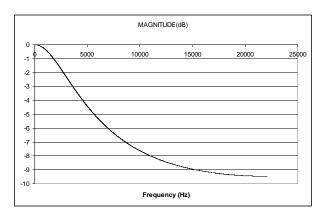

| DAC FILTER RESPONSES                                      |     |

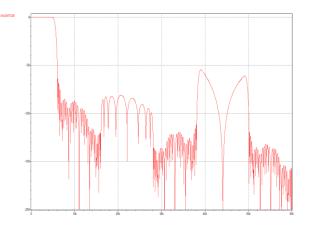

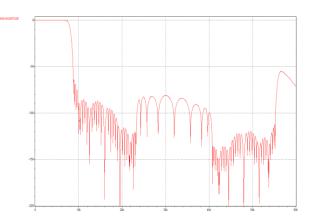

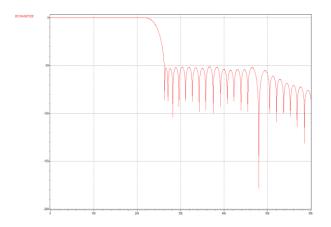

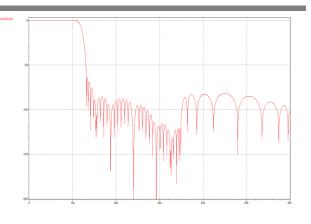

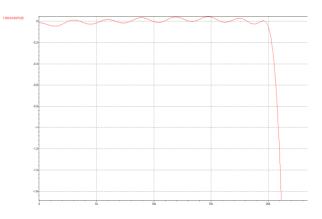

| ADC FILTER RESPONSES                                      | -   |

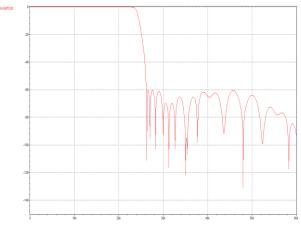

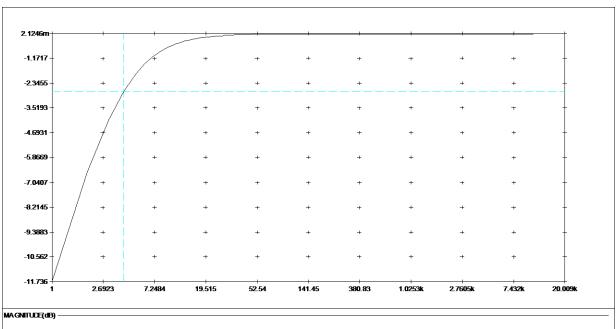

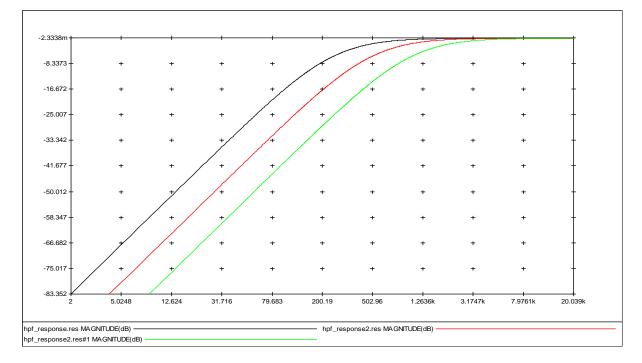

| ADC HIGH PASS FILTER RESPONSES                            |     |

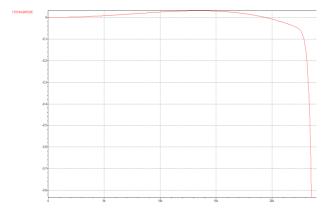

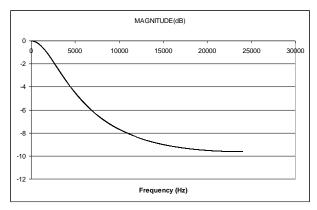

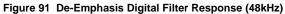

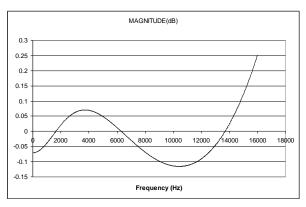

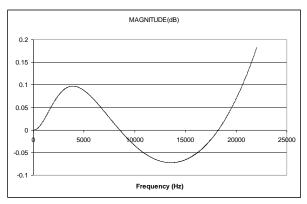

| DE-EMPHASIS FILTER RESPONSES                              |     |

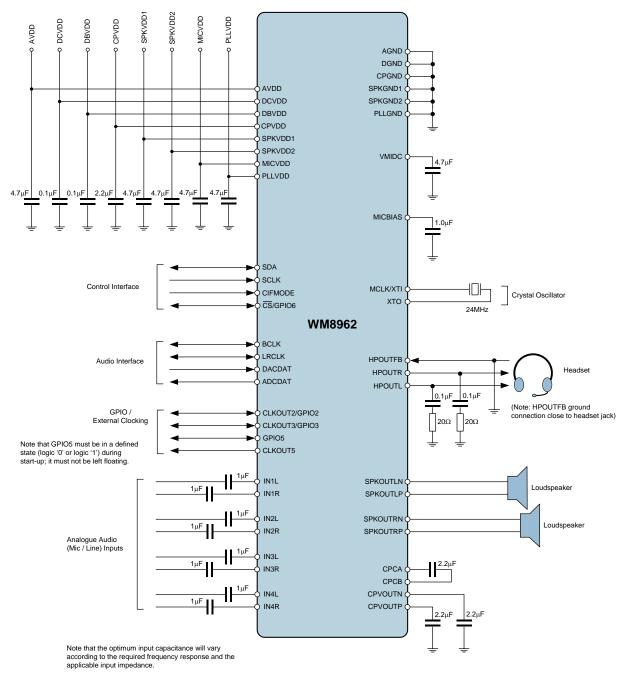

| APPLICATIONS INFORMATION                                  | -   |

| ANALOGUE INPUT PATHS                                      |     |

| MICROPHONE BIAS CIRCUIT                                   |     |

| CHARGE PUMP COMPONENTS                                    |     |

| RECOMMENDED EXTERNAL COMPONENTS DIAGRAM                   |     |

| REVISION HISTORY                             | 290 |

|----------------------------------------------|-----|

|                                              |     |

| IMPORTANT NOTICE                             | 289 |

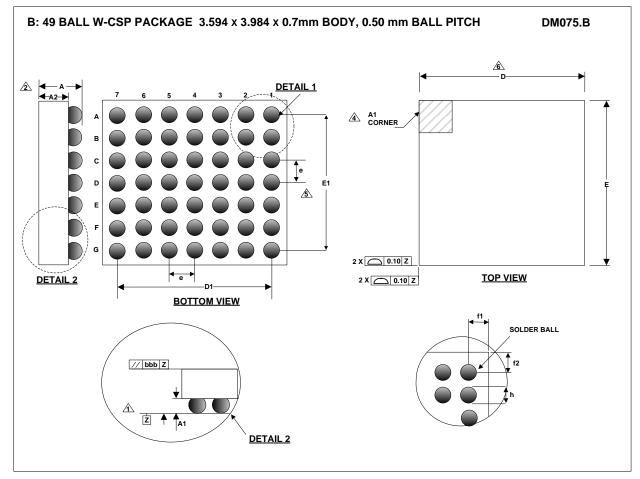

| PACKAGE DIAGRAM FOR DEVICES MARKED BCA HN8   |     |

|                                              | -   |

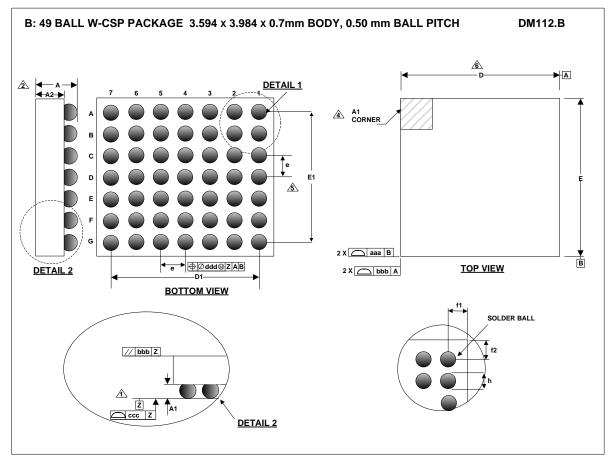

| PACKAGE DIAGRAM FOR DEVICES MARKED KBC       | 287 |

| PACKAGE DIMENSIONS                           | 287 |

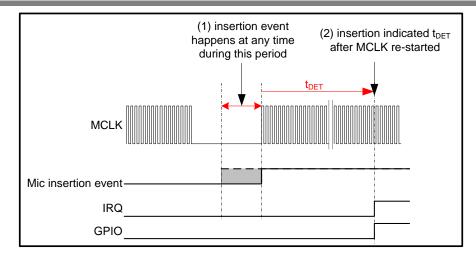

| MIC DETECTION SEQUENCE USING MICBIAS CURRENT |     |

|                                              |     |

| PCB LAYOUT CONSIDERATIONS                    | 201 |

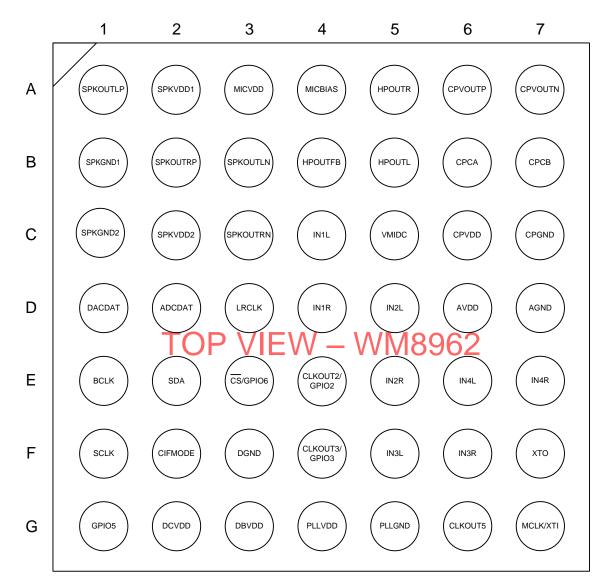

### **PIN CONFIGURATION**

### **ORDERING INFORMATION**

| ORDER CODE   | TEMPERATURE RANGE | PACKAGE                                                                      | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|--------------|-------------------|------------------------------------------------------------------------------|-------------------------------|-------------------------------|

| WM8962ECS/R  | -40°C to +85°C    | 49-ball CSP,<br>3.6 x 3.9 mm,<br>Pb-free, tape and reel,<br>Backside-coated. | MSL1                          | 260°C                         |

| WM8962ECSN/R | -40°C to +85°C    | 49-ball CSP,<br>3.6 x 3.9 mm,<br>Pb-free, tape and reel.                     | MSL1                          | 260°C                         |

Note: Reel quantity = 5,000

### **PIN DESCRIPTION**

| PIN NO | NAME          | TYPE                   | DESCRIPTION                                                          |

|--------|---------------|------------------------|----------------------------------------------------------------------|

| A1     | SPKOUTLP      | Analogue Output        | Left speaker positive output                                         |

| A2     | SPKVDD1       | Supply                 | Supply for left speaker drivers                                      |

| A3     | MICVDD        | Supply                 | Microphone bias amp supply                                           |

| A4     | MICBIAS       | Reference              | Microphone bias                                                      |

| A5     | HPOUTR        | Analogue Output        | Right output (Line or headphone)                                     |

| A6     | CPVOUTP       | Supply                 | Charge pump positive supply (powers HPOUTL, HPOUTR)                  |

| A7     | CPVOUTN       | Supply                 | Charge pump negative supply (powers HPOUTL, HPOUTR)                  |

| B1     | SPKGND1       | Supply                 | Ground for left speaker drivers                                      |

| B2     | SPKOUTRP      | Analogue Output        | Right speaker positive output                                        |

| B3     | SPKOUTLN      | Analogue Output        | Left speaker negative output                                         |

| B4     | HPOUTFB       | Analogue Input         | HPOUTL/R ground loop noise rejection feedback                        |

| B5     | HPOUTL        | Analogue Output        | Left output (Line or headphone)                                      |

| B6     | CPCA          | Analogue Input         | Charge pump fly-back capacitor pin                                   |

| B7     | СРСВ          | Analogue Input         | Charge pump fly-back capacitor pin                                   |

| C1     | SPKGND2       | Supply                 | Ground for right speaker drivers                                     |

| C2     | SPKVDD2       | Supply                 | Supply for right speaker drivers                                     |

| C3     | SPKOUTRN      | Analogue Output        | Right speaker negative output                                        |

| C4     | IN1L          | Analogue Input         | Left channel single-ended input 1                                    |

| C5     | VMIDC         | Reference              | Mid-rail voltage (AVDD/2) - (requires decoupling capacitor)          |

| C6     | CPVDD         | Supply                 | Charge pump power supply                                             |

| C7     | CPGND         | Supply                 | Charge pump ground (return path for CPVDD)                           |

| D1     | DACDAT        | Digital Input          | DAC digital audio data                                               |

| D2     | ADCDAT        | Digital Output         | ADC digital audio data                                               |

| D3     | LRCLK         | Digital Input / Output | Audio interface left / right clock                                   |

| D4     | IN1R          | Analogue Input         | Right channel single-ended input 1                                   |

| D5     | IN2L          | Analogue Input         | Left channel single-ended input 2                                    |

| D6     | AVDD          | Supply                 | Analogue supply                                                      |

| D7     | AGND          | Supply                 | Analogue ground (return path for AVDD and MICVDD)                    |

| E1     | BCLK          | Digital Input / Output | Audio interface bit clock                                            |

| E2     | SDA           | Digital Input / Output | Control interface data input / 2-wire acknowledge output             |

| E3     | CS/GPIO6      | Digital Input / Output | CS input / Digital Microphone input / General purpose input / output |

| E4     | CLKOUT2/GPIO2 | Digital Output         | PLL2 Clock output / General purpose input / output                   |

| E5     | IN2R          | Analogue Input         | Right channel single-ended input 2                                   |

| E6     | IN4L          | Analogue Input         | Left channel single-ended input 4                                    |

| E7     | IN4R          | Analogue Input         | Right channel single-ended input 4                                   |

| F1     | SCLK          | Digital Input          | Control interface clock input                                        |

| F2     | CIFMODE       | Digital Input          | Selects 2-wire or 3 / 4-wire control wire interface                  |

| F3     | DGND          | Supply                 | Digital ground                                                       |

| F4     | CLKOUT3/GPIO3 | Digital Output         | PLL3 / FLL Clock output / GPIO                                       |

| F5     | IN3L          | Analogue Input         | Left channel single-ended input 3                                    |

| F6     | IN3R          | Analogue Input         | Right channel single-ended input 3                                   |

| F7     | XTO           | Analogue Output        | xtal output                                                          |

| G1     | GPIO5         | Digital Input / Output | Digital Microphone Input / General purpose input / output            |

| 51     | 51105         |                        | Important: See page 174 for start-up requirements.                   |

| G2     | DCVDD         | Supply                 | Digital Core Supply                                                  |

| G3     | DBVDD         | Supply                 | Digital Buffer Supply                                                |

| G4     | PLLVDD        | Supply                 | PLL Supply                                                           |

| G5     | PLLGND        | Supply                 | PLL Ground                                                           |

| G6     | CLKOUT5       | Analogue Output        | FLL / Oscillator Clock output                                        |

| G7     | MCLK / XTI    | Digital Input          | Master clock input / xtal input                                      |

### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Cirrus tests its package types according to IPC/JEDEC J-STD-020 for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at  $<30^{\circ}C / 85^{\circ}$  Relative Humidity. Not normally stored in moisture barrier bag. MSL2 = out of bag storage for 1 year at  $<30^{\circ}C / 60^{\circ}$  Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                       | MIN         | МАХ         |

|-------------------------------------------------|-------------|-------------|

| DCVDD, AVDD, PLLVDD                             | -0.3V       | +2.5V       |

| MICVDD and DBVDD                                | -0.3V       | +4.5V       |

| SPKVDD1, SPKVDD2                                | -0.3V       | +7.0V       |

| CPVDD                                           | -0.3V       | +2.2V       |

| Voltage range digital inputs                    | DGND -0.3V  | DBVDD +0.3V |

| Voltage range analogue inputs                   | AGND -0.3V  | AVDD +0.3V  |

| Voltage range analogue outputs (HPOUTL, HPOUTR) | -CPVDD-0.3V | +CPVDD+0.3V |

| Temperature Range, T <sub>A</sub>               | -40°C       | +85°C       |

| Junction Temperature, T <sub>JMAX</sub>         | -40°C       | +150°C      |

| Storage temperature after soldering             | -65°C       | +150°C      |

Notes:

1. Analogue, digital and speaker grounds must always be within 0.3V of each other.

2. All digital and analogue supplies are completely independent from each other (i.e. not internally connected).

- 3. AVDD must be less than or equal to MICVDD.

- 4. AVDD must be less than or equal to SPKVDD1 and SPKVDD2.

### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                        | SYMBOL                                            | MIN  | TYP | MAX | UNIT |

|--------------------------------------------------|---------------------------------------------------|------|-----|-----|------|

| Digital core supply range                        | DCVDD                                             | 1.62 | 1.8 | 2.0 | V    |

| Digital buffer supply range                      | DBVDD                                             | 1.62 | 1.8 | 3.6 | V    |

| Microphone bias supply range                     | MICVDD                                            | 1.7  | 2.5 | 3.6 | V    |

| Analogue supplies range                          | AVDD                                              | 1.7  | 1.8 | 2.0 | V    |

| PLL supply range                                 | PLLVDD                                            | 1.7  | 1.8 | 2.0 | V    |

| Charge pump supply range (1.8V supply operation) | CPVDD                                             | 1.7  | 1.8 | 2.0 | V    |

| Speaker supply range                             | SPKVDD1, SPKVDD2                                  | 1.7  | 5.0 | 5.5 | V    |

| Ground                                           | DGND, AGND, CPGND,<br>SPKGND1, SPKGND2,<br>PLLGND |      | 0   |     | V    |

Notes:

1. SPKVDD1 and SPKVDD2 must be high enough to support the peak output voltage when using CLASSD\_VOL function, to avoid output waveform clipping. Peak output voltage is AVDD\*CLASSD\_VOL.

2. The AGND and PLLGND pins must be tied together as close as possible to the WM8962.

The WM8962 can operate with PLLVDD tied to 0V; device power consumption may be reduced, but the crystal oscillator, PLLs and CLKOUT functions will not be supported.

### **ELECTRICAL CHARACTERISTICS**

#### **Test Conditions**

$$\label{eq:micvdd} \begin{split} \text{MicVdd} = \text{DCVdd} = \text{DBVdd} = \text{CPVdd} = \text{AVdd} = \text{PLLVdd} = 1.8\text{V}, \ \text{SPKVdd1} = \text{SPKVdd2} = 5\text{V}. \\ \text{T}_{\text{A}} = +25^{\circ}\text{C}, \ \text{1kHz} \ \text{signal}, \ \text{fs} = 48\text{kHz}, \ \text{PGA} \ \text{gain} = 0\text{dB}, \ 24\text{-bit} \ \text{audio} \ \text{data} \ \text{unless otherwise stated}. \end{split}$$

| PARAMETER                                                               | SYMBOL         | TEST CONDITIONS        | MIN | TYP                             | MAX | UNIT         |

|-------------------------------------------------------------------------|----------------|------------------------|-----|---------------------------------|-----|--------------|

| Analogue Inputs (IN1L, IN1R, IN4L                                       | , IN4R) to Inj | out PGA                |     |                                 |     |              |

| Full-scale Input Signal Level – note this changes in proportion to AVDD | VINFS          | Single-ended PGA input |     | 500<br>-6.02                    |     | mVrms<br>dBV |

| Input resistance                                                        |                | +24dB PGA gain         |     | 3.6                             |     | kΩ           |

|                                                                         |                | 0dB PGA gain           |     | 30.0                            |     |              |

|                                                                         |                | -23.25dB PGA gain      |     | 56.5                            |     |              |

| Input capacitance                                                       | Cin            |                        |     | 65                              |     | pF           |

| Analogue Inputs (IN2L, IN2R, IN3L                                       | , IN3R) to Inj | out PGA                |     |                                 |     |              |

| Full-scale Input Signal Level – note this changes in proportion to AVDD | VINFS          | Single-ended PGA input |     | 500<br>-6.02                    |     | mVrms<br>dBV |

| Input resistance                                                        |                | All gain settings      |     | 60                              |     | kΩ           |

| Input Programmable Gain Amplifie                                        | er (PGA)       | I                      |     |                                 |     |              |

| Minimum programmable gain                                               |                |                        |     | -23.25                          |     | dB           |

| Maximum programmable gain                                               |                |                        |     | 24                              |     | dB           |

| Programmable Gain Step Size                                             |                | Guaranteed monotonic   |     | 0.75                            |     | dB           |

| PGA Noise (referred to input)<br>(A-weighted)                           |                | IN1 and IN4            |     | -113                            |     | dBV          |

| PGA Noise (referred to input)<br>(A-weighted)                           |                | IN2 and IN3            |     | -113                            |     | dBV          |

| Mute Attenuation                                                        |                |                        |     | 100                             |     | dB           |

| Selectable Input Gain Boost (From                                       | n Input PGA    |                        |     |                                 |     |              |

| Gain Boost Steps                                                        |                | Input from PGA         |     | 0, 6, 13, 18,<br>20, 24, 27, 29 |     | dB           |

| Mute Attenuation                                                        |                |                        |     | 95                              |     | dB           |

| Selectable Input Gain to ADC Mixe                                       | er (From IN2,  | IN3)                   |     |                                 |     |              |

| Gain Boost Steps                                                        |                | Input from IN2 / IN3   |     | -12,-9, -6, -3,<br>0, 3, 6      |     | dB           |

| Mute Attenuation                                                        |                |                        | -   | 95                              |     | dB           |

$$\label{eq:micvdd} \begin{split} \text{MICVDD} = \text{DCVDD} = \text{DBVDD} = \text{CPVDD} = \text{AVDD} = \text{PLLVDD} = 1.8\text{V}, \ \text{SPKVDD1} = \text{SPKVDD2} = 5\text{V}. \\ \text{T}_{\text{A}} = +25^{\circ}\text{C}, \ \text{1kHz} \ \text{signal}, \ \text{fs} = 48\text{kHz}, \ \text{PGA} \ \text{gain} = 0\text{dB}, \ 24\text{-bit} \ \text{audio} \ \text{data} \ \text{unless} \ \text{otherwise} \ \text{stated}. \end{split}$$

$T_A = +25^{\circ}$ C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                              | SYMBOL        | TEST CONDITIONS                                             | MIN | TYP    | MAX | UNIT |

|--------------------------------------------------------|---------------|-------------------------------------------------------------|-----|--------|-----|------|

| Analogue Inputs (IN1L, IN1R) to                        | ADC out via l | nput PGA and Input Gain Bo                                  | ost |        |     |      |

| Signal to Noise Ratio<br>(A-weighted)                  | SNR           | ADC_HP=0<br>MIXIN_BIAS=100                                  |     | 91     |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input) | THD+N         | INPGA_BIAS=100                                              |     | -70    |     | dB   |

|                                                        |               | 'Option 1' (low power) bias settings - see Note 2.          |     |        |     |      |

| Signal to Noise Ratio<br>(A-weighted)                  | SNR           | ADC_HP=0<br>MIXIN_BIAS=011                                  |     | 91     |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input) | THD+N         | INPGA_BIAS=100                                              |     | -75    |     | dB   |

|                                                        |               | 'Option 2' bias settings -<br>see Note 2.                   |     |        |     |      |

| Signal to Noise Ratio<br>(A-weighted)                  | SNR           | ADC_HP=0<br>MIXIN_BIAS=000                                  | 81  | 91     |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input) | THD+N         | INPGA_BIAS=100                                              |     | -82    | -72 | dB   |

|                                                        |               | 'Option 3' bias settings -<br>see Note 2.                   |     |        |     |      |

| Signal to Noise Ratio<br>(A-weighted)                  | SNR           | ADC_HP=1<br>MIXIN_BIAS=000                                  |     | 93     |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input) | THD+N         | INPGA_BIAS=000                                              |     | -82    |     | dB   |

|                                                        |               | Option 4' (high performance)<br>bias settings - see Note 2. |     |        |     |      |

| ADC Channel Separation                                 |               | 1kHz                                                        |     | 95     |     | dB   |

|                                                        |               | 10kHz                                                       |     | 97     |     |      |

| PSRR (AVDD)                                            |               | 100mV(peak-peak) 1kHz                                       |     | 60     |     | dB   |

|                                                        |               | 100mV(peak-peak) 20kHz                                      |     | 40     |     |      |

| Channel Matching                                       |               | 1kHz signal                                                 |     | +/-0.5 |     | dB   |

$$\label{eq:micvdd} \begin{split} \mathsf{MICVDD} &= \mathsf{DCVDD} = \mathsf{DBVDD} = \mathsf{CPVDD} = \mathsf{AVDD} = \mathsf{PLLVDD} = 1.8\mathsf{V}, \ \mathsf{SPKVDD1} = \mathsf{SPKVDD2} = \mathsf{5V}. \\ \mathsf{T}_\mathsf{A} &= +25^\circ\mathsf{C}, \ \mathsf{1kHz} \ \mathsf{signal}, \ \mathsf{fs} = 48\mathsf{kHz}, \ \mathsf{PGA} \ \mathsf{gain} = \mathsf{0dB}, \ \mathsf{24}\text{-bit} \ \mathsf{audio} \ \mathsf{data} \ \mathsf{unless} \ \mathsf{otherwise} \ \mathsf{stated}. \end{split}$$

$I_A = +25^{\circ}$ C, 1kHz signal, is = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                       | SYMBOL        | TEST CONDITIONS                                              | MIN           | TYP | MAX | UNIT |

|-----------------------------------------------------------------|---------------|--------------------------------------------------------------|---------------|-----|-----|------|

| Analogue Inputs (IN2L, IN2R) to                                 | ADC out via l | nput Gain (Input PGA Bypass                                  | ed)           |     |     |      |

| Signal to Noise Ratio<br>(A-weighted)                           | SNR           | ADC_HP=0<br>MIXIN_BIAS=100                                   |               | 91  |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input)          | THD+N         | INPGA_BIAS=100                                               |               | -70 |     | dB   |

|                                                                 |               | 'Option 1' (low power) bias<br>settings - see Note 2.        |               |     |     |      |

| Signal to Noise Ratio<br>(A-weighted)                           | SNR           | ADC_HP=0<br>MIXIN_BIAS=011                                   |               | 91  |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input)          | THD+N         | INPGA_BIAS=100                                               |               | -75 |     | dB   |

|                                                                 |               | 'Option 2' bias settings -<br>see Note 2.                    |               |     |     |      |

| Signal to Noise Ratio<br>(A-weighted)                           | SNR           | ADC_HP=0<br>MIXIN_BIAS=000                                   |               | 91  |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input)          | THD+N         | INPGA_BIAS=100                                               |               | -85 |     | dB   |

|                                                                 |               | 'Option 3' bias settings -<br>see Note 2.                    |               |     |     |      |

| Signal to Noise Ratio<br>(A-weighted)                           | SNR           | ADC_HP=1<br>MIXIN_BIAS=000                                   |               | 94  |     | dB   |

| Total Harmonic Distortion Plus<br>Noise (-1dBFS input)          | THD+N         | INPGA_BIAS=000                                               |               | -85 |     | dB   |

|                                                                 |               | 'Option 4' (high performance)<br>bias settings - see Note 2. |               |     |     |      |

| ADC Channel Separation                                          |               | 1kHz                                                         |               | 95  |     | dB   |

|                                                                 |               | 10kHz                                                        |               | 87  |     |      |

| PSRR (AVDD)                                                     |               | 100mV(peak-peak) 1kHz                                        |               | 60  |     | dB   |

|                                                                 |               | 100mV(peak-peak) 20kHz                                       |               | 40  |     |      |

| Analogue Inputs (IN4L, IN4R) to<br>Low Power headphone playback | •             |                                                              | 2 / 50pF load | 1:  |     |      |

| Input Resistance                                                |               | +6dB PGA gain                                                |               | 10  |     | kΩ   |

|                                                                 |               | 0dB PGA gain                                                 |               | 17  |     |      |

|                                                                 |               | -15dB PGA gain                                               |               | 80  |     | -    |

| Signal to Noise Ratio<br>(A-weighted)                           | SNR           |                                                              |               | 97  |     | dB   |

| Total Harmonic Distortion Plus<br>Noise                         | THD+N         | 10kΩ, 50pF load                                              |               | -80 |     | dB   |

$\mathsf{MICVDD} = \mathsf{DCVDD} = \mathsf{DBVDD} = \mathsf{CPVDD} = \mathsf{AVDD} = \mathsf{PLLVDD} = \mathsf{1.8V}, \ \mathsf{SPKVDD1} = \mathsf{SPKVDD2} = \mathsf{5V}.$

$T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                          | SYMBOL | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |

|------------------------------------|--------|-----------------|-----|-----|-----|------|--|

| ADC Input Path Crosstalk           |        |                 |     |     |     |      |  |

| IN1 / IN4 ADC input path crosstalk |        | 1kHz            |     | -98 |     | dB   |  |

|                                    |        | 10kHz           |     | -79 |     |      |  |

| IN2 / IN3 ADC input path crosstalk |        | 1kHz            |     | -85 |     | dB   |  |

|                                    |        | 10kHz           |     | -65 |     |      |  |

| IN2 / IN4 ADC input path crosstalk |        | 1kHz            |     | -90 |     | dB   |  |

|                                    |        | 10kHz           |     | -69 |     |      |  |

| IN3 / IN4 ADC input path crosstalk |        | 1kHz            |     | -75 |     | dB   |  |

|                                    |        | 10kHz           |     | -55 |     |      |  |

MICVDD = DCVDD = DBVDD = CPVDD = AVDD = PLLVDD = 1.8V, SPKVDD1 = SPKVDD2 = 5V.

$T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                               | SYMBOL       | TEST CONDITIONS              | MIN         | TYP          | MAX           | UNIT    |

|-----------------------------------------|--------------|------------------------------|-------------|--------------|---------------|---------|

| HPOUTL/R_VOL                            |              |                              |             | ·            | •             |         |

| Minimum programmable gain               |              |                              |             | -68          |               | dB      |

| Maximum programmable gain               |              |                              |             | 6            |               | dB      |

| Volume Gain Step Size                   |              | Guaranteed monotonic         |             | 1            |               | dB      |

| Mute Attenuation                        |              |                              |             | 94           |               | dB      |

| HP1L/R_VOL                              |              |                              |             | ·            | •             |         |

| Minimum programmable gain               |              |                              |             | -7           |               | dB      |

| Maximum programmable gain               |              |                              |             | 0            |               | dB      |

| Volume Gain Step Size                   |              | Guaranteed monotonic         |             | 1            |               | dB      |

| DAC to HPOUTL/R (used as Line           | output) with | 10kΩ / 50pF load: Low Powe   | er headphon | e playback m | node (Note 3) |         |

| Full scale output voltage               |              | HPOUTL/R_VOL = 0dB           |             | 0.96         |               | Vrms    |

| Signal to Noise Ratio<br>(A-weighted)   | SNR          |                              | 87          | 97           |               | dB      |

| Total Harmonic Distortion Plus<br>Noise | THD+N        | 10kΩ load                    |             | -84          | -74           | dB      |

| Channel Separation                      |              | 1kHz full scale signal       |             | 93           |               | dB      |

|                                         |              | 10kHz full scale signal      |             | 86           |               |         |

| PSRR (AVDD)                             |              | 100mV(peak-peak) 1kHz        |             | 70           |               | dB      |

|                                         |              | 100mV(peak-peak) 20kHz       |             | 65           |               |         |

| DC offset                               |              | DC servo is enabled          | 0           |              | +/-1.2        | mV      |

| DAC to HPOUTL/R (used as Line           | output) with | 10kΩ / 50pF load: High Perfo | ormance hea | adphone play | back mode (l  | Note 3) |

| Signal to Noise Ratio<br>(A-weighted)   | SNR          |                              | 87          | 98           |               | dB      |

| Total Harmonic Distortion Plus<br>Noise | THD+N        | 10kΩ load                    |             | -84          | -74           | dB      |

MICVDD = DCVDD = DBVDD = CPVDD = AVDD = PLLVDD = 1.8V, SPKVDD1 = SPKVDD2 = 5V.  $T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                      | SYMBOL        | TEST CONDITIONS                          | MIN          | TYP    | MAX    | UNIT |

|--------------------------------|---------------|------------------------------------------|--------------|--------|--------|------|

| DAC to HPOUTL/R with headpho   | ne load: Low  | Power headphone playback                 | k mode (Note | e 3)   |        |      |

| Output Power at 1% THD+N       | Po            | R <sub>L</sub> =32Ω                      |              | 26     |        | mW   |

|                                |               | $R_L=16\Omega$                           |              | 31     |        |      |

| Total Harmonic Distortion Plus | THD+N         | R <sub>L</sub> =32Ω, P <sub>O</sub> =2mW |              | -79    |        | dB   |

| Noise                          |               |                                          |              | 0.011  |        | %    |

|                                |               | $R_L$ =32 $\Omega$ , $P_O$ =3.5mW        |              | -79    |        |      |

|                                |               |                                          |              | 0.011  |        |      |

|                                |               | R∟=32Ω, P₀=12mW                          |              | -78    |        |      |

|                                |               |                                          |              | 0.013  |        |      |

|                                |               | $R_L=16\Omega$ , $P_O=2mW$               |              | -81    |        |      |

|                                |               |                                          |              | 0.0089 |        |      |

|                                |               | $R_L=16\Omega$ , $P_O=22mW$              |              | -80    |        |      |

|                                |               |                                          |              | 0.010  |        |      |

| Output Noise Level             |               |                                          |              | -97    | -87    | dBV  |

| DC offset                      |               | DC servo is enabled                      | 0            |        | +/-1.2 | mV   |

| Channel Separation             |               | 1kHz test signal,                        |              | 95     |        | dB   |

|                                |               | $R_L$ =16 $\Omega$ , $P_O$ =22mW         |              |        |        |      |

|                                |               | 10kHz test signal,                       |              | 84     |        |      |

|                                |               | $R_L$ =16 $\Omega$ , $P_O$ =22mW         |              |        |        |      |

| DAC to HPOUTL/R with headpho   | ne load: High | Performance playback mod                 | de (Note 3)  |        |        |      |

| Total Harmonic Distortion Plus | THD+N         | $R_L$ =32 $\Omega$ , $P_O$ =12mW         |              | -84    |        | dB   |

| Noise                          |               |                                          |              | 0.0063 |        | %    |

|                                |               | $R_L$ =16 $\Omega$ , $P_O$ =22mW         |              | -81    |        |      |

|                                |               |                                          |              | 0.0089 |        |      |

| Output Noise Level             |               |                                          |              | -98    | -87    | dBV  |

MICVDD = DCVDD = DBVDD = CPVDD = AVDD = PLLVDD = 1.8V, SPKVDD1 = SPKVDD2 = 5V.

$T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                         | SYMBOL      | TEST CONDITIONS                                                                                                                                          | MIN      | TYP          | MAX         | UNIT    |

|-------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-------------|---------|

| SPKOUTL/R_VOL                                                     | •           |                                                                                                                                                          |          |              |             |         |

| Minimum programmable gain                                         |             |                                                                                                                                                          |          | -68          |             | dB      |

| Maximum programmable gain                                         |             |                                                                                                                                                          |          | 6            |             | dB      |

| Volume Gain Step Size                                             |             | Guaranteed monotonic                                                                                                                                     |          | 1            |             | dB      |

| Mute Attenuation                                                  |             |                                                                                                                                                          |          | 92           |             | dB      |

| DAC to Stereo Speaker Outputs load)                               | (DAC to SPK | OUTLP, SPKOUTLN, SPKOUT                                                                                                                                  | RP, SPKO | JTRN with 8Ω | + 22µH brid | ge tied |

| Output Power                                                      | Po          | 1% THD+N, $R_L = 8\Omega$ ,<br>SPKVDD1=SPKVDD2=5.5V                                                                                                      |          | 1.26         |             | W       |

|                                                                   |             | 1% THD+N, $R_L = 8Ω$ ,<br>SPKVDD1=SPKVDD2=1.7V                                                                                                           |          | 0.08         |             |         |

| Total Harmonic Distortion Plus<br>Noise                           | THD+N       | $P_0 = 200 \text{mW}, R_L = 8\Omega,$<br>SPKVDD1=SPKVDD2=3.3V                                                                                            |          | -68<br>0.040 |             | dB<br>% |

|                                                                   |             | $P_0 = 320 \text{mW}, R_L = 8\Omega,$<br>SPKVDD1=SPKVDD2=3.3V                                                                                            |          | -72<br>0.025 |             |         |

|                                                                   |             | $P_{O} = 320 \text{mW}, R_{L} = 8\Omega,$<br>SPKVDD1=SPKVDD2=5V                                                                                          |          | -67<br>0.045 | -55         |         |

|                                                                   |             | $\label{eq:powerserver} \begin{array}{l} P_{O} = 1W,  R_{L} = 8\Omega, \\ SPKVDD1 = SPKVDD2 = 5V, \\ CLASSD\_VOL = 110 \\ DACL/R\_VOL = C1h \end{array}$ |          | -61<br>0.089 |             |         |

| Signal to Noise Ratio<br>(A-weighted)<br>(DAC to speaker outputs) | SNR         | $\begin{array}{l} SPKVDD1{=}SPKVDD2{=}3.3V,\\ R_{L}=8\Omega,\\ Output\ signal\ {=}2.0Vrms \end{array}$                                                   |          | 90           |             | dB      |

| · · · · ·                                                         |             | $\begin{array}{l} SPKVDD1{=}SPKVDD2{=}5V,\\ R_{L}=8\Omega,\\ Output\ signal{=}2.8Vrms \end{array}$                                                       | 83       | 93           |             |         |

| PSRR (SPKVDD1/SPKVDD2)                                            | PSRR        | 100mV(peak-peak) 217Hz                                                                                                                                   |          | 78           |             | dB      |

|                                                                   |             | 100mV(peak-peak) 1kHz                                                                                                                                    |          | 78           |             | 7       |

MICVDD = DCVDD = DBVDD = CPVDD = AVDD = PLLVDD = 1.8V, SPKVDD1 = SPKVDD2 = 5V.  $T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                         | SYMBOL                       | SYMBOL TEST CONDITIONS                                                                                                                                 |                             | TYP              | MAX  | UNIT    |

|-------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|------|---------|

| DAC to Mono Speaker Output (D                                     | AC to SPKOL                  | JTLP/RP, SPKOUTLN/RN with                                                                                                                              | n <b>4</b> Ω <b>+ 22μ</b> Η | l bridge tied lo | oad) |         |

| Output Power                                                      | Po                           | 1% THD+N, $R_L = 4\Omega$ ,<br>SPKVDD1=SPKVDD2=5.5V                                                                                                    |                             | 2.45             |      | W       |

|                                                                   |                              | 1% THD+N, $R_L = 4\Omega$ ,<br>SPKVDD1=SPKVDD2=1.7V                                                                                                    |                             | 0.15             |      |         |

| Total Harmonic Distortion Plus<br>Noise                           | rmonic Distortion Plus THD+N |                                                                                                                                                        |                             | -64<br>0.063     |      | dB<br>% |

|                                                                   |                              | $P_{O} = 640 \text{mW}, R_{L} = 4\Omega,$<br>SPKVDD1=SPKVDD2=3.3V,                                                                                     |                             | -63<br>0.071     |      |         |

|                                                                   |                              | $P_{O} = 640 \text{mW}, R_{L} = 4\Omega,$<br>SPKVDD1=SPKVDD2=5V                                                                                        |                             | -67<br>0.044     |      |         |

|                                                                   |                              | $\label{eq:powerserver} \begin{array}{c} P_{O} = 2W,  R_{L} = 4\Omega, \\ SPKVDD1 = SPKVDD2 = 5V, \\ CLASSD_VOL = 110 \\ DACL/R_VOL = C1h \end{array}$ |                             | -61<br>0.089     |      |         |

| Signal to Noise Ratio<br>(A-weighted)<br>(DAC to speaker outputs) | SNR                          | $\label{eq:spkvdd1} \begin{array}{l} SPKVDD1 = SPKVDD2 = 3.3V, \\ R_L = 4\Omega, \\ Output \ signal = 2.0Vrms \end{array}$                             |                             | 90               |      | dB      |

| ,                                                                 |                              | $\label{eq:spkvdd} \begin{array}{l} SPKVDD1{=}SPKVDD2{=}5V,\\ R_{L}=4\Omega,\\ Output\ signal{=}2.8Vrms \end{array}$                                   |                             | 93               |      |         |

$\mathsf{MICVDD} = \mathsf{DCVDD} = \mathsf{DBVDD} = \mathsf{CPVDD} = \mathsf{AVDD} = \mathsf{PLLVDD} = \mathsf{1.8V}, \ \mathsf{SPKVDD1} = \mathsf{SPKVDD2} = \mathsf{5V}.$

$T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                                                      | SYMBOL               | TEST CONDITIONS                                  | MIN  | TYP             | MAX  | UNIT   |

|------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------|------|-----------------|------|--------|

| Analogue Reference Levels                                                                      |                      |                                                  |      |                 |      |        |

| Mid-rail Reference Voltage                                                                     | VMIDC                |                                                  | -3%  | AVDD/2          | +3%  | V      |

| Microphone Bias                                                                                |                      |                                                  |      |                 |      |        |

| Bias Voltage<br>(Note that MICVDD must be at<br>least 300mV higher than V <sub>MICBIAS</sub> ) | V <sub>MICBIAS</sub> | MICVDD=2.5V<br>2mA load current<br>MICBIAS_LVL=1 | -4%  | 1.156 ×<br>AVDD | +4%  | V      |

|                                                                                                |                      | MICVDD=2.5V<br>2mA load current<br>MICBIAS_LVL=0 | -4%  | 0.828 ×<br>AVDD | +4%  |        |

| PSRR (MICVDD)                                                                                  | PSRR                 | 100mV (peak-peak) 1kHz,<br>MICBIAS_LVL=1         |      | 74              |      | dB     |

| PSRR (AVDD)                                                                                    | PSRR                 | 100mV (peak-peak) 1kHz,<br>MICBIAS_LVL=1         |      | 52              |      | dB     |

| Maximum Bias Current Source                                                                    | IMICBIAS             |                                                  |      | 2               |      | mA     |

| Output Noise spectral density<br>@1kHz                                                         | Vst                  | MICBIAS_LVL=1                                    |      | 85              |      | nV/√Hz |

| <b>MICBIAS Current Detect Function</b>                                                         | (see Note 1          | )                                                |      |                 | •    | •      |

| Current Detect Threshold                                                                       |                      | MICDET_THR = 000                                 | 38   | 64              | 90   | μA     |

|                                                                                                |                      | MICDET_THR = 001                                 | -25% | 166             | +25% |        |

|                                                                                                |                      | MICDET_THR = 010                                 | -20% | 375             | +20% |        |

|                                                                                                |                      | MICDET_THR = 011                                 | -20% | 475             | +20% |        |

|                                                                                                |                      | MICDET_THR = 100                                 | -20% | 575             | +20% |        |

|                                                                                                |                      | MICDET_THR = 101                                 | -20% | 680             | +20% |        |

|                                                                                                |                      | MICDET_THR = 110                                 | -20% | 885             | +20% |        |

|                                                                                                |                      | MICDET_THR = 111                                 | -20% | 990             | +20% |        |

| Delay Time for Current Detect<br>Interrupt                                                     | t <sub>DET</sub>     |                                                  |      | 1.6             |      | ms     |

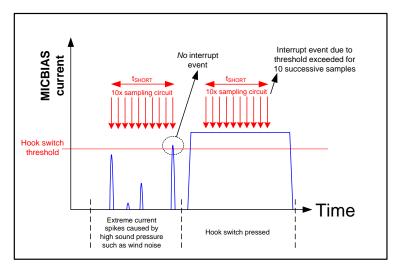

| <b>MICBIAS Short Circuit (Hook Swit</b>                                                        | ch) Detect F         | unction (see Note 1)                             |      |                 |      |        |

| Short Circuit Detect Threshold                                                                 |                      | MICSHORT_THR = 00                                | -18% | 515             | +18% | μA     |

|                                                                                                |                      | MICSHORT_THR = 01                                | -15% | 680             | +15% |        |

|                                                                                                |                      | MICSHORT_THR = 10                                | -15% | 1050            | +15% |        |

|                                                                                                |                      | MICSHORT_THR = 11                                | -15% | 1215            | +15% |        |

| Delay Time for<br>Short Circuit Detect Interrupt                                               | t <sub>short</sub>   |                                                  |      | 47              |      | ms     |

| Charge Pump                                                                                    |                      |                                                  |      |                 |      |        |

| Maximum Charge Pump switching<br>frequency                                                     | $CP_{FREQ}$          |                                                  |      | 1               |      | MHz    |

| Flyback capacitor<br>(between CPCA and CPCB pins)                                              | C <sub>FB</sub>      | at 2V                                            | 1    |                 |      | μF     |

| VPOS capacitor                                                                                 |                      | at 2V                                            | 2    |                 |      | μF     |

| VNEG capacitor                                                                                 |                      | at 2V                                            | 2    |                 |      | μF     |

| Charge pump start-up time                                                                      |                      |                                                  |      | 190             |      | μs     |

$\mathsf{MICVDD} = \mathsf{DCVDD} = \mathsf{DBVDD} = \mathsf{CPVDD} = \mathsf{AVDD} = \mathsf{PLLVDD} = 1.8\mathsf{V}, \ \mathsf{SPKVDD1} = \mathsf{SPKVDD2} = \mathsf{5V}.$

$T_A = +25^{\circ}C$ , 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                     | SYMBOL           | TEST CONDITIONS                                                                                                                           | MIN        | TYP   | MAX       | UNIT |

|---------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-----------|------|

| Crystal Oscillator                                            | 1                | 1                                                                                                                                         |            |       |           |      |

| External crystal frequency                                    |                  |                                                                                                                                           |            | 24    |           | MHz  |

| Oscillator load capacitance                                   |                  | XTI and XTO Pins                                                                                                                          |            | 10.5  |           | pF   |

| Start-up time                                                 |                  | measured from time when:<br>PLLVDD ≥ 1.7V,<br>AVDD ≥ 1.7V and<br>DVDD ≥ 1.62V,<br>until crystal output is stable<br>and in specification. |            | 1.5   |           | ms   |

| Phase Locked Loops (PLLs)                                     |                  |                                                                                                                                           |            |       |           |      |

| Output frequency                                              | Fout             |                                                                                                                                           | 22.5       |       | 50        | MHz  |

| Output duty cycle                                             |                  |                                                                                                                                           | 40         | 50    | 60        | %    |

| Start-up time (including Crystal<br>Oscillator start-up time) |                  | measured from time when:<br>PLLVDD ≥ 1.7V,<br>AVDD ≥ 1.7V and<br>DVDD ≥ 1.62V,<br>until PLL outputs are stable<br>and in specification.   |            | 1.5   |           | ms   |

| Frequency synthesis error                                     |                  |                                                                                                                                           |            | 0     |           | ppm  |

| Absolute clock period jitter (peak)                           |                  | Input Clock = 24MHz,<br>5pF load                                                                                                          |            | 500   |           | ps   |

| Short term jitter<br>(peak, cycle to cycle)                   |                  | N=1, 1000 samples,<br>Input Clock = 24MHz,<br>5pF load. (see Note 4)                                                                      |            | 150   |           | ps   |

| Long term jitter (peak)                                       |                  | N=1000, 1000 samples,<br>Input Clock = 24MHz,<br>5pF load. (see Note 4)                                                                   |            | 500   |           | ps   |

| MCLK / XTI input frequency range                              |                  |                                                                                                                                           | 14         |       | 40        | MHz  |

| Frequency Locked Loop (FLL)                                   |                  |                                                                                                                                           |            |       |           |      |

| Input frequency                                               | F <sub>REF</sub> | FLL_REFCLK_DIV = 00                                                                                                                       | 0.032      |       | 13.5      | MHz  |

|                                                               |                  | FLL_REFCLK_DIV = 01                                                                                                                       | 0.064      |       | 27        |      |

|                                                               |                  | FLL_REFCLK_DIV = 10                                                                                                                       | 0.128      |       | 36.864    |      |

| Output frequency                                              | Fout             |                                                                                                                                           | 1.875      |       | 50        | MHz  |

| Start-Up time                                                 |                  | VMID enabled; measured<br>from FLL_ENA=1 to clock<br>signal present on CLKOUTn.                                                           |            | 220   |           | μs   |

| Frequency synthesis error                                     |                  |                                                                                                                                           |            | 0     |           | ppm  |

| Start-Up time (free-running mode)                             |                  | VMID enabled; measured<br>from FLL_ENA=1 to clock<br>signal present on CLKOUTn.                                                           |            | 0.75  |           | μs   |

| Frequency accuracy (free-running mode)                        |                  | Reference clock<br>supplied initially                                                                                                     |            | +/-10 |           | %    |

|                                                               |                  | No reference clock<br>provided                                                                                                            |            | +/-30 |           | %    |

| Digital Input / Output                                        |                  |                                                                                                                                           |            |       |           |      |

| Input HIGH Level                                              | V <sub>IH</sub>  |                                                                                                                                           | 0.7×DBVDD  |       |           | V    |

| Input LOW Level                                               | V <sub>IL</sub>  |                                                                                                                                           |            |       | 0.3×DBVDD | V    |

| Output HIGH Level                                             | V <sub>он</sub>  | I <sub>OH</sub> =1mA                                                                                                                      | 0.9×DBVDD  |       |           | V    |

| Output LOW Level                                              | V <sub>OL</sub>  | I <sub>OL</sub> =-1mA                                                                                                                     |            |       | 0.1×DBVDD | V    |

| Input capacitance                                             |                  |                                                                                                                                           |            | 15    |           | pF   |

| Input leakage                                                 |                  |                                                                                                                                           | -0.9       |       | 0.9       | μA   |

| CLKOUTn output impedance                                      |                  |                                                                                                                                           | $ $ $\top$ | 160   |           | Ω    |

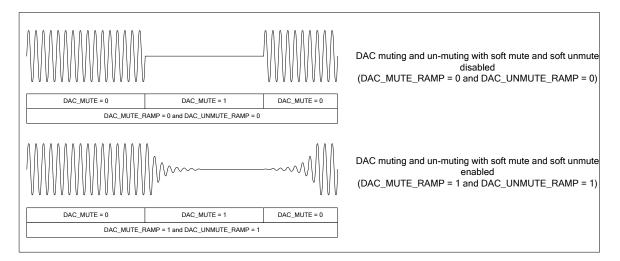

MICVDD = DCVDD = DBVDD = CPVDD = AVDD = PLLVDD = 1.8V, SPKVDD1 = SPKVDD2 = 5V.