## SX1280/SX1281

# Long Range, Low Power, 2.4 GHz Transceiver with Ranging Capability

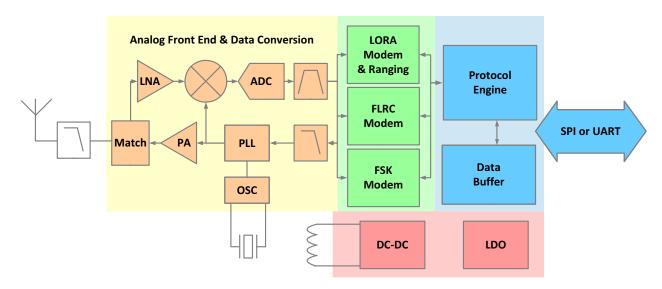

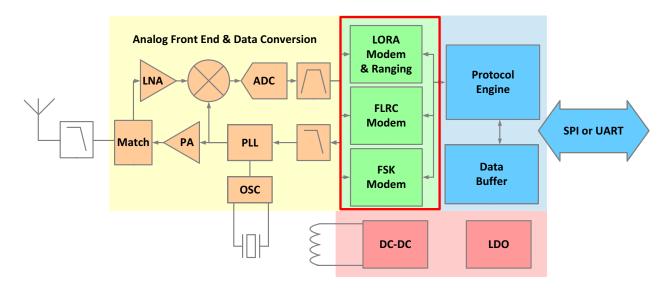

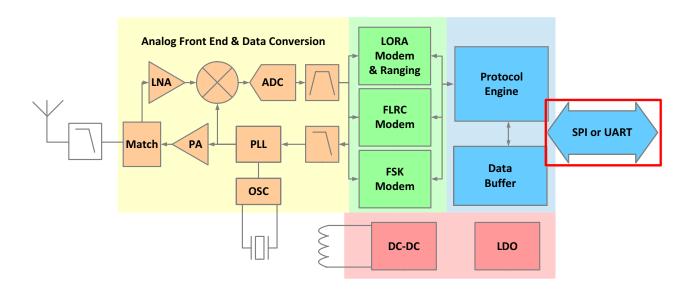

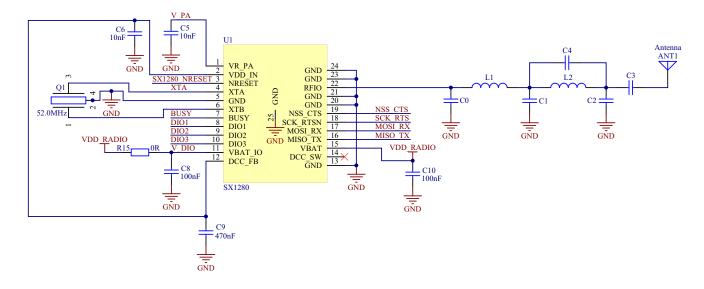

**Figure A: Transceiver Block Diagram**

#### **General Description**

The SX1280 and SX1281 transceivers provide ultra long range communication in the 2.4 GHz band with the linearity to withstand heavy interference. This makes them the ideal solution for robust and reliable wireless solutions. They are the first ISM band transceiver IC of their kind to integrate a time-of-flight functionality, opening up application solutions to track and localize people, pets, drones, or objects in a factory. These long range 2.4 GHz products include multiple physical layers and modulations to optimize long range communication at high data rate for video and security applications. Very small products for wearables can easily be designed thanks to the high level of integration and the ultra-low current consumption which allows the use of miniaturized batteries.

The radio is fully compliant with all worldwide 2.4 GHz radio regulations including EN 300 440, FCC CFR 47 Part 15 and the Japanese ARIB STD-T66.

The level of integration, low consumption and ranging function within the long range 2.4 GHz product line enable enhanced connectivity and provide additional functionality to a new generation of previously unconnected devices and applications.

#### **Key Features**

- · Long Range 2.4 GHz transceiver

- High sensitivity, down to -132 dBm

- +12.5 dBm, high efficiency PA

- Low energy consumption, on-chip DC-DC

- LoRa, FLRC, (G)FSK supported modulations

- Programmable bit rate

- · Excellent blocking immunity

- Ranging Engine, Time-of-flight function

- BLE PHY layer compatibility

- · Low system cost

### **Applications**

- Home automation & appliances

- · Security systems

- Tracking applications

- Wearables & sports/fitness sensors

- Radio-controlled toys & drones

- Smart watches & beacons

- Healthcare

# **Ordering Information**

| Part Number  | Delivery    | Order Quantity |

|--------------|-------------|----------------|

| SX1280IMLTRT | Tape & Reel | 3'000 pieces   |

| SX1281IMLTRT | Tape & Reel | 3'000 pieces   |

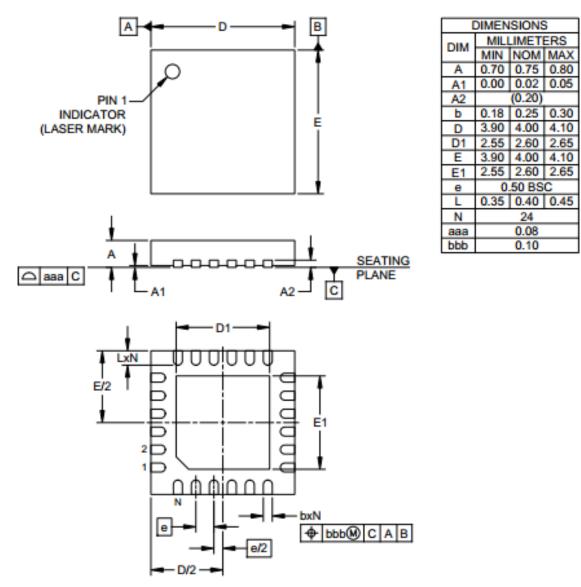

QFN 24 Package, with the temperature operating range from -40 to 85°C

Pb-free, Halogen free, RoHS/WEEE compliant product

## **Revision History**

| Version | ECO    | Date          | Changes and/or Modifications                                                                                                                                                                                                                                                                                                        |

|---------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev 1.0 | 035543 | February 2017 | First Release                                                                                                                                                                                                                                                                                                                       |

| Rev 1.1 | 037029 | May 2017      | Added table of effective data rates for the LoRa Modem Correction of the formulas for time-on-air in LoRa Correction of typos in the chapter Host Controller Interface Update of the application schematic with optional TCXO Update of the reference design BOM Deletion of redundant information in the chapter Thermal Impedance |

Rev 1.1

# **Table of Contents**

| General Description                             | 1  |

|-------------------------------------------------|----|

| Key Features                                    | 1  |

| Applications                                    | 1  |

| Ordering Information                            | 2  |

| Revision History                                | 2  |

| List of Figures                                 | 7  |

| List of Tables                                  | 8  |

| 1. Introduction                                 | 12 |

| 1.1 Analog Front End                            | 12 |

| 1.2 Power Distribution                          | 12 |

| 1.3 Modem                                       | 12 |

| 1.4 Packet Processing                           | 13 |

| 1.5 Digital Interface and Control               | 13 |

| 2. Pin Connections                              | 14 |

| 2.1 Transceiver Pinout                          | 14 |

| 2.2 Package view                                | 15 |

| 3. Specifications                               | 16 |

| 3.1 ESD Notice                                  | 16 |

| 3.2 Absolute Minimum and Maximum Ratings        | 16 |

| 3.3 Operating Range                             | 16 |

| 3.4 General Electrical Specifications           | 17 |

| 3.5 Receiver Electrical Specifications          | 18 |

| 3.5.1 Receiver Specifications                   | 18 |

| 3.5.2 LoRa Modem                                | 19 |

| 3.5.3 FLRC Modem                                | 20 |

| 3.5.4 FSK Modem                                 | 21 |

| 3.6 Transmitter Electrical Specifications       | 22 |

| 3.7 Crystal Oscillator Specifications           | 22 |

| 3.8 Digital Pin Levels                          | 23 |

| 4. Analog Front End                             | 24 |

| 4.1 Transmitter                                 | 24 |

| 4.2 Receiver                                    | 25 |

| 4.2.1 Low Power Mode and High Sensitivity Mode  | 26 |

| 4.3 PLL                                         | 26 |

| 4.4 RC Oscillators                              | 26 |

| 5. Power Distribution                           | 27 |

| 5.1 Selecting DC-DC Converter or LDO Regulation | 27 |

| 5.2 Flexible DIO Supply                         | 28 |

| 6. Digital Baseband                             | 29 |

| 6.1 Overview                                    | 29 |

| 6.2 LoRa Modem                                  | 30 |

| 6.2.1 LoRa Modulation                           | 30 |

| 6.2.2 Spreading Factor                          | 30 |

| 6.2.3 Bandwidth                                         | 31 |

|---------------------------------------------------------|----|

| 6.2.4 Forward Error Correction Coding Rate              | 31 |

| 6.2.5 Ranging Engine                                    | 31 |

| 6.3 FLRC Modem                                          | 32 |

| 6.3.1 Modem Bandwidth and Data Rates                    | 32 |

| 6.3.2 FEC Coding Rate                                   | 33 |

| 6.3.3 Gaussian Filtering                                | 34 |

| 6.4 FSK Modem                                           | 35 |

| 6.4.1 Modem Bandwidth and Data Rates                    | 35 |

| 6.4.2 Modem Modulation Index                            | 36 |

| 6.5 Guidance on Modem Selection                         | 37 |

| 7. Packet Engine                                        | 38 |

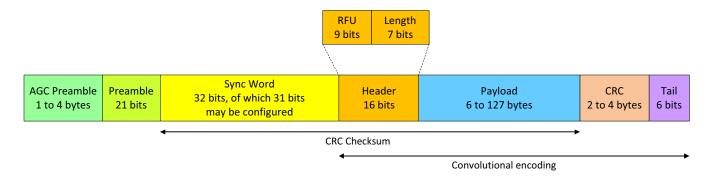

| 7.1 GFSK Packet                                         | 39 |

| 7.1.1 Fixed-length Packet                               | 39 |

| 7.1.2 Variable-length Packet                            | 39 |

| 7.2 BLE Packet Format                                   | 40 |

| 7.3 FLRC Packet                                         | 41 |

| 7.3.1 FLRC Packet Format                                | 41 |

| 7.3.2 Fixed-Length Packet Format                        | 41 |

| 7.3.3 Variable-length Packet Format                     | 42 |

| 7.3.4 FLRC Time-on-Air                                  | 42 |

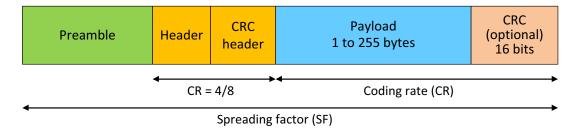

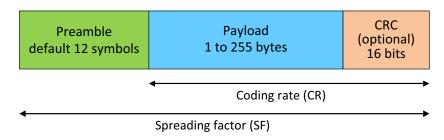

| 7.4 LoRa Packet                                         | 43 |

| 7.4.1 LoRa Packet Format                                | 43 |

| 7.4.2 Explicit (Variable-length) Header Mode            | 43 |

| 7.4.3 Implicit (Fixed-length) Header Mode               | 44 |

| 7.4.4 LoRa Time-on-Air                                  | 44 |

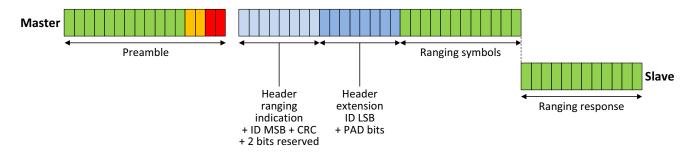

| 7.5 LoRa Ranging Engine Packet                          | 46 |

| 7.5.1 Ranging Packet Format                             | 46 |

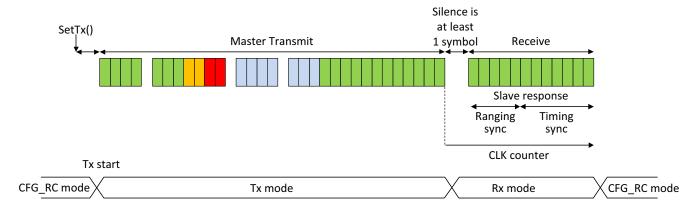

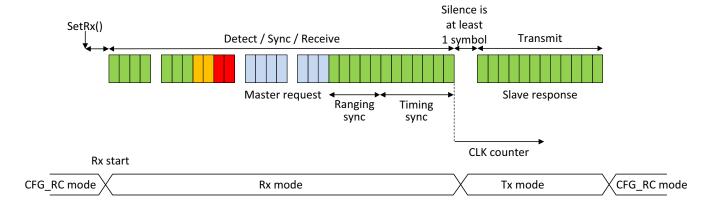

| 7.5.2 Ranging Master Exchange                           | 47 |

| 7.5.3 Ranging Slave Exchange                            | 47 |

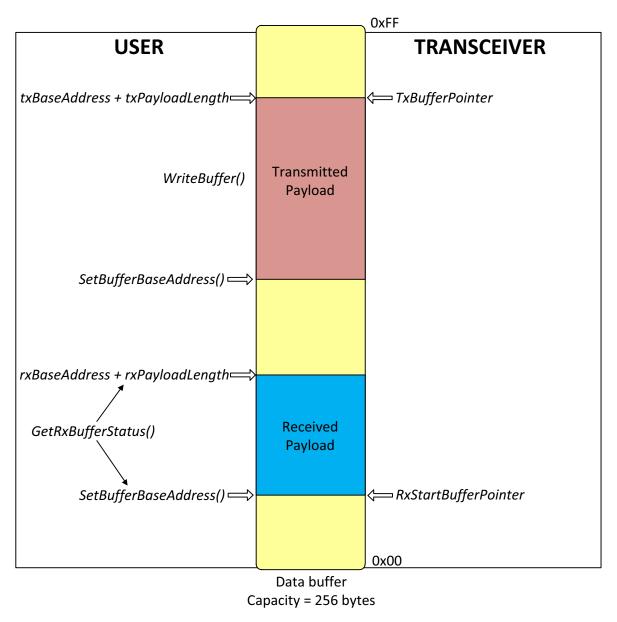

| 8. Data Buffer                                          | 48 |

| 8.1 Principle of Operation                              | 48 |

| 8.2 Receive Operation                                   | 49 |

| 8.3 Transmit Operation                                  | 49 |

| 8.4 Using the Data buffer                               | 49 |

| 9. Digital Interface and Control                        | 50 |

| 9.1 BUSY Pin Communication                              | 50 |

| 9.2 Interface Detection                                 | 50 |

| 9.3 SPI Interface                                       | 51 |

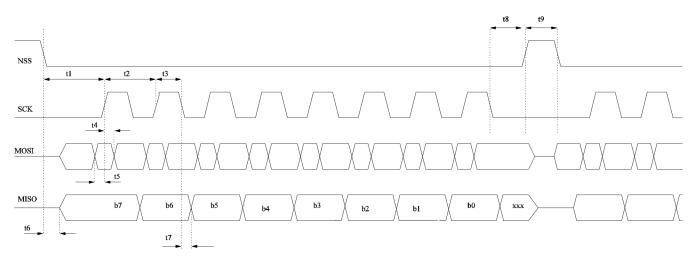

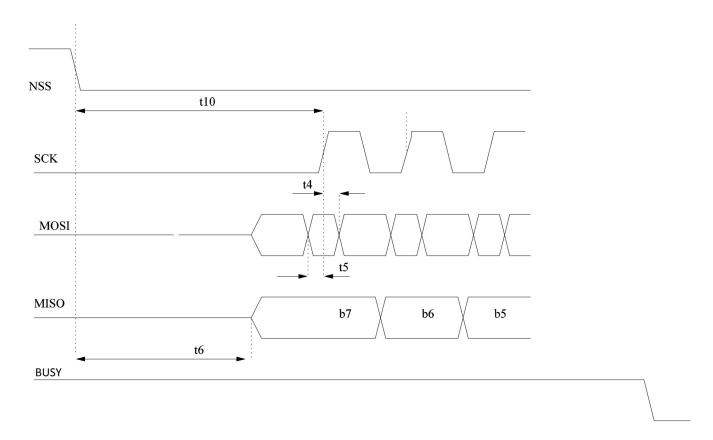

| 9.3.1 SPI Timing When the Transceiver is in Active Mode | 51 |

| 9.3.2 SPI Timing When the Transceiver Leaves Sleep Mode | 52 |

| 9.3.3 SPI Timings                                       | 53 |

| 9.4 UART Interface                                      | 54 |

| 9.5 Pin Sharing                                         | 54 |

| 9.6 Multi-Purpose Digital Input/Output (DIO)            | 54 |

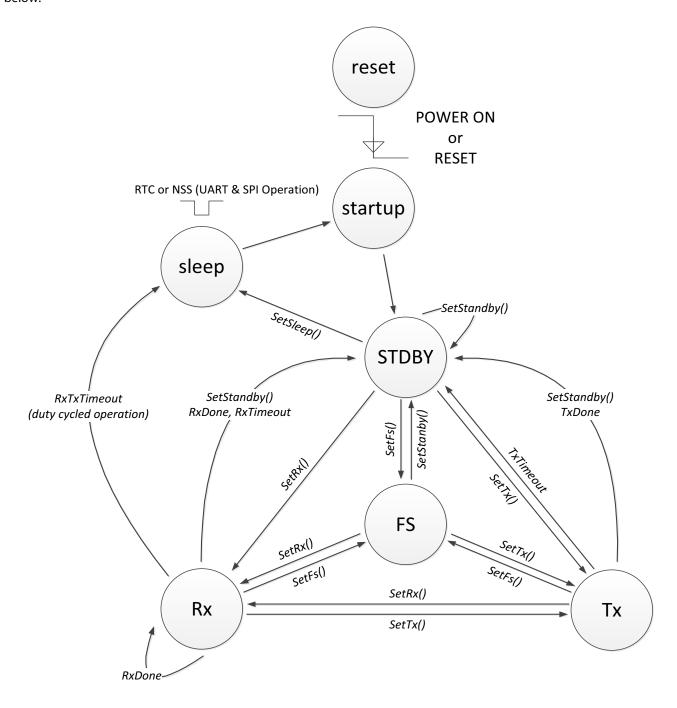

| 10. Operational Modes                                   | 55 |

Rev 1.1

| 10.1 Startup                                          | 55 |

|-------------------------------------------------------|----|

| 10.2 Sleep Mode                                       | 55 |

| 10.3 Standby Mode                                     | 56 |

| 10.4 Frequency Synthesis (FS) Mode                    | 56 |

| 10.5 Receive (Rx) Mode                                | 56 |

| 10.6 Transmit (Tx) Mode                               | 56 |

| 10.7 Transceiver Circuit Modes Graphical Illustration | 57 |

| 10.8 Active Mode Switching Time                       | 58 |

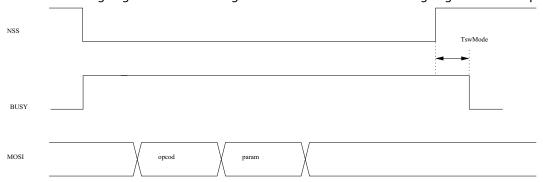

| 11. Host Controller Interface                         | 59 |

| 11.1 Command Structure                                | 59 |

| 11.2 GetStatus Command                                | 60 |

| 11.3 Register Access Operations                       | 61 |

| 11.3.1 WriteRegister Command                          | 61 |

| 11.3.2 ReadRegister Command                           | 62 |

| 11.4 Data Buffer Operations                           | 63 |

| 11.4.1 WriteBuffer Command                            | 63 |

| 11.4.2 ReadBuffer                                     | 63 |

| 11.5 Radio Operation Modes                            | 64 |

| 11.5.1 SetSleep                                       | 64 |

| 11.5.2 SetStandby                                     | 64 |

| 11.5.3 SetFs                                          | 65 |

| 11.5.4 SetTx                                          | 65 |

| 11.5.5 SetRx                                          | 66 |

| 11.5.6 SetRxDutyCycle                                 | 67 |

| 11.5.7 SetLongPreamble                                | 68 |

| 11.5.8 SetCAD                                         | 69 |

| 11.5.9 SetTxContinuousWave                            | 69 |

| 11.5.10 SetTxContinuousPreamble                       | 69 |

| 11.5.11 SetAutoTx                                     | 70 |

| 11.5.12 SetAutoFs                                     | 70 |

| 11.6 Radio Configuration                              | 71 |

| 11.6.1 SetPacketType                                  | 71 |

| 11.6.2 GetPacketType                                  | 72 |

| 11.6.3 SetRfFrequency                                 | 72 |

| 11.6.4 SetTxParams                                    | 72 |

| 11.6.5 SetCadParams                                   | 73 |

| 11.6.6 SetBufferBaseAddress                           | 74 |

| 11.6.7 SetModulationParams                            | 74 |

| 11.6.8 SetPacketParams                                | 75 |

| 11.7 Communication Status Information                 | 77 |

| 11.7.1 GetRxBufferStatus                              | 77 |

| 11.7.2 GetPacketStatus                                | 77 |

| 11.7.3 GetRssilnst                                    | 80 |

| 11.8 IRQ Handling                                     | 80 |

| 11.8.1 SetDiolrqParams                                | 81 |

| 11.8.2 GetlrqStatus                                   | 82 |

Rev 1.1

| 11.8.3 ClearIrqStatus                               | 82  |

|-----------------------------------------------------|-----|

| 12. List of Commands                                | 83  |

| 13. Transceiver Operation                           | 85  |

| 13.1 GFSK Packet                                    | 85  |

| 13.1.1 Common Transceiver Settings                  | 85  |

| 13.1.2 Tx Setting and Operations                    | 91  |

| 13.1.3 Rx Setting and Operations                    | 92  |

| 13.2 BLE Packet                                     | 94  |

| 13.2.1 Common Transceiver Settings                  | 94  |

| 13.2.2 Tx Setting and Operations                    | 98  |

| 13.2.3 Rx Setting and Operations                    | 99  |

| 13.2.4 BLE Specific Functions                       | 101 |

| 13.3 FLRC Packet                                    | 102 |

| 13.3.1 Common Transceiver Settings                  | 102 |

| 13.3.2 Tx Setting and Operations                    | 107 |

| 13.3.3 Rx Setting and Operations                    | 108 |

| 13.4 LoRa Packet                                    | 111 |

| 13.4.1 Common Transceiver Settings for LoRa         | 111 |

| 13.4.2 Tx Setting and Operations                    | 114 |

| 13.4.3 Rx Setting and Operations                    | 114 |

| 13.5 Settings for Ranging                           | 116 |

| 13.5.1 Ranging Device Setting                       | 116 |

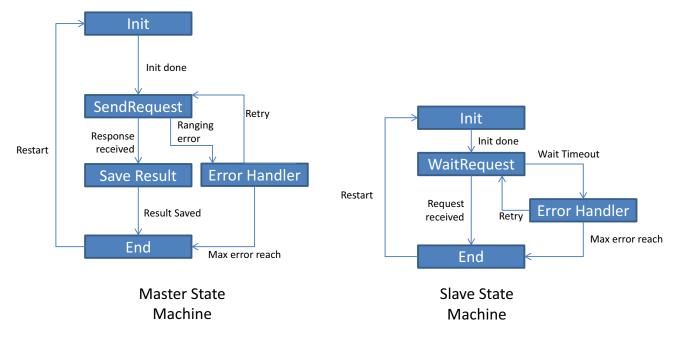

| 13.5.2 Ranging Operation as State Machines          | 120 |

| 13.6 Miscellaneous Functions                        | 121 |

| 13.6.1 SetRegulatorMode Command                     | 121 |

| 13.6.2 Context Saving                               | 121 |

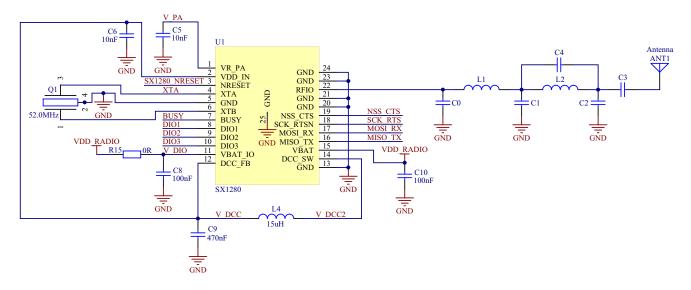

| 14. Reference Design and Application Schematics     | 122 |

| 14.1 Reference Design                               | 122 |

| 14.1.1 Application Design Schematic                 | 122 |

| 14.1.2 Reference Design BOM                         | 123 |

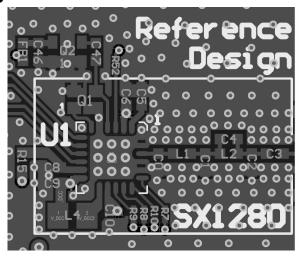

| 14.1.3 Reference Design PCB                         | 123 |

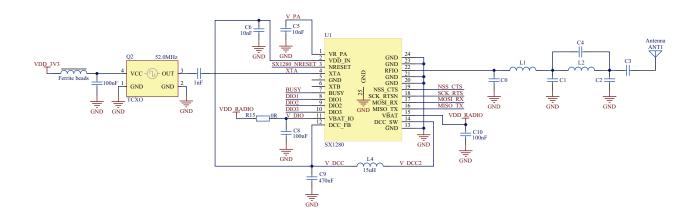

| 14.2 Application Design with optional TCXO          | 124 |

| 14.3 Application Design with Low Drop Out Regulator | 124 |

| 14.4 Sleep Mode Consumption                         | 125 |

| 15. Packaging Information                           | 126 |

| 15.1 Package Outline Drawing                        | 126 |

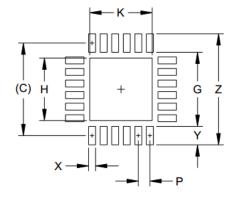

| 15.2 Land Pattern                                   | 127 |

| 15.3 Reflow Profiles                                | 127 |

| 15.4 Thermal Impedance                              | 127 |

| Glossary                                            | 128 |

Rev 1.1

# **List of Figures**

| Figure 2-1: Transceiver Pin Locations                                    | 15  |

|--------------------------------------------------------------------------|-----|

| Figure 4-1: Transceiver Block Diagram, Analog Front End Highlighted      | 24  |

| Figure 5-1: Transceiver Block Diagram, Power Distribution Highlighted    | 27  |

| Figure 5-2: Separate DIO Supply                                          | 28  |

| Figure 6-1: Transceiver Block Diagram, Modems Highlighted                | 29  |

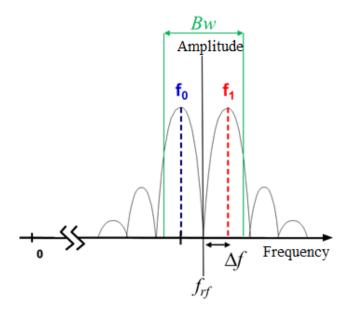

| Figure 6-2: FSK Modulation Parameters                                    | 35  |

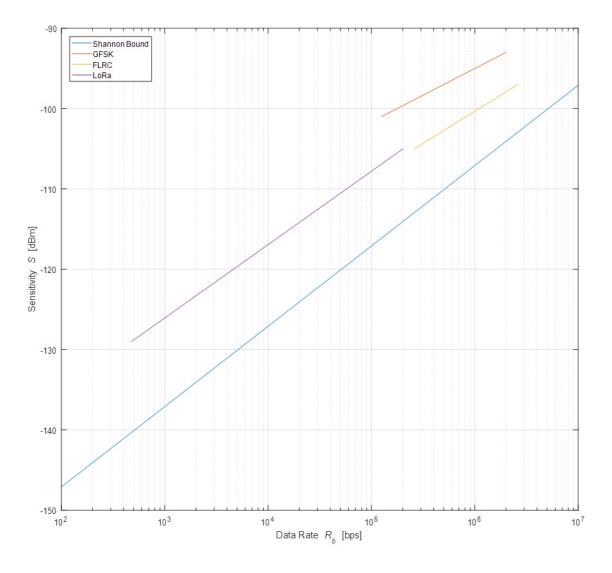

| Figure 6-3: Sensitivity Performance of the Transceiver Modems            | 37  |

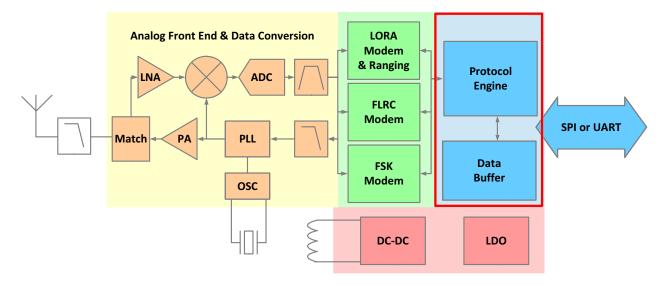

| Figure 7-1: Transceiver Block Diagram, Packet Engine Highlighted         | 38  |

| Figure 7-2: Fixed-length Packet Format                                   | 39  |

| Figure 7-3: Variable-length Packet Format                                | 39  |

| Figure 7-4: BLE Packet Format                                            | 40  |

| Figure 7-5: PDU Header Format                                            | 40  |

| Figure 7-6: FLRC Fixed-length Packet Format                              | 41  |

| Figure 7-7: FLRC Variable-length Packet Format                           | 42  |

| Figure 7-8: LoRa Variable-length Packet Format                           | 43  |

| Figure 7-9: LoRa Fixed-length Packet Format                              | 44  |

| Figure 7-10: Ranging Packet Format                                       | 46  |

| Figure 7-11: Ranging Master Packet Exchange                              | 47  |

| Figure 7-12: Ranging Slave Packet Exchange                               | 47  |

| Figure 8-1: Data Buffer Diagram                                          | 48  |

| Figure 9-1: Transceiver Block Diagram, Digital Interface Highlighted     | 50  |

| Figure 9-2: SPI Timing Diagram                                           | 51  |

| Figure 9-3: SPI Timing Transition                                        | 52  |

| Figure 10-1: Transceiver Circuit Modes                                   | 57  |

| Figure 10-2: Switching Time Definition in Active Mode                    | 58  |

| Figure 13-1: Ranging State Machines 1                                    | 120 |

| Figure 14-1: Transceiver Application Design Schematic                    | 122 |

| Figure 14-2: Long Range Reference Design PCB Layout 1                    | 123 |

| Figure 14-3: Application Schematic with Optional TCXO 1                  | 124 |

| Figure 14-4: Application Schematic with Low Drop Out Regulator Schematic | 124 |

| Figure 15-1: QFN 4x4 Package Outline Drawing 1                           | 126 |

| Figure 15-2: OFN 4x4mm Land Pattern 1                                    | 127 |

Rev 1.1

# **List of Tables**

| Table 1-1: Product Portfolio and Modem Functionality                                     | 12 |

|------------------------------------------------------------------------------------------|----|

| Table 2-1: Transceiver Pinout                                                            | 14 |

| Table 3-1: Minimum and Maximum Ratings                                                   | 16 |

| Table 3-2: Operating Range                                                               | 16 |

| Table 3-3: General Electrical Specifications                                             | 17 |

| Table 3-4: Receiver Specifications                                                       | 18 |

| Table 3-5: LoRa Modem Specifications                                                     | 19 |

| Table 3-6: FLRC Modem Specifications                                                     | 20 |

| Table 3-7: FSK Modem Specifications                                                      | 21 |

| Table 3-8: Transmitter Electrical Specifications                                         | 22 |

| Table 3-9: Crystal Oscillator Specifications                                             | 22 |

| Table 3-10: Digital Levels and Timings                                                   | 23 |

| Table 4-1: Procedure for Receiver Gain Manual Setting                                    | 25 |

| Table 4-2: Receiver Gain Manual Setting                                                  | 25 |

| Table 5-1: Regulation Type versus Circuit Mode                                           | 27 |

| Table 6-1: Receiver Sensitivity when using LoRa                                          | 30 |

| Table 6-2: Effective Data Rates when using LoRa                                          | 31 |

| Table 6-3: Valid FLRC Data Rate and Bandwidth Combinations                               | 32 |

| Table 6-4: Effective FLRC Data Rates Based upon FEC Usage with Resulting Sensitivities   | 33 |

| Table 6-5: Receiver Performance of the FLRC Modem                                        | 34 |

| Table 6-6: Valid FSK Data Rate and Bandwidth Combinations with Resulting Sensitivities . | 36 |

| Table 9-1: SPI Timing Requirements                                                       | 53 |

| Table 10-1: SX1280 Operating Modes                                                       | 55 |

| Table 10-2: Switching Time (TswMode) for all Possible Transitions                        | 58 |

| Table 11-1: SPI interface Command Sequence                                               | 59 |

| Table 11-2: UART Interface Command Sequence                                              | 59 |

| Table 11-3: Status Byte Definition                                                       | 60 |

| Table 11-4: GetStatus Data Transfert (SPI)                                               | 61 |

| Table 11-5: GetStatus Data Transfert (UART)                                              | 61 |

| Table 11-6: WriteRegister Data Transfer (SPI)                                            | 61 |

| Table 11-7: WriteRegister Data Transfer (UART)                                           | 61 |

| Table 11-8: ReadRegister Data Transfer (SPI)                                             |    |

| Table 11-9: ReadRegister Data Transfer (UART)                                            | 62 |

| Table 11-10: WriteBuffer SPI Data Transfer                                               | 63 |

| Table 11-11: WriteBuffer UART Data Transfer                                              | 63 |

| Table 11-12: ReadBuffer SPI Data Transfer                                                | 63 |

| Table 11-13: ReadBuffer UART Data Transfer                                               | 63 |

| Table 11-14: SetSleep SPI Data Transfer                                                  | 64 |

| Table 11-15: Sleep Mode Definition                                                       | 64 |

| Table 11-16: SetStandby SPI Data Transfer                                                | 64 |

| Table 11-17: SetStandby UART Data Transfer                                               | 65 |

| Table 11-18: Standby Config Definition                                                   |    |

| Table 11-19: SetFs Data Transfer                                                         | 65 |

| Table 11-20: SetTx SPI Data Transfer                   | 65 |

|--------------------------------------------------------|----|

| Table 11-21: SetTx UART Data Transfer                  | 65 |

| Table 11-22: SetTx Time-out Definition                 | 66 |

| Table 11-23: SetTx Time-out Duration                   | 66 |

| Table 11-24: SetRx SPI Data Transfer                   | 66 |

| Table 11-25: SetRx UART Data Transfer                  | 66 |

| Table 11-26: SetRx Time-out Duration                   | 67 |

| Table 11-27: Duty Cycled Operation SPI Data Transfer   | 67 |

| Table 11-28: Duty Cycled Operation UART Data Transfer  | 67 |

| Table 11-29: Rx Duration Definition.                   | 68 |

| Table 11-30: SetLongPreamble Data Transfer             | 68 |

| Table 11-31: SetCAD Data Transfer                      | 69 |

| Table 11-32: SetTxContinuousWave Data Transfer         | 69 |

| Table 11-33: SetTxContinuousPreamble Data Transfer     | 69 |

| Table 11-34: SetAutoTx SPI Data Transfer               | 70 |

| Table 11-35: SetAutoTx UART Data Transfer              | 70 |

| Table 11-36: SetAutoFs SPI Data Transfer               | 70 |

| Table 11-37: SetAutoFs UART Data Transfer              | 70 |

| Table 11-38: SetPacketType SPI Data Transfer           | 71 |

| Table 11-39: SetPacketType UART Data Transfer          |    |

| Table 11-40: PacketType Definition                     | 71 |

| Table 11-41: GetPacketType SPI Data Transfer           | 72 |

| Table 11-42: GetPacketType UART Data Transfer          | 72 |

| Table 11-43: SetRfFrequency SPI Data Transfer          | 72 |

| Table 11-44: SetRfFrequency UART Data Transfer         | 72 |

| Table 11-45: SetTxParams SPI Data Transfer             | 72 |

| Table 11-46: SetTxParams UART Data Transfer            | 73 |

| Table 11-47: RampTime Definition                       | 73 |

| Table 11-48: CAD SPI Data Transfer                     | 73 |

| Table 11-49: CAD UART Data Transfer                    | 73 |

| Table 11-50: CadSymbolNum Definition                   | 74 |

| Table 11-51: SetBufferBaseAddress SPI Data Transfer    | 74 |

| Table 11-52: SetBufferBaseAddress UART Data Transfer   | 74 |

| Table 11-53: SetModulationParams SPI Data Transfer     | 74 |

| Table 11-54: SetModulationParams UART Data Transfer    | 74 |

| Table 11-55: SetModulationParams Parameters Definition | 75 |

| Table 11-56: SetPacketParams SPI Data Transfer         | 75 |

| Table 11-57: SetPacketParams UART Data Transfer        | 75 |

| Table 11-58: SetPacketParams Parameters Definition     | 76 |

| Table 11-59: GetRxBufferStatus SPI Data Transfer       | 77 |

| Table 11-60: GetRxBufferStatus UART Data Transfer      | 77 |

| Table 11-61: GetPacketStatus SPI Data Transfer         | 77 |

| Table 11-62: GetPacketStatus UART Data Transfer        | 78 |

| Table 11-63: packetStatus Definition                   | 78 |

| Table 11-64: RSSI and SNR Packet Status                | 78 |

| Table 11-65: Status Packet Status Byte                 | 79 |

| Table 11-66: Error Packet Status Byte                                   | 79  |

|-------------------------------------------------------------------------|-----|

| Table 11-67: Sync Packet Status Byte                                    | 79  |

| Table 11-68: GetRssilnst SPI Data Transfer                              | 80  |

| Table 11-69: GetRssilnst UART Data Transfer                             | 80  |

| Table 11-70: Rssilnst Definition                                        | 80  |

| Table 11-71: IRQ Register                                               | 80  |

| Table 11-72: IRQ Mask Definition SPI Data Transfer                      | 81  |

| Table 11-73: IRQ Mask Definition UART Data Transfer                     | 81  |

| Table 11-74: GetIrqStatus SPI Data Transfer                             | 82  |

| Table 11-75: GetIrqStatus UART Data Transfer                            | 82  |

| Table 11-76: ClearIrqStatus SPI Data Transfer                           | 82  |

| Table 11-77: ClearIrqStatus UART Data Transfer                          | 82  |

| Table 12-1: Transceiver Available Commands                              | 83  |

| Table 13-1: Modulation Parameters in GFSK Mode                          | 85  |

| Table 13-2: Modulation Parameters in GFSK Mode                          | 86  |

| Table 13-3: Modulation Parameters in GFSK Mode                          | 87  |

| Table 13-4: Preamble Length Definition in GFSK Packet                   | 87  |

| Table 13-5: Sync Word Length Definition in GFSK Packet                  | 88  |

| Table 13-6: Sync Word Combination in GFSK Packet                        | 88  |

| Table 13-7: Packet Type Definition in GFSK Packet                       | 88  |

| Table 13-8: Payload Length Definition in GFSK Packet                    | 89  |

| Table 13-9: CRC Definition in GFSK Packet                               | 89  |

| Table 13-10: Whitening Enabling in GFSK Packet                          | 89  |

| Table 13-11: Sync Word Definition in GFSK Packet                        | 89  |

| Table 13-12: CRC Initialisation Registers                               | 90  |

| Table 13-13: CRC Polynomial Definition                                  | 90  |

| Table 13-14: PacketStatus[3] in GFSK Packet                             | 91  |

| Table 13-15: PacketStatus[2] in GFSK Packet                             | 93  |

| Table 13-16: PacketStatus[4] in GFSK Mode Packet                        | 93  |

| Table 13-17: Modulation Parameters in BLE and GFSK Mode                 | 94  |

| Table 13-18: Modulation Parameters in BLE and GFSK Mode                 | 95  |

| Table 13-19: Modulation Parameters in BLE and GFSK Mode                 | 95  |

| Table 13-20: Connection State Definition in BLE Packet                  | 96  |

| Table 13-21: CRC Definition in BLE Packet                               | 96  |

| Table 13-22: Tx Test Packet Payload in Test Mode for BLE Packet         | 96  |

| Table 13-23: Whitening Enabling in BLE Packet                           | 97  |

| Table 13-24: Sync Word Definition in BLE Packet                         | 97  |

| Table 13-25: CRC Initialisation Registers                               | 97  |

| Table 13-26: PacketStatus3 in BLE Packet                                | 98  |

| Table 13-27: PacketStatus2 in BLE Mode                                  | 99  |

| Table 13-28: PacketStatus4 in BLE Mode                                  | 100 |

| Table 13-29: SetAutoTx Mode                                             | 101 |

| Table 13-30: Modulation Parameters in FLRC Mode: Bandwidth and Bit Rate | 102 |

| Table 13-31: Modulation Parameters in FLRC Mode: Coding Rate            | 103 |

| Table 13-32: Modulation Parameters in FLRC Mode: BT                     | 103 |

| Table 13-33: AGC Preamble Length Definition in FLRC Packet              | 103 |

| Table 13-34: Sync Word Length Definition in FLRC Packet         | 104   |

|-----------------------------------------------------------------|-------|

| Table 13-35: Sync Word Combination in FLRC Packet               | 104   |

| Table 13-36: Packet Type Definition in FLRC Packet              | 105   |

| Table 13-37: Payload Length Definition in FLRC Packet           | 105   |

| Table 13-38: CRC Definition in FLRC Packet                      | 105   |

| Table 13-39: CRC Initialisation Registers                       | 105   |

| Table 13-40: CRC Polynomial Definition                          | 106   |

| Table 13-41: Whitening Definition in FLRC Packet                | 106   |

| Table 13-42: Sync Word Definition in FLRC Packet                | 106   |

| Table 13-43: PacketStatus3 in FLRC Packet                       | 107   |

| Table 13-44: PacketStatus2 in FLRC Packet                       | 109   |

| Table 13-45: PacketStatus3 in FLRC Packet                       | 109   |

| Table 13-46: PacketStatus4 in FLRC Packet                       | 110   |

| Table 13-47: Modulation Parameters in LoRa Mode                 | . 111 |

| Table 13-48: Modulation Parameters in LoRa Mode                 | 112   |

| Table 13-49: Modulation Parameters in LoRa Mode                 | 112   |

| Table 13-50: Preamble Definition in LoRa or Ranging             | . 113 |

| Table 13-51: Packet Type Definition in LoRa or Ranging Packet   | 113   |

| Table 13-52: Payload Length Definition in LoRa Packet           | 113   |

| Table 13-53: CRC Enabling in LoRa Packet                        | 113   |

| Table 13-54: IQ Swapping in LoRa or Ranging Packet              | 113   |

| Table 13-55: Ranging Device Modulation Parameters               | 116   |

| Table 13-56: Slave Ranging Request Address Definition           | 117   |

| Table 13-57: Register Address Bit Definition                    | 117   |

| Table 13-58: Master Ranging Request Address Definition          | 117   |

| Table 13-59: Calibration Value in Register                      |       |

| Table 13-60: Ranging Role Value                                 | 118   |

| Table 13-61: Register Result Address                            | 119   |

| Table 13-62: Ranging Result Type Selection                      | 119   |

| Table 13-63: Power Regulation Selection SPI Data Transfer       | 121   |

| Table 13-64: Power Regulation Selection UART Data Transfer      |       |

| Table 13-65: RegModeParam Definition                            | 121   |

| Table 13-66: SetSaveContext Data Transfer                       |       |

| Table 14-1: Reference Design BOM                                |       |

| Table 14-2: Host Settings for Minimizing Sleep Mode Consumption | 125   |

## 1. Introduction

The SX1280 and SX1281 are half-duplex transceivers capable of low power operation in the worldwide 2.4 GHz ISM band. The radio comprises 5 main parts, which are described in the following chapters.

## 1.1 Analog Front End

The radio features a high efficiency +12.5 dBm transmitter and a high linearity receive chain that are both accessed via a common antenna port pin. Frequency conversion between RF and baseband (low-IF) is governed by a digital PLL that is referenced to a 52 MHz crystal. Both transmit and receive chains are interfaced by data converters to the ensuing digital blocks. For more information see the Section 4. "Analog Front End" on page 24.

#### 1.2 Power Distribution

Two forms of voltage regulation are available, either a integrated Low-DropOut (LDO) or a high efficiency buck (step down) DC to DC converter. This allows the designer to choose between high energy efficiency or miniaturisation of the radio depending upon the design priorities of the application. For more information, please see the Section 5. "Power Distribution" on page 27.

### 1.3 Modem

There are a range of modulation options available in the LoRa family's three modems, each of which has packet options that include many MAC layer functionalities. For a description of each modulation format and the performance benefits associated with that modulation, please see the corresponding section below:

- LoRa Modem and Packet: Section 6.2 "LoRa Modem" on page 30

- FLRC Modem and Packet: Section 6.3 "FLRC Modem" on page 32

- FSK Modem and Packet: Section 6.4 "FSK Modem" on page 35

The long range 2.4 GHz product line also features the Ranging Engine, a long distance ranging functionality that permits time-of-flight measurement between a pair of LoRa radios. The availability of each modem and the Ranging Engine, for each part number in the long range 2.4 GHz product line is shown below.

**Table 1-1: Product Portfolio and Modem Functionality**

| Product Reference | SX1280 | SX1281 |

|-------------------|--------|--------|

| LoRa              | ✓      | ✓      |

| FLRC              | ✓      | ✓      |

| GFSK              | ✓      | ✓      |

| Ranging Engine    | ✓      |        |

# 1.4 Packet Processing

The radio can operate in a fully automatic mode where the processing of packets for transmission or reception can be performed without the intervention of an external host microcontroller. For more details see Section 7. "Packet Engine" on page 38.

In both transmit and receive modes the payload interface to the transceiver is the packet data buffer described in Section 8. "Data Buffer" on page 48 of this datasheet.

# 1.5 Digital Interface and Control

The specification and processing for all digital communication with the transceiver is described in Section 9. "Digital Interface and Control" on page 50. This includes descriptions of the SPI and UART interfaces, that can be used to configure the transceiver together with the Digital Input / Output (DIO) that are used to send interrupts to an external host microcontroller.

- For the SPI interface see Section 9.3 "SPI Interface" on page 51

- For the UART interface see Section 9.4 "UART Interface" on page 54

- For the DIO see Section 9.6 "Multi-Purpose Digital Input/Output (DIO)" on page 54

# 2. Pin Connections

# 2.1 Transceiver Pinout

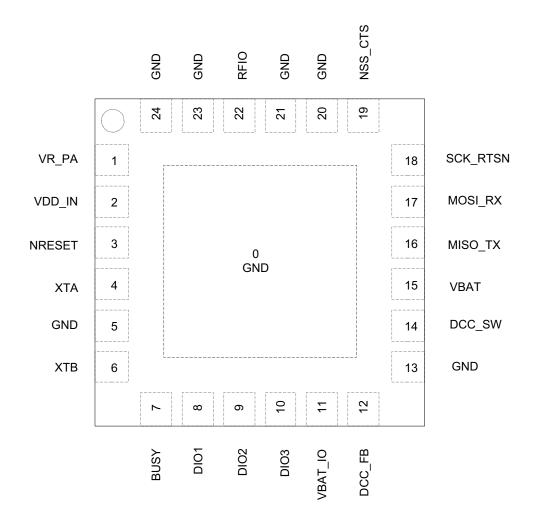

**Table 2-1: Transceiver Pinout**

| Pin<br>Number | Pin<br>Name | Type<br>(I = input<br>O = Ouptut) | SPI description                   | UART description                       |

|---------------|-------------|-----------------------------------|-----------------------------------|----------------------------------------|

| 0             | GND         | -                                 | Exposed                           | Ground pad                             |

| 1             | VR_PA       | -                                 | Regulated su                      | upply for the PA                       |

| 2             | VBAT_IN     | I                                 | Regulated supply in               | put. Connect to Pin 12.                |

| 3             | NRESET      | I                                 | Reset signal, active low w        | vith internal pull-up at 50 k $\Omega$ |

| 4             | XTA         | -                                 | Reference oscillator co           | onnection or TCXO input                |

| 5             | GND         | -                                 | Gr                                | round                                  |

| 6             | XTB         | -                                 | Reference osci                    | illator connection                     |

| 7             | BUSY        | 0                                 | Transceiver                       | busy indicator                         |

| 8             | DIO1        | I/O                               | Optional multi-                   | purpose digital I/O                    |

| 9             | DIO2        | I/O                               | Optional multi-                   | purpose digital I/O                    |

| 10            | DIO3        | I/O                               | Optional multi-                   | purpose digital I/O                    |

| 11            | VBAT_IO     | I                                 | Supply for the Digital IO interfa | ce (1.8 V to 3.7 V). Must be ≤ VBAT.   |

| 12            | DCC_FB      | 0                                 | Regulated output voltage          | e from the internal regulator          |

| 13            | GND         | -                                 | Gr                                | round                                  |

| 14            | DCC_SW      | 0                                 | DC-DC Sw                          | itcher Output                          |

| 15            | VBAT        | I                                 | Supply for the RFIC (1.8 V t      | to 3.7 V). Must be ≥ VBAT_IO.          |

| 16            | MISO_TX     | 0                                 | SPI slave output                  | UART Transmit pin                      |

| 17            | MOSI_RX     | I                                 | SPI slave input                   | UART Receive pin                       |

| 18            | SCK_RTSN    | I                                 | SPI clock                         | UART Request To Send                   |

| 19            | NSS_CTS     | I                                 | SPI Slave Select                  | UART Clear To Send                     |

| 20            | GND         | -                                 | Gr                                | round                                  |

| 21            | GND         | -                                 | Gr                                | round                                  |

| 22            | RFIO        | I/O                               | RF transmit outp                  | ut and receive input                   |

| 23            | GND         | -                                 | Gr                                | round                                  |

| 24            | GND         | -                                 | Gr                                | ound                                   |

# 2.2 Package view

**Figure 2-1: Transceiver Pin Locations**

# 3. Specifications

The following specifications are given for the typical operating conditions of VBAT\_IO = VBAT = 3.3 V, temperature = 25 °C, crystal oscillator frequency = 52 MHz, RF centre frequency = 2.4 GHz. All RF impedances are matched using the reference design, see Section 14.1 "Reference Design" on page 122. Blocking, ACR and co-channel rejection are given for a single tone interferer and referenced to sensitivity level +6 dB. The current supply is given as the sum of current on VBAT and VBAT\_IO. The buck converter (DC-DC) is considered switched ON unless otherwise stated.

#### 3.1 ESD Notice

The SX1280/SX1281 transceivers are high-performance radio frequency devices. They all satisfy:

- Class 2 of the JEDEC standard JESD22-A114 (Human Body Model) on all pins

- Class III of the JEDEC standard JESD22-C101 (Charged Device Model) on all pins

# 3.2 Absolute Minimum and Maximum Ratings

**Table 3-1: Minimum and Maximum Ratings**

| Symbol | Description                           | Minimum | Typical | Maximum | Unit |

|--------|---------------------------------------|---------|---------|---------|------|

| VBATmr | Supply voltage on<br>VBAT and VBAT_IO | -0.5    | -       | 3.9     | V    |

| Tmr    | Temperature                           | -55     | -       | 115     | °C   |

| Pmr    | RF Input level                        | -       | -       | 10      | dBm  |

## 3.3 Operating Range

**Table 3-2: Operating Range**

| Symbol | Description                        | Minimum | Typical | Maximum | Unit |

|--------|------------------------------------|---------|---------|---------|------|

| VBATop | Supply voltage<br>VBAT and VBAT_IO | 1.8     | -       | 3.7     | V    |

| Тор    | Temperature<br>under bias          | -40     | -       | 85      | °C   |

| Clop   | Load capacitance on digital ports  | -       | -       | 10      | pF   |

| ML     | RF Input power                     | -       | -       | 10      | dBm  |

# 3.4 General Electrical Specifications

**Table 3-3: General Electrical Specifications**

| Symbol       | Description                                                                                              | Minimum | Typical | Maximum | Unit   |

|--------------|----------------------------------------------------------------------------------------------------------|---------|---------|---------|--------|

|              | Supply current in Sleep mode with data buffer retained                                                   | -       | 0.215   | 1.0     | μΑ     |

| IDDSL        | Supply current in Sleep mode with register content retained (context saved) and data buffer not retained | -       | 0.25    | 1.0     | μΑ     |

| IDDSL        | Supply current in Sleep mode with instruction RAM retained                                               | -       | 0.4     | 1.0     | μΑ     |

|              | Supply current in Sleep mode with data buffer, instruction RAM, data RAM retained. RC running            | -       | 1.2     | 1.8     | μΑ     |

| IDDSTDBYRC   | Supply current in STDBY_RC mode                                                                          | -       | 760     | -       | μΑ     |

| IDDSTDBYXOSC | Supply current in STDBY_XOSC mode                                                                        | -       | 1.2     | -       | mA     |

| IDDFS        | Supply current in FS mode                                                                                | -       | 2.8     | -       | mA     |

| FR           | Synthesizer frequency range                                                                              | 2400    | -       | 2500    | MHz    |

| FSTEP        | Synthesizer frequency step<br>(52 MHz reference)                                                         | -       | 198     | -       | Hz     |

|              | Phase noise at 2.45 GHz                                                                                  |         |         |         |        |

| PHN          | 1 MHz offset                                                                                             | -       | -117    | -       | dBc/Hz |

|              | 10 MHz offset                                                                                            | -       | -133    | -       | dBc/Hz |

| FXOSC        | Crystal oscillator frequency                                                                             | -       | 52      | -       | MHz    |

| TS_FS        | Frequency synthesizer wake-up time<br>with XOSC enabled                                                  | -       | 54      | -       | μs     |

|              | Frequency synthesizer hop time to within 10 kHz of target frequency                                      |         |         |         |        |

| TS_HOP       | 1 MHz                                                                                                    | -       | 20      | -       | μs     |

| TS_HOP       | 10 MHz                                                                                                   | -       | 30      | -       | μs     |

|              | 100 MHz                                                                                                  | -       | 50      | -       | μs     |

| TS_OS        | Crystal oscillator wake-up time from STDBY_RC mode                                                       | -       | 100     | -       | μs     |

For the digital specifications, see Table 10-2: "Switching Time (TswMode) for all Possible Transitions" on page 58.

# 3.5 Receiver Electrical Specifications

All receiver sensitivity numbers are given for a Packer Error Rate (PER) of 1%, for packet with 10 bytes of payload.

Values are given for maximum AGC gain which is the highest low power gain.

A continuous wave (CW) interferer is used for all blocking and rejection measurements unless otherwise stated.

## 3.5.1 Receiver Specifications

#### **Table 3-4: Receiver Specifications**

| Symbol | Description                               | Minimum            | Typical | Maximum | Unit |

|--------|-------------------------------------------|--------------------|---------|---------|------|

|        | 3rd Order input intercept for maximum low | power gain setting |         |         |      |

|        | In-band interferer <6 MHz                 | -                  | -25     | -       | dBm  |

| IIP3   | In-band interferer @ 6 MHz                | -                  | -6      | -       | dBm  |

|        | In-band interferer @10 MHz                | -                  | -4      | -       | dBm  |

|        | In-band interferer @ 20 MHz               | -                  | -4      | -       | dBm  |

| IMR    | Image rejection (CW tone 1% PER)          | -                  | 30      | -       | dB   |

## 3.5.2 LoRa Modem

**Table 3-5: LoRa Modem Specifications**

| Symbol    | Description                                 | Minimum                | Typical             | Maximum | Unit |

|-----------|---------------------------------------------|------------------------|---------------------|---------|------|

|           | Supply current for low power mode           |                        |                     |         |      |

|           | for BW = 203 kHz                            | -                      | 5.5                 | -       | mA   |

| IDDRXLP_L | for BW = 406 kHz                            | -                      | 6.0                 | -       | mA   |

|           | for BW = 812 kHz                            | -                      | 7.0                 | -       | mA   |

|           | for BW = 1625 kHz                           | -                      | 7.5                 | -       | mA   |

|           | Supply current for high sensitivity mode    |                        |                     |         |      |

|           | for BW = 203 kHz                            | -                      | 6.2                 | -       | mA   |

| IDDRXHS_L | for BW = 406 kHz                            | -                      | 6.7                 | -       | mA   |

|           | for BW = 812 kHz                            | -                      | 7.7                 | -       | mA   |

|           | for BW = 1625 kHz                           | -                      | 8.2                 | -       | mA   |

|           | LoRa bitrate programmable range with CR     | R = 4/5                |                     |         |      |

|           | SF5, BW = 1625 kHz                          | -                      | 202                 | -       | kb/s |

| RB_L      | SF6, BW = 1625 kHz                          | -                      | 122                 | -       | kb/s |

| RB_L      | SF7, BW = 1625 kHz                          | -                      | 71                  | -       | kb/s |

|           | SF12, BW = 203 kHz                          | -                      | 0.476               | -       | kb/s |

| BW_L      | LoRa bandwidth programmable range           | 203                    | -                   | 1625    | kHz  |

|           | LoRa receiver sensitivity with CR = 4/5 and | l low power mode er    | nabled <sup>1</sup> |         |      |

| RFSLP_L   | SF7, BW = 1625 kHz,                         | -                      | -106                | -       | dBm  |

|           | SF12, BW = 203 kHz                          | -                      | -130                | -       | dBm  |

|           | LoRa receiver sensitivity with CR = 4/5 and | l high sensitivity mod | de enabled 1        |         |      |

| RFSHS_L   | SF7, BW = 1625 kHz,                         | -                      | -109                | -       | dBm  |

|           | SF12, BW = 203 kHz                          | -                      | -132                | -       | dBm  |

|           | Co-channel rejection LoRa                   |                        |                     |         |      |

| CCR_L     | SF7                                         | -                      | 7.5                 | -       | dB   |

|           | SF12                                        | -                      | 19.5                | -       | dB   |

|           | Blocking immunity SF12                      |                        |                     |         |      |

|           | +/- 1 MHz                                   | -                      | 60                  | -       | dB   |

| BI_L      | +/- 2 MHz                                   | -                      | 63                  | -       | dB   |

|           | +/- 10 MHz                                  | -                      | 81                  | -       | dB   |

**Table 3-5: LoRa Modem Specifications**

| Symbol | Description                                | Minimum | Typical | Maximum | Unit |

|--------|--------------------------------------------|---------|---------|---------|------|

|        | Adjacent channel rejection at 1.5 BW of CW |         |         |         |      |

| ACR_L  | SF = 12, BW = 203 kHz                      | -       | 37      | -       | dB   |

|        | SF = 7, BW = 1.6 MHz                       | -       | 37      | -       | dB   |

<sup>1.</sup> See Section 4.2.1 "Low Power Mode and High Sensitivity Mode" on page 26.

#### 3.5.3 FLRC Modem

**Table 3-6: FLRC Modem Specifications**

| Symbol   | Description                                    | Minimum | Typical                            | Maximum | Unit |

|----------|------------------------------------------------|---------|------------------------------------|---------|------|

|          | Supply currents                                |         |                                    |         |      |

| IDDRX_FL | BW = 300 kHz, BR = 260 kb/s                    | -       | 6.5                                | -       | mA   |

|          | BW = 1200 kHz, BR = 1300 kb/s                  | -       | 8.6                                | -       | mA   |

| RB_FL    | FLRC Modem programmable bitrate                | 260     | -                                  | 1300    | kb/s |

| BW_FL    | Programmable channel bandwidth range           | 300     | -                                  | 2400    | kHz  |

|          | FLRC Receiver Sensitivity                      |         |                                    |         |      |

| RFS_FL   | 260 kSymb/s, 130 kb/s<br>BW = 300 kHz CR=1/2   | -       | -106                               | -       | dBm  |

|          | 2.6 MSymb/s, 1.3 Mb/s,<br>BW = 2.4 MHz, CR=1/2 | -       | 6.5 -<br>8.6 -<br>- 1300<br>- 2400 | dBm     |      |

| CCR_FL   | Co-channel rejection FLRC                      | -       | -10                                | -       | dB   |

|          | Blocker level for Max low power gain setting   |         |                                    |         |      |

|          | +/- 1 MHz                                      | -       | 41                                 | -       | dB   |

| BI_FL    | +/- 2 MHz                                      | -       | 44                                 | -       | dB   |

|          | +/- 10 MHz                                     | -       | 62                                 | -       | dB   |

|          | +/- 20 MHz                                     | -       | 69                                 | -       | dB   |

|          | Adjacent channel rejection at 1.5 BW for CW    |         |                                    |         |      |

| ACR_FL   | 260 kb/s, BW = 300 kHz                         | -       | 44                                 | -       | dB   |

|          | 1.3 Mb/s, BW = 2.4 MHz                         | -       | 49                                 | -       | dB   |

Notice: all data rates listed in the table above are in raw bits. All values are given with BT = 0.5.

## 3.5.4 FSK Modem

**Table 3-7: FSK Modem Specifications**

| Symbol                               | Description                              | Minimum             | Typical                | Maximum                                              | Unit |

|--------------------------------------|------------------------------------------|---------------------|------------------------|------------------------------------------------------|------|

|                                      | Supply currents for low power mode,      | demodulation run    | ning <sup>1</sup>      |                                                      |      |

| IDDRX_FSK_250_LP                     | BW = 300 kHz, BR = 250 kb/s              | -                   | 4.8                    | -                                                    | mA   |

| IDDRX_FSK_1000_LP                    | BW = 1200 kHz, BR = 1000 kb/s            | -                   | 5.3                    | -                                                    | mA   |

| IDDRX_FSK_2000_LP                    | BW = 2400 kHz, BR = 2000 kb/s            | -                   | 5.7                    | -                                                    | mA   |

|                                      | Supply currents for high sensitivity m   | ode, demodulatior   | n running <sup>1</sup> |                                                      |      |

| IDDRX_FSK_250_HS                     | BW = 300 kHz, BR = 250 kb/s              | -                   | 5.5                    | -                                                    | mA   |

| IDDRX_FSK_1000_HS                    | BW = 1200 kHz, BR = 1000 kb/s            | -                   | 6.0                    | -                                                    | mA   |

| IDDRX_FSK_2000_HS                    | BW = 2400 kHz, BR = 2000 kb/s            | -                   | 6.4                    | -                                                    | mA   |

| BR_FSK                               | FSK Modem programmable bitrate           | 125                 | -                      | 2000                                                 | kb/s |

| BW_FSK                               | Programmable channel bandwidth range DSB | 300                 | -                      | 2400                                                 | kHz  |

|                                      | FSK Receiver Sensitivity BER 0.1%        |                     |                        |                                                      |      |

| RFS_FSK1<br>low power mode           | 250 kb/s, β = 0.5, BW = 300 kHz          | -                   | -100                   | -                                                    | dBm  |

| low power mode                       | 1 Mb/s, β = 0.5, BW = 1200 kHz           | -                   | -94                    | -<br>2000<br>2400<br>-<br>-<br>-<br>-<br>-<br>-<br>- | dBm  |

|                                      | FSK Receiver Sensitivity BER 0.1%        |                     |                        |                                                      |      |

| RFS_FSK1_HS<br>high sensitivity mode | 250 kb/s, β = 0.5, BW = 300 kHz          | -                   | -102                   | -                                                    | dBm  |

|                                      | 1 Mb/s, $\beta$ = 0.5, BW = 1200 kHz     | -                   | -96                    | - 2000<br>2400<br>z                                  | dBm  |

|                                      | FSK Receiver Sensitivity PER 1%          |                     |                        |                                                      |      |

| RFS_FSK2<br>low power mode           | 250 kb/s, β = 0.5, BW = 300 kHz          | -                   | -93                    | -                                                    | dBm  |

| ion power mode                       | 1 Mb/s, $\beta$ = 0.5, BW = 1200 kHz     | -                   | -88                    | 2000 2400                                            | dBm  |

|                                      | FSK Receiver Sensitivity PER 1%          |                     |                        | -<br>2000<br>2400<br>-<br>-<br>-<br>-<br>-<br>-<br>- |      |

| RFS_FSK2_HS high sensitivity mode    | 250 kb/s, β = 0.5, BW = 300 kHz          | -                   | -94                    | -                                                    | dBm  |

| g,                                   | 1 Mb/s, $\beta$ = 0.5, BW = 1200 kHz     | -                   | -90                    | -                                                    | dBm  |

| CCR_FSK                              | Co-Channel Rejection                     | -                   | -10                    | -                                                    | dB   |

|                                      | Blocker level for max low power gain     | setting, BR = 250 k | b/s, BW = 300 kH:      | Z                                                    |      |

|                                      | +/- 1 MHz                                | -                   | 41                     | -                                                    | dB   |

| BI_FSK                               | +/- 2 MHz                                | -                   | 44                     | -                                                    | dB   |

|                                      | +/- 10 MHz                               | -                   | 62                     | -                                                    | dB   |

|                                      | +/- 20 MHz                               | -                   | 69                     | -                                                    | dB   |

**Table 3-7: FSK Modem Specifications**

| Symbol  | Description                       | Minimum   | Typical | Maximum | Unit |

|---------|-----------------------------------|-----------|---------|---------|------|

|         | Adjacent channel rejection at 1.5 | BW for CW |         |         |      |

| ACR_FSK | BW = 300 kHz                      | -         | 34      | -       | dB   |

|         | BW = 1200 kHz                     | -         | 34      | -       | dB   |

<sup>1.</sup> See Section 4.2.1 "Low Power Mode and High Sensitivity Mode" on page 26.

Notice: all values listed in the table above are given with the modulation index  $\beta$  = 0.5.

# 3.6 Transmitter Electrical Specifications

**Table 3-8: Transmitter Electrical Specifications**

| Symbol  | Description                          | Minimum | Typical | Maximum | Unit |

|---------|--------------------------------------|---------|---------|---------|------|

| IDD_T13 | 12.5 dBm                             | -       | 24      | -       | mA   |

| IDD_T10 | 10 dBm                               | -       | 18      | -       | mA   |

| IDD_T0  | 0 dBm                                | -       | 10      | -       | mA   |

| RFOPMIN | Minimum RF output power              | -       | -18     | -       | dBm  |

| RFOPMAX | Maximum RF output power              | -       | 12.5    | -       | dBm  |

| FDA     | Programmable FSK frequency deviation | 62.5    | -       | 1000    | kHz  |

# 3.7 Crystal Oscillator Specifications

**Table 3-9: Crystal Oscillator Specifications**

| Symbol | Description                  | Minimum | Typical          | Maximum         | Unit |

|--------|------------------------------|---------|------------------|-----------------|------|

| FXOSC  | Crystal oscillator frequency | -       | 52               | -               | MHz  |

| CLOAD  | Crystal loading capacitance  | -       | 10               | -               | рF   |

| COXTAL | Crystal shunt capacitance    | -       | 2                | 5               | рF   |

| RSXTAL | Crystal series resistance    | -       | 10               | 50 <sup>1</sup> | Ω    |

| CMXTAL | Crystal motional capacitance | 3       | 3.5 <sup>2</sup> | 4               | fF   |

<sup>1.</sup> An RSXTAL of up to 90  $\Omega$  may be used if C0XTAL is restricted to < 3 pF.

<sup>2.</sup> Other CMXTAL values may be used, noting that smaller values reduce start up time whilst larger values will degrade frequency accuracy and phase noise.

# 3.8 Digital Pin Levels

**Table 3-10: Digital Levels and Timings**

| Symbol            | Description                                       | Minimum | Typical | Maximum | Unit    | Conditions                        |

|-------------------|---------------------------------------------------|---------|---------|---------|---------|-----------------------------------|

| V <sub>IH</sub>   | Digital input level high                          | 0.8     | -       | -       | VBAT_IO | -                                 |

| V <sub>IL</sub>   | Digital input level low                           | -       | -       | 0.2     | VBAT_IO | -                                 |

| V <sub>OH</sub>   | Digital output level high                         | 0.9     | -       | -       | VBAT_IO | $I_{\text{max}} = 2.5 \text{ mA}$ |

| V <sub>OL</sub>   | Digital output level low                          | -       | -       | 0.1     | VBAT_IO | I <sub>max</sub> = -2.5 mA        |

| I <sub>Leak</sub> | Digital input leakage current<br>(NSS, MOSI, SCK) | -1      | -       | 1       | μΑ      | -                                 |

Rev 1.1

# 4. Analog Front End

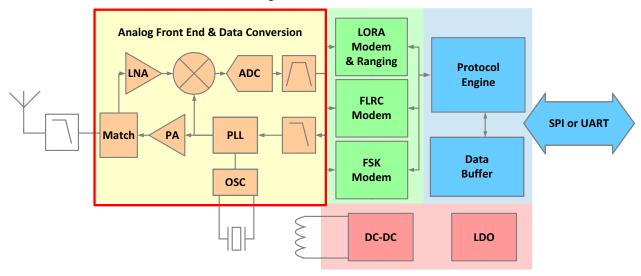

The analog front end features a single antenna port connection to an integrated matching circuit that permits half-duplex operation of the radio without external RF switching.

Figure 4-1: Transceiver Block Diagram, Analog Front End Highlighted

### 4.1 Transmitter

The transmit chain comprises the modulated output from the modem bank which directly modulates the fractional-N PLL. An optional pre-filtering of the bit stream can be enabled to reduce the power in the adjacent channels, also dependent upon the selected modulation type.

The transmitter is enabled by using the SetTx(periodBase, periodBaseCount) command. Upon issuing this command, the transmitter sends the packet stored in the data buffer. The transmitter then returns to STDBY\_RC mode, either upon completion of the packet transmission, or after a predefined time-out period defined by the time base of the interrupt timer, periodBase, and the preset number of clock ticks periodBaseCount as in Section 12. "List of Commands" on page 83.

The RF output power of the transmitter is controllable in 1 dB increments in the range -18 dBm to +12 dBm, the final power step is then a 0.5 dB increment to the maximum transmitter output power of 12.5 dBm. The RF output power (PRF) and the ramp time are determined by the command SetTxParam(power, rampTime). The output power is set using the formula:

$$P_{RF[dBm]} = -18 + power$$

Where the maximum output power, P<sub>RF[dBm]</sub>, is 12.5 dBm.

This corresponds to the RF output power at the antenna feedpoint of the reference design (see Section 14.1.1 "Application Design Schematic" on page 122). Abrupt switching of an RF power amplifier can cause undesirable spurious spectral emissions. A precision DAC is therefore used as a reference for the transceiver PA supply allowing smooth transition to transmit mode. The time over which the PA is ramped, prior to packet transmission, *rampTime* can be varied from 2 to 20 µs accordingly. In some applications and for regulatory testing purposes it can be useful to generate a continuous wave (CW) tone in transmit mode or enable a continuously modulated output. These two functionalities are accessible through

the SetTxContinuousWave() and SetTxContinuousPreamble() functions. The latter provides a stream of alternating logical '1' and '0' modulated data using whatever configured modulation settings.

### 4.2 Receiver

LoRa, FLRC or FSK systems operate as a half-duplex low-IF/zero-IF transceiver. The received RF signal is first amplified by the LNA via the on-chip impedance matching network. The single-ended to differential conversion is performed afterwards to improve the second order linearity of the receiver. The signal is then down-converted to baseband or an intermediate frequency by quadrature mixers to obtain the I and Q signals. These signals are then low-pass filtered and finally digitized.

The receive chain employs an Automatic Gain Control (AGC) that is enabled by default and is used to ensure that the optimal front end gain is selected for reception of a given detected signal power. This can be disabled and the gain of the RF front end set manually. To do this the following registers must be configured:

**Table 4-1: Procedure for Receiver Gain Manual Setting**

| Register | Bit     | Value   | Comments                                  |

|----------|---------|---------|-------------------------------------------|

| 0x89F    | bit 7   | 1       | Enable Manual Gain Control                |

| 0x895    | bit 0   | 0       | Enable Manual Gain Control                |

| 0x89E    | bit 0:3 | 1 to 13 | Manual Gain Setting (see following table) |

The gain can then be set according to the settings indicated in the table below:

**Table 4-2: Receiver Gain Manual Setting**

| Setting | Gain [dB] |

|---------|-----------|

| 13      | Max       |

| 12      | Max -2    |

| 11      | Max -4    |

| 10      | Max -6    |

| 9       | Max -8    |

| 8       | Max -12   |

| 7       | Max -18   |

| 6       | Max -24   |

| 5       | Max -30   |

| 4       | Max -36   |

| 3       | Max -42   |

| 2       | Max -48   |

| 1       | Max -54   |

The procedure for reading from and writing to a control register is described in Section 12. "List of Commands" on page 83.

The transition to receive mode is made by issuing the SetRx(periodBase, periodBaseCount) command with the periodBase oscillator timebase and periodBaseCount number of clock ticks specifying the time-out upon which receive mode (see Section 10.5 "Receive (Rx) Mode" on page 56) will be exited to STDBY\_RC mode. The process of periodic reception can be fully automated in the transceiver. This process and the processing specific to each modulation format are described in Section 13.1.3 "Rx Setting and Operations" on page 92.

When a signal or packet is received the transceiver reports a signal strength using the Received Signal Strength Indicator (RSSI). This information is returned with a *GetPacketStatus()* request as in Section 12. "List of Commands" on page 83.

#### 4.2.1 Low Power Mode and High Sensitivity Mode

In receive mode, the SX1280 can operate in one of two distinct regimes of operation. Low power mode allows maximium efficiency of the SX1280 to be attained, optimizing the performance of the device for receiver current consumption. This is enabled by default and limits the gain of the receiver LNA from accessing the highest three steps of LNA gain.

Conversely, high sensitivity mode can be used to unlock the very lowest noise, highest sensitivity gain steps for a slight increase in receiver current consumption. High sensitivity mode is enabled by setting bits 7:6 at address 0x891 to 0x3. Once enabled the noise figure of the receiver is improved by up to 3 dB for 500  $\mu$ A of additional current consumption.

#### **4.3 PLL**

A fractional-N third order sigma-delta PLL acts as the frequency synthesizer for the LO (Local Oscillator) for both receiver and transmitter chains. The PLL is capable of fast auto-calibration with a low switching time. Modulation is performed automatically either within or outside the PLL bandwidth depending upon the selected modulation type.

The PLL frequency is derived from the crystal oscillator circuit which uses an external 52 MHz crystal reference. The PLL and reference frequency determine the RF centre frequency of the radio. With the default crystal reference frequency, FXosc, and FRF values this is set to 2.4 GHz. All other reference oscillator and PLL settings are automatically optimized for the selected modem settings.

To set the RF centre frequency of transceiver the SetRFFrequency() command is used. The frequency is passed as a 24-bit operand, rfFrequency, as shown below:

$$F_{RF} = \frac{FXosc}{2^{18}} rfFrequency$$

The PLL can be enabled individually by using the SetFS() command, which tunes the PLL to the transmit frequency. This is an intermediate mode that is automatically enabled on the transition from sleep or standby to transmit or receive modes.

### 4.4 RC Oscillators

Two RC oscillators are available: 64 kHz and 13 MHz RC oscillators. The 64 kHz RC oscillator is optionally used by the transceiver in Sleep mode to wake the transceiver to perform periodic or duty cycled operations. The 13 MHz RC oscillator is enabled for all SPI or UART communication to permit configuration of the device without starting the crystal oscillator.

The presence of the two oscillators allows ultra low consumption in Sleep mode with only the 64 kHz oscillator running, whereas once communication is initiated, the faster higher consumption 1.3 MHz oscillator is started to allow efficient high-speed communication with an external host processor. Optionally the crystal oscillator can be used instead of the RC oscillator in all modes other than sleep mode, as described in Section 10. "Operational Modes" on page 55.

SX1280/SX1281

Data Sheet Rev 1.1

DS.SX1280-1.W.APP May 2017

### 5. Power Distribution

Figure 5-1: Transceiver Block Diagram, Power Distribution Highlighted

# 5.1 Selecting DC-DC Converter or LDO Regulation

Two forms of voltage regulation (DC-DC buck converter or linear regulator) are available depending upon the design priorities of the application. By default the linear LDO regulator is used in all modes. Alternatively a high efficiency DC to DC buck converter (DC-DC) can be enabled in FS, Rx and Tx modes.

All specifications of the transceiver are given with the DC-DC regulator enabled. For applications where cost and size are constrained, LDO-only operation is possible which negates the need for the 15  $\mu$ H inductor between pins 12 and 14, conferring the following benefits:

- Reduced Bill Of Materials

- Reduced board space

Conversely, the energy consumption of the radio will be increased. The following table illustrates the power regulation options for different modes and user settings.

**Table 5-1: Regulation Type versus Circuit Mode**

| Circuit Mode       | Sleep | STDBY_RC | STDBY_XOSC | FS    | Rx    | Tx    |

|--------------------|-------|----------|------------|-------|-------|-------|

| Regulator Type = 0 | -     | LDO      | LDO        | LDO   | LDO   | LDO   |

| Regulator Type = 1 | -     | LDO      | DC-DC      | DC-DC | DC-DC | DC-DC |

The user can specify the use of DC-DC by using the command <code>SetRegulatorType(regulatorType)</code>. This operation must be carried out in <code>STDBY\_RC</code> mode only.

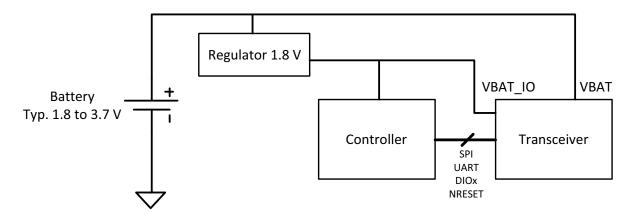

# **5.2 Flexible DIO Supply**

The transceiver has two power supply pins, one for the core of the transceiver called VBAT and one for the host controller interface (SPI/UART, DIOs, BUSY) called VBAT\_IO. Both power supplies can be connected together in application. In case a low voltage micro-controller (typically with IO pads at 1.8 V) is used to control the transceiver, the user can:

- use VBAT at 3.3V for optimal RF performance

- directly connect VBAT\_IO to the same supply used for the micro-controller

- connect the digital IOs including SPI or UART directly to the micro-controller DIOs.

At any time, VBAT\_SX1280\_DIO must be lower than or equal to VBAT.

Requirement: VBAT ≥ VBAT\_IO

Figure 5-2: Separate DIO Supply

# 6. Digital Baseband

### 6.1 Overview

The transceiver features three modems that are all implemented in the digital baseband portion of the circuit. Corresponding to each modem are independent packet format and packet configuration options.

All modems use a digital Automatic Frequency Correction (AFC). This process is fully automated and transparent to the user. The frequency tolerance of each modem is detailed in its corresponding Section. The interfaces controlling the modem configuration and the memory in which the packets are stored are also common to all modems providing a simple unified interface to both the modulated and demodulated data.

The available modems and the corresponding packet types for each modem are shown in the highlighted block below:

Figure 6-1: Transceiver Block Diagram, Modems Highlighted

Associated with each physical layer modulation available, there is also a range of corresponding packet formats.

Note: care must therefore be taken to ensure that modulation parameters are set using the command SetModulationParam() only after defining the packet type SetPacketType() to be used.

### 6.2 LoRa Modem

The LoRa modem provides both long range communication based upon LoRa spread spectrum modulation and incorporates a ranging engine which provides the facility to measure the time-of-flight, thus offering the possibility to deduce the range between a pair of transceivers.

#### 6.2.1 LoRa Modulation

The LoRa modem uses spread spectrum modulation and Forward Error Correction (FEC) techniques to increase the range and robustness of radio communication links compared to traditional FSK or OOK based modulations.

An important aspect of the LoRa modem is its superior immunity to interference. It is capable of co-channel rejection up to 19.5 dB. This immunity to interference allows the coexistence of LoRa modulated systems either in bands of heavy spectral usage or in hybrid communication networks that use LoRa to extend range and robustness when legacy modulation schemes fail.

When used for communication the LoRa packet is compatible with this modem. Full details on this format and its use can be found in Section 13.4 "LoRa Packet" on page 111.

### **6.2.2 Spreading Factor**

The LoRa modem uses a chirp spread spectrum based modulation. As for any spread spectrum device, the LoRa modulation represents each symbol of payload information by multiple chips of information. The Spreading Factor (SF) determines the ratio between the symbol rate (Rs) and chip rate (Rc):

$$R_c = 2^{SF} R_s$$

Note that the Spreading Factor must be known in advance on both transmit and receive sides of the link as different spreading factors are orthogonal to each other.

The following table shows the receiver sensivities when using the LoRa modem. The receiver sensitivities are given with:

- Packer Error Rate (PER) of 1%,

- · Packet with 10 bytes of payload

- 25°C, 3.3. V, CR = 4/5

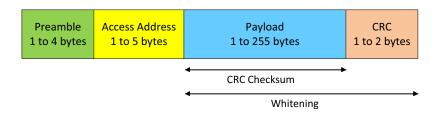

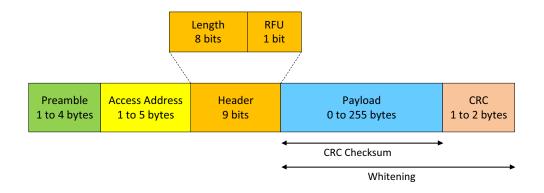

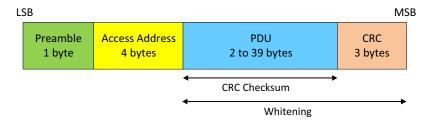

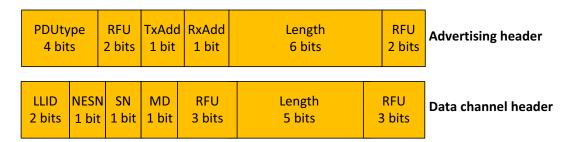

Table 6-1: Receiver Sensitivity when using LoRa