www.ti.com.cn

ZHCSB94-JULY 2013

# 具有 IEC-ESD 保护的总线极性纠正 RS-485 转发器

## 特性

- 超过 EIA-485 标准的要求

- 76ms (t<sub>FS</sub>)内的总线极性纠正

- 数据速率: 300bps 至 250kbps

- 两个工作配置:

- 只作为故障安全电阻器

- 故障安全和差分端接电阻器

- 在一个总线上多达 256 个节点(1/8 单位负载)

- 小外形尺寸集成电路 (SOIC)-8 封装以实现向后兼 容性

- 总线引脚保护:

- ±16kV 的人体模型 (HBM) 保护

- ±12kV IEC61000-4-2 接触放电

- +4kV IEC61000-4-4 快速瞬态突发

## 应用范围

- 电子

- 工业自动化

- 加热,通风和空调环境系统 (HVAC)

- DMX512 网络

- 过程控制

- 电池供电型应用

- 运动控制

- 电信设备

## 说明

SN65HVD888 是一款低功率 RS-485 转发器,此转发 器具有自动总线极性纠正和瞬态保护。热插拔时,此 器件在总线闲置的头 76ms 内检测并纠正总线极性。 片载瞬态保护功能保护此器件不受 IEC61000 静电放 电 (ESD) 和瞬态放电 (EFT) 瞬态的影响。 这个器件有 针对要求严格的工业类应用的稳健耐用的驱动器和发送 器。 这些总线引脚可耐受静电放电 (ESD) 事件,具有 对于人体模型 (HBM),空气间隙放电和接触放电技术 规范的高水平保护。

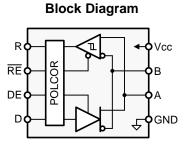

此器件将一个差分驱动器和一个差分接收器组合在一起,这两个器件由一个 5V 单电源供电。驱动器差分输出和接收器差分输入被内部连接以形成一个适用于半双工(两线制总线)通信的总线端口。此器件都特有一个宽共模电压范围,这使得此器件适合于长线缆运行上的多点应用。SN65HVD888 采用一个 SOIC-8 封装,并且在 -40℃ 至 85℃ 范围内运行。

53

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### ZHCSB94-JULY 2013

Texas Instruments

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

| SOIC-8<br>(TOP VIEW) |   |   |   |     |  |  |  |  |  |

|----------------------|---|---|---|-----|--|--|--|--|--|

| R 🛙                  |   | 8 | Ь | Vcc |  |  |  |  |  |

| RE [                 | 2 | 7 | Ш | В   |  |  |  |  |  |

| DE [                 | 3 | 6 |   | Α   |  |  |  |  |  |

| D [[                 | 4 | 5 |   | GND |  |  |  |  |  |

#### DRIVER PIN FUNCTIONS

| INPUT       | ENABLE | OUT | PUTS | DESCRIPTION                             |  |  |

|-------------|--------|-----|------|-----------------------------------------|--|--|

| D           | DE     | Α   | В    | DESCRIPTION                             |  |  |

| NORMAL MODE |        |     |      |                                         |  |  |

| Н           | Н      | Н   | L    | Actively drives bus High                |  |  |

| L           | Н      | L   | Н    | Actively drives bus Low                 |  |  |

| Х           | L      | Z   | Z    | Driver disabled                         |  |  |

| Х           | OPEN   | Z   | Z    | Driver disabled by default              |  |  |

| OPEN        | Н      | Н   | L    | Actively drives bus High                |  |  |

|             |        |     |      | POLARITY-CORRECTING MODE <sup>(1)</sup> |  |  |

| Н           | Н      | L   | Н    | Actively drives bus Low                 |  |  |

| L           | Н      | Н   | L    | Actively drives bus High                |  |  |

| Х           | L      | Z   | Z    | Driver disabled                         |  |  |

| Х           | OPEN   | Z   | Z    | Driver disabled by default              |  |  |

| OPEN        | Н      | L   | Н    | Actively drives bus Low                 |  |  |

(1) The polarity-correcting mode is entered when  $V_{ID} < V_{IT-}$  and  $t > t_{FS}$  and DE = low. This state is latched when /RE turns from Low to High.

#### **RECEIVER PIN FUNCTIONS**

| DIFFERENTIAL<br>INPUT        | ENABLE | OUTPUT | DESCRIPTION                          |  |

|------------------------------|--------|--------|--------------------------------------|--|

| $V_{ID} = V_A - V_B$         | /RE    | R      |                                      |  |

|                              |        |        | NORMAL MODE                          |  |

| $V_{IT+} < V_{ID}$           | L      | Н      | Receive valid bus High               |  |

| $V_{IT-} < V_{ID} < V_{IT+}$ | L      | ?      | Indeterminate bus state              |  |

| $V_{ID} < V_{IT-}$           | L      | L      | Receive valid bus Low                |  |

| Х                            | Н      | Z      | Receiver disabled                    |  |

| Х                            | OPEN   | Z      | Receiver disabled                    |  |

| Open, short, idle Bus        | L      | ?      | Indeterminate bus state              |  |

|                              |        | POL    | ARITY-CORRECTING MODE <sup>(1)</sup> |  |

| $V_{IT+} < V_{ID}$           | L      | L      | Receive valid bus Low                |  |

| $V_{IT-} < V_{ID} < V_{IT+}$ | L      | ?      | Indeterminate bus state              |  |

| $V_{ID} < V_{IT-}$           | L      | Н      | Receive polarity corrected bus High  |  |

| Х                            | Н      | Z      | Receiver disabled                    |  |

| Х                            | OPEN   | Z      | Receiver disabled                    |  |

| Open, short, idle Bus        | L      | ?      | Indeterminate bus state              |  |

(1) The polarity-correcting mode is entered when  $V_{ID} < V_{IT-}$  and t > t<sub>FS</sub> and DE = low. This state is latched when /RE turns from Low to High.

ZHCSB94-JULY 2013

## **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

|                  |                                    |                                                   | VALUE |                         | UNIT |

|------------------|------------------------------------|---------------------------------------------------|-------|-------------------------|------|

|                  |                                    |                                                   | MIN   | MAX                     |      |

| V <sub>CC</sub>  | Supply voltage                     |                                                   | -0.5  | 7                       |      |

|                  | Input voltage range at any         | logic pin                                         | -0.3  | 5.7                     |      |

|                  | Voltage input range, transie       | ent pulse, A and B, through 100 $\Omega$          | -100  | 100                     | V    |

|                  | Voltage range at A or B inp        | outs                                              | -18   | 18                      |      |

|                  | Receiver output current            |                                                   | -24   | 24                      | mA   |

|                  | Continuous total-power dissipation |                                                   |       | See THERMAL INFORMATION |      |

|                  | IEC 61000-4-2 ESD (Conta           |                                                   | ±12   |                         |      |

|                  | IEC 61000-4-4 EFT (Fast t          | ransient or burst) bus terminals and GND          |       | ±4                      |      |

|                  | IEC 60749-26 ESD (HBM),            | bus terminals and GND                             |       | ±16                     | kV   |

|                  |                                    | Test Method A114 (HBM), all pins                  |       | ±4                      |      |

|                  | JEDEC Standard 22                  | Test Method C101 (Charged Device Model), all pins |       | ±1.5                    |      |

|                  |                                    |                                                   | ±100  | V                       |      |

| TJ               | Junction temperature               |                                                   | 170   | *                       |      |

| T <sub>STG</sub> | Storage temperature                |                                                   | -65   | 150                     | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## THERMAL INFORMATION

|                    |                                                     | SN65HVD888          |       |

|--------------------|-----------------------------------------------------|---------------------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                       | PACKAGE SOIC<br>(D) | UNITS |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance              | 116.1               |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance           | 60.8                |       |

| $\theta_{JB}$      | Junction-to-board thermal resistance <sup>(2)</sup> | 57.1                |       |

| $\Psi_{JT}$        | Junction-to-top characterization parameter          | 13.9                | °C/W  |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter        | 56.5                |       |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance        | NA                  |       |

For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

## POWER DISSIPATION

|                   | PARAMETER                                                                                                                                                                                                                 | TEST CONDITIONS                                                                      | VALUE                                                                                | UNITS |    |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|----|

| Power Dissipation | Unterminated                                                                                                                                                                                                              | $ \begin{array}{l} R_{L} = 300 \ \Omega, \\ C_{L} = 50 \ pF \ (driver) \end{array} $ | 164                                                                                  | mW    |    |

| PD                | $\begin{array}{l} \mbox{driver and receiver enabled,} \\ \mbox{PD} & V_{CC} = 5.5 \mbox{ V, } T_J = 150^{\circ}\mbox{C} \\ 50\% \mbox{ duty cycle square-wave signal at} \\ 250 \mbox{ kbps signaling rate:} \end{array}$ | RS-422 load                                                                          | $ \begin{array}{l} R_{L} = 100 \ \Omega, \\ C_{L} = 50 \ pF \ (driver) \end{array} $ | 247   | mW |

|                   |                                                                                                                                                                                                                           | RS-485 load                                                                          | $ \begin{array}{l} R_L = 54 \ \Omega, \\ C_L = 50 \ pF \ (driver), \end{array} $     | 316   | mW |

EXAS

www.ti.com.cn

## **RECOMMENDED OPERATING CONDITIONS**

|                               |                                                  |                                                                        | MIN | NOM | MAX             | UNIT |

|-------------------------------|--------------------------------------------------|------------------------------------------------------------------------|-----|-----|-----------------|------|

| V <sub>CC</sub>               | Supply voltage                                   |                                                                        | 4.5 | 5   | 5.5             |      |

| $V_{ID}$                      | Differential input voltage                       |                                                                        | -12 |     | 12              |      |

| VI                            | Input voltage at any bus terminal (se            | eparate or common mode) <sup>(1)</sup>                                 | -7  |     | 12              | V    |

| $V_{\text{IH}}$               | High-level input voltage (driver, drive          | er-enable, and receiver-enable inputs)                                 | 2   |     | V <sub>CC</sub> |      |

| VIL                           | Low-level input voltage (driver, drive           | 0                                                                      |     | 0.8 |                 |      |

|                               | Output ourroat                                   | Driver                                                                 | -60 |     | 60              |      |

| I <sub>O</sub>                | Output current                                   | Receiver                                                               | -8  |     | 8               | mA   |

| CL                            | Differential load capacitance                    |                                                                        |     | 50  |                 | pF   |

| RL                            | Differential load resistance                     |                                                                        |     | 60  |                 | Ω    |

| 1/t <sub>UI</sub>             | Signaling rate                                   | 0.3                                                                    |     | 250 | kbps            |      |

| TJ                            | Junction temperature                             | -40                                                                    |     | 150 |                 |      |

| T <sub>A</sub> <sup>(2)</sup> | Operating free-air temperature (see information) | Operating free-air temperature (see THERMAL INFORMATION for additional |     |     | 85              | °C   |

The algebraic convention in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

Operation is specified for internal (junction) temperatures up to 150°C. Self-heating due to internal power dissipation should be considered for each application. Maximum junction temperature is internally limited by the thermal shut-down (TSD) circuit which disables the driver outputs when the junction temperature reaches 170°C.

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                                                      | TEST COND                                          | MIN          | TYP  | MAX                      | UNIT |    |

|---------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|--------------|------|--------------------------|------|----|

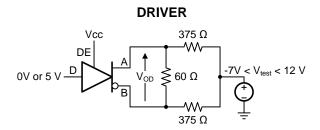

| 1.7 1                           | Driver differential-output                                                     | RL = 60 Ω, 375 Ω on each output from $-7$ to +12 V | See Figure 1 | 1.5  | 2.5                      |      |    |

| V <sub>OD</sub>                 | voltage magnitude                                                              | RL = 54 Ω (RS-485)                                 | See Figure 2 | 1.5  | 2.5                      |      | V  |

|                                 |                                                                                | RL = 100 Ω (RS-422)                                | See Figure 2 | 2    | 3                        |      |    |

| $\Delta  V_{OD} $               | Change in magnitude of<br>driver differential-output<br>voltage                | RL = 54 Ω, CL = 50 pF                              | See Figure 2 | -0.2 | 0                        | 0.2  | V  |

| V <sub>OC(SS)</sub>             | Steady-state common-mode output voltage                                        |                                                    |              | 1    | V <sub>CC</sub> / 2      | 3    | V  |

| ΔV <sub>OC</sub>                | Change in differential driver common-mode output voltage                       | Center of two 27-Ω load resistors                  | See Figure 2 | -0.2 | 0                        | 0.2  |    |

| V <sub>OC(PP)</sub>             | Peak-to-peak driver common-<br>mode output voltage                             |                                                    |              |      | 850                      |      | mV |

| C <sub>OD</sub>                 | Differential output capacitance                                                |                                                    |              |      | 8                        |      | pF |

| V <sub>IT+</sub>                | Positive-going receiver<br>differential-input voltage<br>threshold             |                                                    |              |      | 35                       | 100  | mV |

| V <sub>IT-</sub>                | Negative-going receiver<br>differential-input voltage<br>threshold             |                                                    |              | -100 | -35                      |      | mV |

| V <sub>HYS</sub> <sup>(1)</sup> | Receiver differential-input voltage threshold hysteresis $(V_{IT+} - V_{IT-})$ |                                                    |              | 40   | 60                       |      | mV |

| V <sub>OH</sub>                 | Receiver high-level output voltage                                             | I <sub>OH</sub> = -8 mA                            |              | 2.4  | V <sub>CC</sub> –<br>0.3 |      | V  |

| V <sub>OL</sub>                 | Receiver low-level output voltage                                              | I <sub>OL</sub> = 8 mA                             |              |      | 0.2                      | 0.4  | V  |

| I <sub>I</sub>                  | Driver input, driver enable,<br>and receiver enable input<br>current           |                                                    |              | -2   |                          | 2    | μA |

(1) Under any specific conditions,  $V_{IT+}$  is ensured to be at least  $V_{HYS}$  higher than  $V_{IT-}$ .

www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                                        | TEST CONDI                                                        | TEST CONDITIONS                                               |       | TYP | MAX | UNIT |  |

|-----------------|----------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|-------|-----|-----|------|--|

| I <sub>OZ</sub> | Receiver high-impedance output current | VO = 0 V or VCC, /RE at VCC                                       | )                                                             | -10   |     | 10  | μA   |  |

| I <sub>OS</sub> | Driver short-circuit output current    | $ I_{OS} $ with V <sub>A</sub> or V <sub>B</sub> from –7 to +12 V |                                                               |       |     | 150 | mA   |  |

|                 | Bus input current (driver              | $V_{CC} = 4.5$ to 5.5 V or                                        | V <sub>I</sub> = 12 V                                         |       | 75  | 125 |      |  |

| disabled)       | $V_{CC}$ = 0 V, DE at 0 V              | $V_I = -7 V$                                                      | -100                                                          | -40   |     | μA  |      |  |

|                 |                                        | Driver and receiver enabled                                       | DE = V <sub>CC</sub> , /RE =<br>GND, No load                  |       | 750 | 900 |      |  |

|                 |                                        | Driver enabled, receiver disabled                                 | $\begin{array}{l} DE=V_{CC},/RE=\\ V_{CC},Noload \end{array}$ |       |     | 650 |      |  |

| I <sub>CC</sub> | Supply current (quiescent)             | Driver disabled, receiver enabled                                 | DE = GND, /RE =<br>GND, No load                               |       |     | 750 | μA   |  |

|                 |                                        | Driver and receiver disabled                                      | DE = GND, D =<br>GND /RE = VCC,<br>No load                    | 0.4 5 |     | 5   |      |  |

|                 | Supply current (dynamic)               | See                                                               |                                                               |       |     |     |      |  |

## SWITCHING CHARACTERISTICS

3.3 ms > bit time > 4  $\mu$ s (unless otherwise noted)

| PARAMETER                                                           |                                                           | TEST CONDITIONS    |                              | MIN | TYP | MAX  | UNIT |  |

|---------------------------------------------------------------------|-----------------------------------------------------------|--------------------|------------------------------|-----|-----|------|------|--|

| DRIVER                                                              |                                                           |                    |                              |     |     |      |      |  |

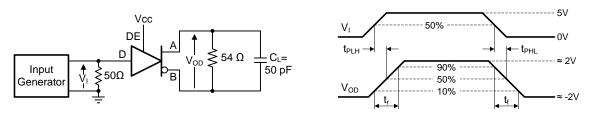

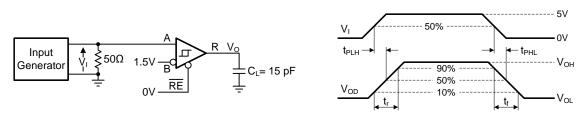

| t <sub>r</sub> , t <sub>f</sub>                                     | Driver differential-output rise and fall times            | RL = 54 Ω, CL = 50 |                              | 400 | 700 | 1200 |      |  |

| t <sub>PHL</sub> , t <sub>PLH</sub>                                 | Driver propagation delay                                  | pF                 | See Figure 3                 | 90  | 700 | 1000 | ns   |  |

| t <sub>SK(P)</sub>                                                  | Driver pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub>   |                    |                              |     | 25  | 200  |      |  |

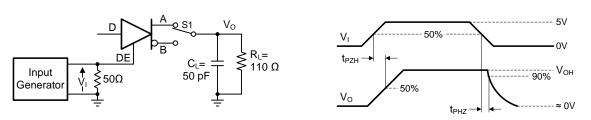

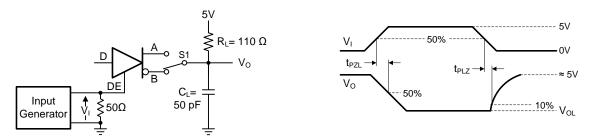

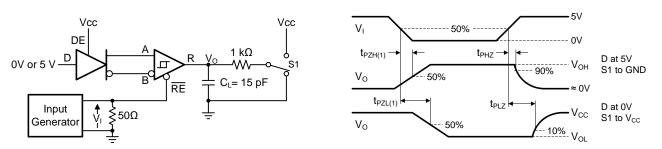

| t <sub>PHZ</sub> , t <sub>PLZ</sub>                                 | Driver disable time                                       |                    |                              |     | 50  | 500  |      |  |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>                                 | Driver enable time                                        | Receiver enabled   | See Figure 4 and<br>Figure 5 |     | 500 | 1000 | ns   |  |

|                                                                     |                                                           | Receiver disabled  |                              |     | 3   | 9    | μs   |  |

| RECEIVE                                                             | R                                                         |                    |                              |     |     |      |      |  |

| t <sub>r</sub> , t <sub>f</sub>                                     | Receiver output rise and fall times                       |                    |                              |     | 18  | 30   |      |  |

| t <sub>PHL</sub> , t <sub>PLH</sub>                                 | Receiver propagation delay time                           | CL = 15 pF         | See Figure 6                 |     | 85  | 195  | ns   |  |

| t <sub>SK(P)</sub>                                                  | Receiver pulse skew,  t <sub>PHL</sub> - t <sub>PLH</sub> |                    |                              |     | 1   | 15   |      |  |

| t <sub>PHZ</sub> , t <sub>PLZ</sub>                                 | Receiver disable time                                     |                    |                              |     | 50  | 500  |      |  |

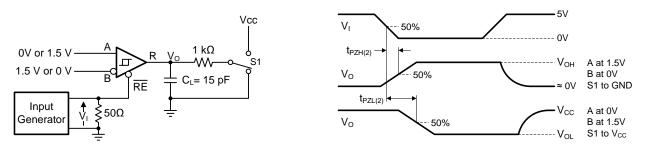

| t <sub>PZL(1)</sub> ,                                               |                                                           | Driver enabled     | See Figure 7                 |     | 20  | 130  | ns   |  |

| t <sub>PZH(1)</sub><br>t <sub>PZL(2)</sub> ,<br>t <sub>PZH(2)</sub> | Receiver enable time                                      | Driver disabled    | See Figure 8                 |     | 2   | 8    | μs   |  |

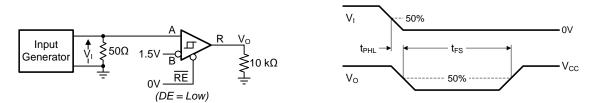

| t <sub>FS</sub>                                                     | Bus failsafe time                                         | Driver disabled    | See Figure 9                 | 44  | 58  | 76   | ms   |  |

# ▼ INSTRUMENTS

#### www.ti.com.cn

XAS

#### PARAMETER MEASUREMENT INFORMATION

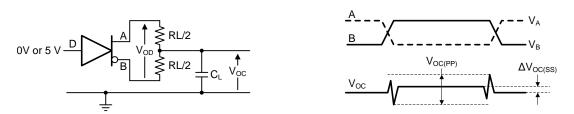

Figure 1. Measurement of Driver Differential-Output Voltage With Common-Mode Load

Figure 2. Measurement of Driver Differential and Common-Mode Output With RS-485 Load

Figure 3. Measurement of Driver Differential-Output Rise and Fall Times and Propagation Delays

Figure 4. Measurement of Driver Enable and Disable Times With Active-High Output and Pull-Down Load

Figure 5. Measurement of Driver Enable and Disable Times With Active-Low Output and Pull-up Load

## **SN65HVD888**

ZHCSB94-JULY 2013

# PARAMETER MEASUREMENT INFORMATION (continued)

RECEIVER

Figure 6. Measurement of Receiver Output Rise and Fall Times and Propagation Delays

Figure 7. Measurement of Receiver Enable and Disable Times With Driver Enabled

Figure 8. Measurement of Receiver Enable Times With Driver Disabled

Figure 9. Measurement of Receiver Polarity-Correction Time With Driver Disabled

ZHCSB94-JULY 2013

www.ti.com.cn

INSTRUMENTS

Texas

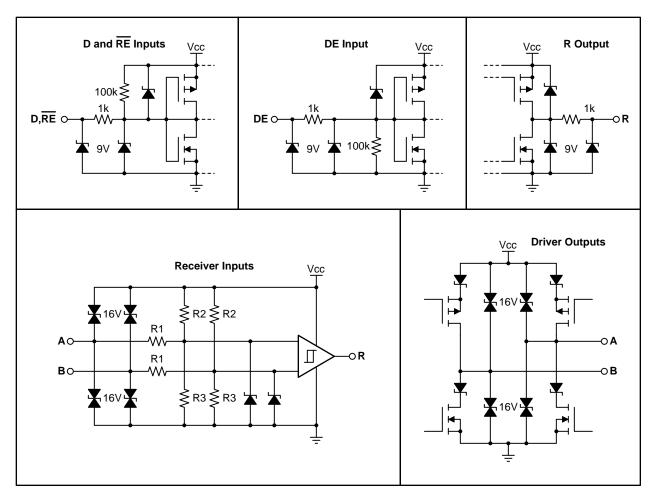

## EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

Figure 10. Equivalent Input and Output Schematic Diagrams

## **DEVICE INFORMATION**

#### Low-Power Standby Mode

When the driver and the receiver are both disabled (DE = Low and RE = High) the device enters standby mode. If the enable inputs are in the disabled state for only a brief time (for example: less than 100 ns), the device does not enter standby mode, preventing the SN65HVD888 from entering standby mode during driver or receiver enabling. Only when the enable inputs are held in the disabled state for a duration of 300 ns or more does the device enter low-power standby mode. In this mode most internal circuitry is powered down, and the steady-state supply current is typically less than 400 nA. When either the driver or the receiver is re-enabled, the internal circuitry becomes active. During  $V_{CC}$  power-up, when the device is set for both driver and receiver disabled mode, the device may consume more than 5-µA of ICC disabled current because of capacitance charging effects. This condition occurs only during  $V_{CC}$  power up.

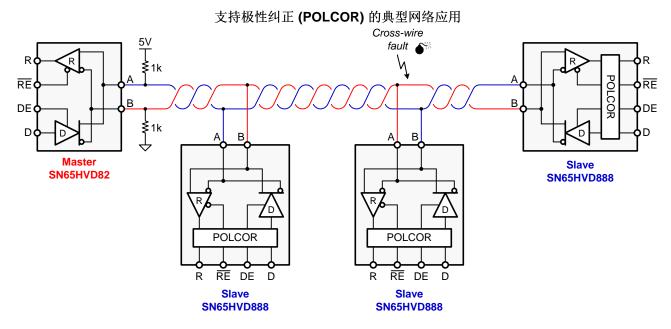

## **Bus Polarity Correction**

The SN65HVD888 automatically corrects a wrong bus-signal polarity caused by a cross-wire fault. In order to detect the bus polarity, all three of the following conditions must be met:

- A failsafe-biasing network (commonly at the master node) must define the signal polarity of the bus

- A slave node must enable the receiver and disable the driver (/RE = DE = Low)

- The bus must idle for the failsafe time, t<sub>FS-max</sub>

After the failsafe time has passed, the polarity correction is complete and is applied to both the receive and transmit channels. The status of the bus polarity is latched within the transceiver and is maintained for subsequent data transmissions.

#### NOTE

Data string durations of consecutive 0s or 1s exceeding  $t_{FS-min}$  can accidently trigger a wrong polarity correction and must be avoided.

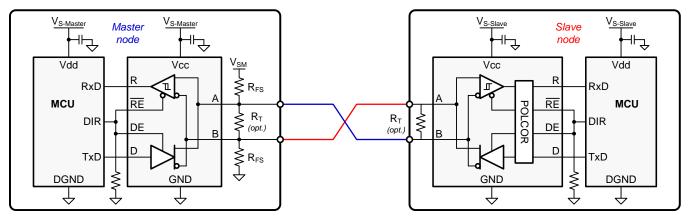

Figure 11 shows a simple point-to-point data link between a master node and a slave node. Because the master node with the failsafe biasing network determines the signal polarity on the bus, an RS-485 transceiver without polarity correction, such as SN65HVD82, suffices. All other bus nodes, typically performing as slaves, require the SN65HVD888 transceiver with polarity correction.

Figure 11. Point-To-Point Data Link With Cross-Wire Fault

Prior to initiating data transmission the master transceiver must idle for a time span that exceeds the maximum failsafe time,  $t_{FS-max}$ , of a slave transceiver. This idle time is accomplished by driving the direction control line, DIR, low. After a time, t >  $t_{FS-max}$ , the master begins transmitting data.

Because of the indicated cross-wire fault between master and slave, the slave node receives bus signals with reversed polarity. Assuming the slave node has just been connected to the bus, the direction-control pin is pulled-down during power-up and then is actively driven low by the slave MCU. The polarity correction begins as soon as the slave supply is established and ends after approximately 44 to 76 ms.

Copyright © 2013, Texas Instruments Incorporated

ZHCSB94-JULY 2013

www.ti.com.cn

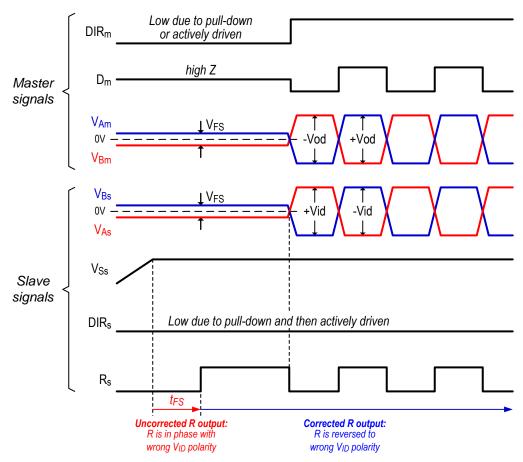

Figure 12. Polarity Correction Timing Prior to a Data Transmission

Initially the slave receiver assumes that the correct bus polarity is applied to the inputs and performs no polarity reversal. Because of the reversed polarity of the bus-failsafe voltage, the output of the slave receiver,  $R_S$ , turns low. After  $t_{FS}$  has passed and the receiver has detected the wrong bus polarity, the internal POLCOR logic reverses the input signal and  $R_S$  turns high.

At this point all incoming bus data with reversed polarity are polarity corrected within the transceiver. Because polarity correction is also applied to the transmit path, the data sent by the slave MCU are reversed by the POLCOR logic and then fed into the driver.

The reversed data from the slave MCU are reversed again by the cross-wire fault in the bus, and the correct bus polarity is reestablished at the master end.

This process repeats each time the device powers up and detects an incorrect bus polarity.

ZHCSB94-JULY 2013

www.ti.com.cn

## **APPLICATION INFORMATION**

## **Device Configuration**

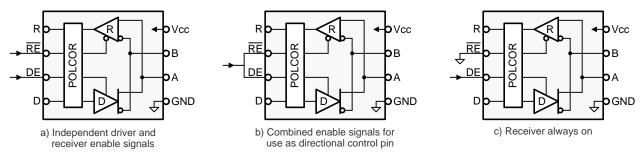

The SN65HVD888 is a half-duplex RS-485 transceiver operating from a single 5-V  $\pm$ 10% supply. The driver and receiver enable pins allow for the configuration of different operating modes.

Figure 13. Transceiver Configurations

Using independent enable lines provides the most flexible control as the lines allow for the driver and the receiver to be turned on and turned off individually. While this configuration requires two control lines, it allows for selective listening to the bus traffic, whether the driver is transmitting data or not. Only this configuration allows the SN65HVD888 to enter low-power standby mode because it allows both the driver and receiver to be disabled simultaneously.

Combining the enable signals simplifies the interface to the controller by forming a single direction-control signal. Thus, when the direction-control line is high, the transceiver is configured as a driver, while for a low the device operates as a receiver.

Tying the receiver enable to ground and controlling only the driver-enable input also uses only one control line. In this configuration a node not only receives the data on the bus sent by other nodes but also receives the data sent on the bus, enabling the node to verify the correct data has been transmitted.

### **Bus Design**

An RS-485 bus consists of multiple transceivers connected in parallel to a bus cable. To eliminate line reflections, each cable end is terminated with a termination resistor, RT, whose value matches the characteristic impedance, Z0, of the cable. This method, known as parallel termination, allows for relatively high data rates over long cable length.

Common cables used are unshielded twisted pair (UTP), such as low-cost CAT-5 cable with Z0 = 100  $\Omega$ , and RS-485 cable with Z0 = 120  $\Omega$ . Typical cable sizes are AWG 22 and AWG 24.

The maximum bus length is typically given as 4000 ft or 1200 m, and represents the length of an AWG 24 cable whose cable resistance approaches the value of the termination resistance, thus reducing the bus signal by half or 6 dB. Actual maximum usable cable length depends on the signaling rate, cable characteristics, and environmental conditions.

| V <sub>cc</sub> | R <sub>L</sub> Differential<br>Termination | R <sub>FS</sub> Pull up | R <sub>FS</sub> Pull down | V <sub>ID</sub> |

|-----------------|--------------------------------------------|-------------------------|---------------------------|-----------------|

|                 |                                            | 560 Ω                   | 560 Ω                     | 230 mV          |

| 5 V             | 54 Ω                                       | 1 ΚΩ                    | 1 ΚΩ                      | 131 mV          |

|                 |                                            | 4.7 ΚΩ                  | 4.7 ΚΩ                    | 29 mV           |

|                 |                                            | 10 ΚΩ                   | 10 KΩ                     | 13 mV           |

Table 1. VID with a Failsafe Network and Bus Termination

An external failsafe-resistor network must be used to ensure failsafe operation during an idle bus state. When the bus is not actively driven, the differential receiver inputs could float allowing the receiver output to assume a random output. A proper failsafe network forces the receiver inputs to exceed the VIT threshold, thus forcing the SN65HVD888 receiver output into the failsafe (high) state. Table 1 shows the differential input voltage ( $V_{ID}$ ) for various failsafe networks with a 54- $\Omega$  differential bus termination.

Copyright © 2013, Texas Instruments Incorporated

#### ZHCSB94-JULY 2013

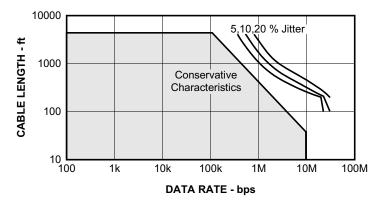

### Cable Length Versus Data Rate

There is an inverse relationship between data rate and cable length, which means the higher the data rate, the shorter the cable length; and conversely, the lower the data rate the longer the cable length. While most RS-485 systems use data rates between 10 kbps and 100 kbps, applications such as e-metering often operate at rates of up to 250 kbps even at distances of 4000 ft and longer. Longer distances are possible by allowing for small signal jitter of up to 5 or 10%.

Figure 14. Cable Length vs Data Rate Characteristic

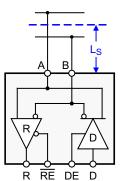

### **Stub Length**

When connecting a node to the bus, the distance between the transceiver inputs and the cable trunk, known as the stub, should be as short as possible. The reason for the short distance is because a stub presents a non-terminated piece of bus line which can introduce reflections if the distance is too long. As a general guideline, the electrical length or round-trip delay of a stub should be less than one-tenth of the rise time of the driver, thus leading to a maximum physical stub length of as shown in Equation 1.

$L_{Stub} \le 0.1 \times t_r \times v \times c$

where

- t<sub>r</sub> is the 10/90 rise time of the driver

- c is the speed of light  $(3 \times 10^8 \text{ m/s or } 9.8 \times 10^8 \text{ ft/s})$

- v is the signal velocity of the cable (v = 78%) or trace (v = 45%) as a factor of c

(1)

Based on Equation 1, with a minimum rise time of 400 ns, Equation 2 shows the maximum cable-stub length of the SN65HVD888.

$L_{Stub} \le 0.1 \times 400 \times 10^{-9} \times 3 \ 10^8 \times 0.78 = 9.4 \text{ m} \text{ (or } 30.6 \text{ ft)}$

(2)

Figure 15. Stub Length

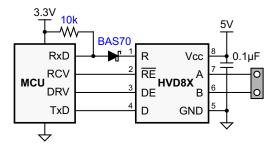

#### 3- to 5-V Interface

Interfacing the SN65HVD888 to a 3-V controller is easy. Because the 5-V logic inputs of the transceiver accept 3-V input signals they can be directly connected to the controller I/O. The 5-V receiver output, R, however must be level-shifted by a Schottky diode and a 10-k resistor to connect to the controller input (see Figure 16). When R is high, the diode is reverse biased and the controller supply potential lies at the controller RxD input. When R is low, the diode is forward biased and conducts. In this case only the diode forward voltage of 0.2 V lies at the controller RxD input.

Figure 16. 3-V to 5-V Interface

#### Noise Immunity

The input sensitivity of a standard RS-485 transceiver is  $\pm 200$  mV. When the differential input voltage, V<sub>ID</sub>, is greater than +200 mV, the receiver output turns high, for V<sub>ID</sub> < -200 mV the receiver outputs low.

The SN65HVD888 transceiver implements high receiver noise-immunity by providing a typical positive-going input threshold of 35 mV and a minimum hysteresis of 40 mV. In the case of a noisy input condition therefore, a differential noise voltage of up to 40 mV<sub>PP</sub> can be present without causing the receiver output to change states from high to low.

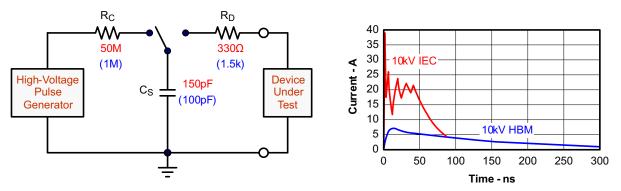

### **Transient Protection**

The bus terminals of the SN65HVD888 transceiver family possess on-chip ESD protection against ±16 kV HBM and ±12 kV IEC61000-4-2 contact discharge. The International Electrotechnical Commision (IEC) ESD test is far more severe than the HBM ESD test. The 50% higher charge capacitance,  $C_S$ , and 78% lower discharge resistance,  $R_D$  of the IEC model produce significantly higher discharge currents than the HBM model.

As stated in the IEC 61000-4-2 standard, contact discharge is the preferred transient protection test method. Although IEC air-gap testing is less repeatable than contact testing, air discharge protection levels are inferred from the contact discharge test results.

Figure 17. HBM and IEC-ESD Models and Currents in Comparison (HBM Values in Parenthesis)

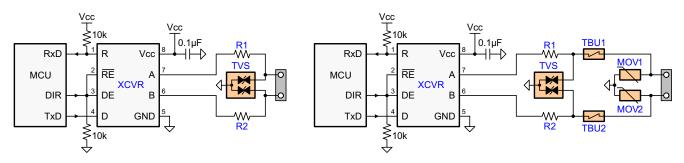

The on-chip implementation of IEC ESD protection significantly increases the robustness of equipment. Common discharge events occur because of human contact with connectors and cables. Designers may choose to implement protection against longer duration transients, typically referred to as surge transients. Figure 9 suggests two circuit designs providing protection against short and long duration surge transients, in addition to ESD and Electrical Fast Transients (EFT) transients. Table 2 lists the bill of materials for the external protection devices.

EFTs are generally caused by relay-contact bounce or the interruption of inductive loads. Surge transients often result from lightning strikes (direct strike or an indirect strike which induce voltages and currents), or the switching of power systems, including load changes and short circuits switching. These transients are often encountered in industrial environments, such as factory automation and power-grid systems.

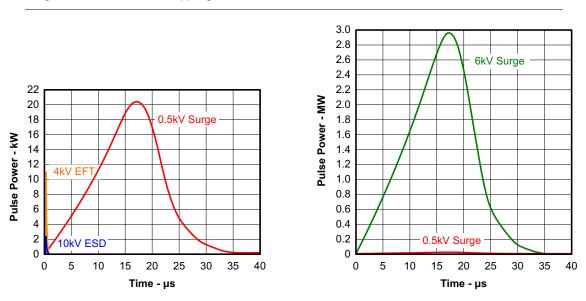

Figure 18 compares the pulse-power of the EFT and surge transients with the power caused by an IEC ESD transient. In the diagram on the left of Figure 18, the tiny blue blip in the bottom left corner represents the power of a 10-kV ESD transient, which already dwarfs against the significantly higher EFT power spike, and certainly dwarfs against the 500-V surge transient. This type of transient power is well representative of factory environments in industrial and process automation. The diagram on the fright of Figure 18 compares the enormous power of a 6-kV surge transient, most likely occurring in e-metering applications of power generating and power grid systems, with the aforementioned 500-V surge transient.

#### NOTE

The unit of the pulse-power changes from kW to MW, thus making the power of the 500-V surge transient almost dropping off the scale.

Figure 18. Power Comparison of ESD, EFT, and Surge Transients

In the case of surge transients, hgih-energy content is signified by long pulse duration and slow decaying pulse power

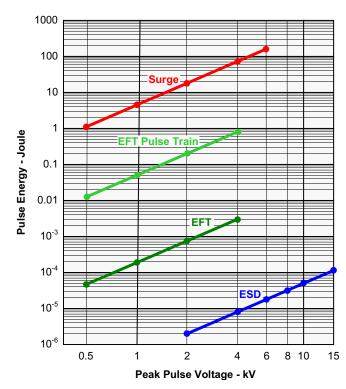

The electrical energy of a transient that is dumped into the internal protection cells of the transceiver is converted into thermal energy. This thermal energy heats the protection cells and literally destroys them, thus destroying the transceiver. Figure 19 shows the large differences in transient energies for single ESD, EFT, and surge transients as well as for an EFT pulse train, commonly applied during compliance testing.

ZHCSB94-JULY 2013

Figure 19. Comparison of Transient Energies

|  | Table | 2. | Bill | of | <b>Materials</b> |

|--|-------|----|------|----|------------------|

|--|-------|----|------|----|------------------|

| Device     | Function                                                      | Order Number       | Manufacturer |  |

|------------|---------------------------------------------------------------|--------------------|--------------|--|

| XCVR       | 5-V, 250-kbps RS-485 Transceiver                              | SN65HVD888         | ТІ           |  |

| R1, R2     | 10-Ω, Pulse-Proof Thick-Film Resistor                         | CRCW0603010RJNEAHP | Vishay       |  |

| TVS        | Bidirectional 400-W Transient Suppressor                      | CDSOT23-SM712      | Bourns       |  |

| TBU1, TBU2 | Bidirectional.                                                | TBU-CA-065-200-WH  | Bourns       |  |

| MOV1, MOV2 | 200mA Transient Blocking Unit 200-V, Metal-<br>Oxide Varistor | MOV-10D201K        | Bourns       |  |

Figure 20. Transient Protections Against ESD, EFT, and Surge Transients

The left circuit shown in Figure 20 provides surge protection of  $\geq$  500-V transients, while the right protection circuits can withstand surge transients of 5 kV.

## **Design and Layout Considerations For Transient Protection**

Because ESD and EFT transients have a wide frequency bandwidth from approximately 3 MHz to 3 GHz, high-frequency layout techniques must be applied during PCB design.

In order for PCB design to be successful, begin with the design of the protection circuit in mind.

- 1. Place the protection circuitry close to the bus connector to prevent noise transients from penetrating your board.

- 2. Use Vcc and ground planes to provide low-inductance. Note that high-frequency currents follow the path of least inductance and not the path of least impedance.

- 3. Design the protection components into the direction of the signal path. Do not force the transients currents to divert from the signal path to reach the protection device.

- Apply 100- to 220-nF bypass capacitors as close as possible to the V<sub>CC</sub>-pins of transceiver, UART, controller ICs on the board.

- 5. Use at least two vias for V<sub>CC</sub> and ground connections of bypass capacitors and protection devices to minimize effective via-inductance.

- 6. Use 1- to 10-k pullup or pulldown resistors for enable lines to limit noise currents in theses lines during transient events.

- 7. Insert pulse-proof resistors into the A and B bus lines if the TVS clamping voltage is higher than the specified maximum voltage of the transceiver bus terminals. These resistors limit the residual clamping current into the transceiver and prevent it from latching up.

- While pure TVS protection is sufficient for surge transients up to 1 kV, higher transients require metaloxide varistors (MOVs) which reduce the transients to a few-hundred volts of clamping voltage, and transient blocking units (TBUs) that limit transient current to some 200 mA.

#### **Isolated Bus Node Design**

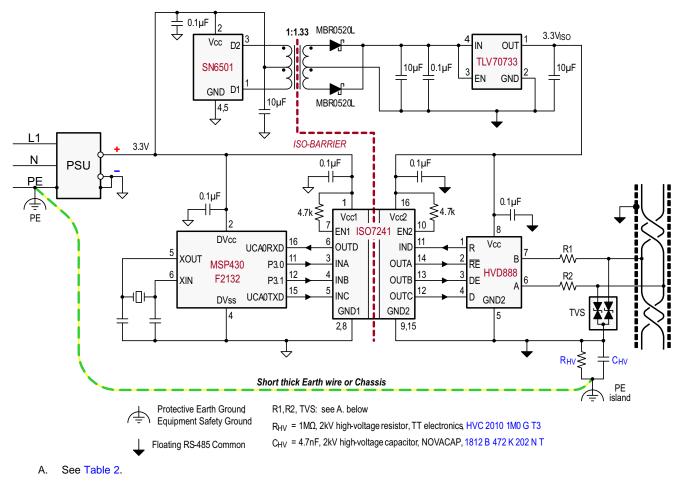

Many RS-485 networks use isolated bus nodes to prevent the creation of unintended ground loops and their disruptive impact on signal integrity. An isolated bus node typically includes a micro controller that connects to the bus transceiver through a multi-channel, digital isolator (Figure 21).

Figure 21. Isolated Bus Node With Transient Protection

Power isolation is accomplished using the push-pull transformer driver SN6501 and a low-cost LDO, TLV70733.

Signal isolation uses the quadruple digital isolator ISO7241. Notice that both enable inputs, EN1 and EN2, are pulled-up via 4.7-k resistors to limit input currents during transient events.

While the transient protection is similar to the one in Figure 20 (left circuit), an additional high-voltage capacitor diverts transient energy from the floating RS-485 common further towards Protective Earth (PE) ground. This diversion is necessary as noise transients on the bus are usually referred to Earth potential.

R<sub>VH</sub> refers to a high-voltage resistor, and in some applications even a varistor. This resistance is applied to prevent charging of the floating ground to dangerous potentials during normal operation.

Occasionally varistors are used instead of resistors in order to rapidly discharge  $C_{HV}$ , if expected that fast transients might charge  $C_{HV}$  to high-potentials.

Note that the PE island represents a copper island on the PCB for the provision of a short, thick Earth wire connecting this island to PE ground at the entrance of the power supply unit (PSU).

In equipment designs using a chassis, the PE connection is usually provided through the chassis itself. Typically the PE conductor is tied to the chassis at one end while the high-voltage components,  $C_{HV}$  and  $R_{HV}$ , are connecting to the chassis at the other end.

Copyright © 2013, Texas Instruments Incorporated

14-Jul-2013

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | •       | Pins | •    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty  | (2)                        |                  | (3)                |              | (4/5)          |         |

| SN65HVD888D      | ACTIVE | SOIC         | D       | 8    | 75   | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | HVD888         | Samples |

| SN65HVD888DR     | ACTIVE | SOIC         | D       | 8    | 2500 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | -40 to 85    | HVD888         | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

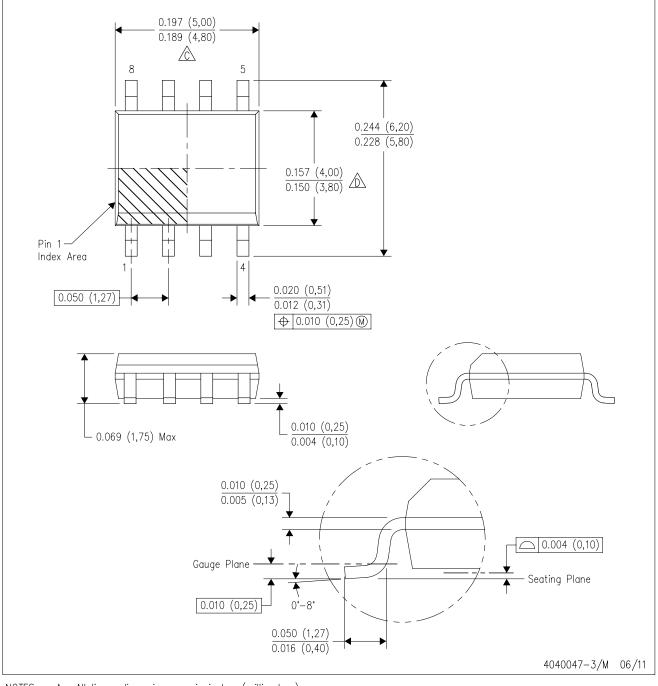

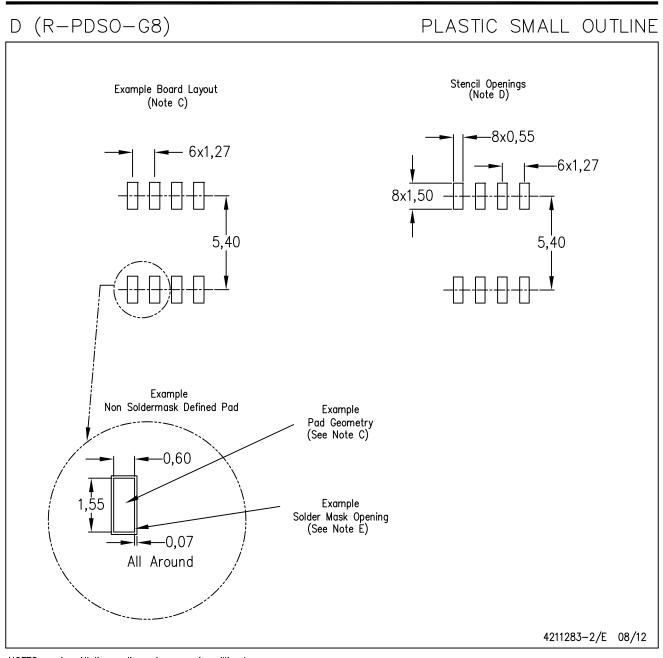

D (R-PDSO-G8)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### 重要声明

德州仪器(TI)及其下属子公司有权根据 JESD46 最新标准,对所提供的产品和服务进行更正、修改、增强、改进或其它更改,并有权根据 JESD48 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。所有产品的销售 都遵循在订单确认时所提供的TI 销售条款与条件。

TI保证其所销售的组件的性能符合产品销售时TI半导体产品销售条件与条款的适用规范。仅在TI保证的范围内,且TI认为有必要时才会使用测试或其它质量控制技术。除非适用法律做出了硬性规定,否则没有必要对每种组件的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应 用相关的风险,客户应提供充分的设计与操作安全措施。

TI不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予 的直接或隐含权 限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服 务的许可、授权、或认可。使用 此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它 知识产权方面的许可。

对于 TI 的产品手册或数据表中 TI 信息的重要部分,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况 下才允许进行 复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。

在转售 TI 组件或服务时,如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分,则会失去相关 TI 组件 或服务的所有明示或暗示授权,且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。

客户认可并同意,尽管任何应用相关信息或支持仍可能由 TI 提供,但他们将独力负责满足与其产品及在其应用中使用 TI 产品 相关的所有法律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,可预见 故障的危险后果、监测故障及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因 在此类安全关键应用中使用任何 TI 组件而对 TI 及其代理造成的任何损失。

在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特 有的可满足适用的功能安全性标准和要求的终端产品解决方案。尽管如此,此类组件仍然服从这些条款。

TI 组件未获得用于 FDA Class III(或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使 用的特别协议。

只有那些 TI 特别注明属于军用等级或"增强型塑料"的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同 意,对并非指定面向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独 力负责满足与此类使用相关的所有法律和法规要求。

TI 己明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。在任何情况下,因使用非指定产品而无法达到 ISO/TS16949 要求,TI不承担任何责任。

|               | 产品                                 |              | 应用                       |

|---------------|------------------------------------|--------------|--------------------------|

| 数字音频          | www.ti.com.cn/audio                | 通信与电信        | www.ti.com.cn/telecom    |

| 放大器和线性器件      | www.ti.com.cn/amplifiers           | 计算机及周边       | www.ti.com.cn/computer   |

| 数据转换器         | www.ti.com.cn/dataconverters       | 消费电子         | www.ti.com/consumer-apps |

| DLP® 产品       | www.dlp.com                        | 能源           | www.ti.com/energy        |

| DSP - 数字信号处理器 | www.ti.com.cn/dsp                  | 工业应用         | www.ti.com.cn/industrial |

| 时钟和计时器        | www.ti.com.cn/clockandtimers       | 医疗电子         | www.ti.com.cn/medical    |

| 接口            | www.ti.com.cn/interface            | 安防应用         | www.ti.com.cn/security   |

| 逻辑            | www.ti.com.cn/logic                | 汽车电子         | www.ti.com.cn/automotive |

| 电源管理          | www.ti.com.cn/power                | 视频和影像        | www.ti.com.cn/video      |

| 微控制器 (MCU)    | www.ti.com.cn/microcontrollers     |              |                          |

| RFID 系统       | www.ti.com.cn/rfidsys              |              |                          |

| OMAP应用处理器     | www.ti.com/omap                    |              |                          |

| 无线连通性         | www.ti.com.cn/wirelessconnectivity | 德州仪器在线技术支持社区 | www.deyisupport.com      |

邮寄地址: 上海市浦东新区世纪大道 1568 号,中建大厦 32 楼 邮政编码: 200122 Copyright © 2013 德州仪器 半导体技术(上海)有限公司