#### Data Sheet

#### January 25, 2008

## FN7311.8

# 250MHz Differential Line Receivers

The EL5172 and EL5372 are single and triple high bandwidth amplifiers designed to extract the difference signal from noisy environments. They are primarily targeted for applications such as receiving signals from twisted-pair lines or any application where common mode noise injection is likely to occur.

The EL5172 and EL5372 are stable for a gain of one and requires two external resistors to set the voltage gain.

The output common mode level is set by the reference pin (VREE), which has a -3dB bandwidth of over 120MHz. Generally, this pin is grounded but it can be tied to any voltage reference.

The output can deliver a maximum of ±60mA and is short circuit protected to withstand a temporary overload condition.

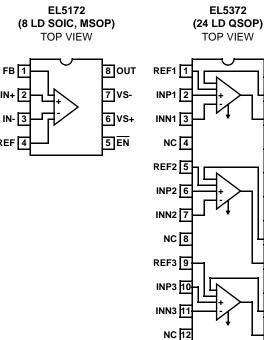

The EL5172 is available in the 8 Ld SOIC and 8 Ld MSOP packages and the EL5372 in a 24 Ld QSOP package. Both are specified for operation over the full -40°C to +85°C temperature range.

24 NC

23 FB1

22 OUT1

21 NC

20 VSP

19 VSN

18 NC 17 FB2

16 OUT2

15 EN

14 FB3 13 OUT3

## Pinouts

IN+

REF

#### Features

- Differential input range ±2.3V

- 250MHz 3dB bandwidth

- 800V/µs slew rate

- · 60mA maximum output current

- Single 5V or dual ±5V supplies

- Low power 5mA to 6mA per channel

- Pb-free available (RoHS compliant)

#### Applications

- · Twisted-pair receivers

- Differential line receivers

- VGA over twisted-pair

- ADSL/HDSL receivers

- · Differential to single-ended amplification

- Reception of analog signals in a noisy environment

#### **Ordering Information**

| PART NUMBER           | PART MARKING | PACKAGE                        | PKG. DWG. # |  |

|-----------------------|--------------|--------------------------------|-------------|--|

| EL5172IS              | 5172IS       | 8 Ld SOIC (150 mil)            |             |  |

| EL5172IS-T7*          | 5172IS       | 8 Ld SOIC (150 mil)            | MDP0027     |  |

| EL5172IS-T13*         | 5172IS       | 8 Ld SOIC (150 mil)            | MDP0027     |  |

| EL5172ISZ (Note)      | 5172ISZ      | 8 Ld SOIC (150 mil) (Pb-free)  | MDP0027     |  |

| EL5172ISZ-T7* (Note)  | 5172ISZ      | 8 Ld SOIC (150 mil) (Pb-free)  | MDP0027     |  |

| EL5172ISZ-T13* (Note) | 5172ISZ      | 8 Ld SOIC (150 mil) (Pb-free)  | MDP0027     |  |

| EL5172IY              | h            | 8 Ld MSOP (3.0mm)              | MDP0043     |  |

| EL5172IY-T7*          | h            | 8 Ld MSOP (3.0mm)              | MDP0043     |  |

| EL5172IY-T13*         | h            | 8 Ld MSOP (3.0mm)              | MDP0043     |  |

| EL5172IYZ (Note)      | BAAWA        | 8 Ld MSOP (3.0mm) (Pb-free)    | MDP0043     |  |

| EL5172IYZ-T7* (Note)  | BAAWA        | 8 Ld MSOP (3.0mm) (Pb-free)    | MDP0043     |  |

| EL5172IYZ-T13* (Note) | BAAWA        | 8 Ld MSOP (3.0mm) (Pb-free)    | MDP0043     |  |

| EL5372IU              | EL5372IU     | 24 Ld QSOP (150 mil)           | MDP0040     |  |

| EL5372IU-T7*          | EL5372IU     | 24 Ld QSOP (150 mil)           | MDP0040     |  |

| EL5372IU-T13*         | EL5372IU     | 24 Ld QSOP (150 mil)           | MDP0040     |  |

| EL5372IUZ (Note)      | EL5372IUZ    | 24 Ld QSOP (150 mil) (Pb-free) | MDP0040     |  |

| EL5372IUZ-T7* (Note)  | EL5372IUZ    | 24 Ld QSOP (150 mil) (Pb-free) | MDP0040     |  |

| EL5372IUZ-T13* (Note) | EL5372IUZ    | 24 Ld QSOP (150 mil) (Pb-free) | MDP0040     |  |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Absolute Maximum Ratings (T<sub>A</sub> = +25°C)

| Supply Voltage (V <sub>S</sub> + to V <sub>S</sub> -) |              |

|-------------------------------------------------------|--------------|

| Maximum Output Current.                               | ±60mA        |

| Storage Temperature Range65                           | °C to +150°C |

#### **Thermal Information**

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **Electrical Specifications** $V_{S^+} = +5V$ , $V_{S^-} = -5V$ , $T_A = +25^{\circ}C$ , $V_{IN} = 0V$ , $R_L = 500\Omega$ , $R_F = 0$ , $R_G = OPEN$ , $C_L = 2.7pF$ , Unless Otherwise Specified.

| PARAMETER                  | DESCRIPTION                                                                 | CONDITIONS                                                        | MIN  | TYP   | MAX  | UNIT   |

|----------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------|------|-------|------|--------|

| AC PERFORMA                | NCE                                                                         |                                                                   |      | 1     |      |        |

| BW                         | -3dB Bandwidth                                                              | A <sub>V</sub> =1, C <sub>L</sub> = 2.7pF                         |      | 250   |      | MHz    |

|                            |                                                                             | A <sub>V</sub> =2, R <sub>F</sub> = 1000Ω, C <sub>L</sub> = 2.7pF |      | 70    |      | MHz    |

|                            |                                                                             | $A_V = 10, R_F = 1000\Omega, C_L = 2.7 pF$                        |      | 10    |      | MHz    |

| BW                         | ±0.1dB Bandwidth                                                            | A <sub>V</sub> =1, C <sub>L</sub> = 2.7pF                         |      | 25    |      | MHz    |

| SR                         | Slew Rate                                                                   | V <sub>OUT</sub> = 3V <sub>P-P</sub> , 20% to 80%, EL5172         | 550  | 800   | 1000 | V/µs   |

|                            |                                                                             | V <sub>OUT</sub> = 3V <sub>P-P</sub> , 20% to 80%, EL5372         | 550  | 700   | 1000 | V/µs   |

| t <sub>STL</sub>           | Settling Time to 0.1%                                                       | $V_{OUT} = 2V_{P-P}$                                              |      | 10    |      | ns     |

| <sup>t</sup> OVR           | Output Overdrive Recovery Time                                              |                                                                   |      | 20    |      | ns     |

| GBWP                       | Gain Bandwidth Product                                                      |                                                                   |      | 100   |      | MHz    |

| V <sub>REF</sub> BW (-3dB) | V <sub>REF</sub> -3dB Bandwidth                                             | A <sub>V</sub> =1, C <sub>L</sub> = 2.7pF                         |      | 120   |      | MHz    |

| V <sub>REF</sub> SR        | V <sub>REF</sub> Slew Rate                                                  | V <sub>OUT</sub> = 2V <sub>P-P</sub> , 20% to 80%                 |      | 600   |      | V/µs   |

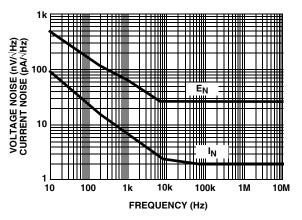

| V <sub>N</sub>             | Input Voltage Noise                                                         | at f = 11kHz                                                      |      | 26    |      | nV/√Hz |

| I <sub>N</sub>             | Input Current Noise                                                         | at f = 11kHz                                                      |      | 2     |      | pA/√Hz |

| HD2                        | Second Harmonic Distortion                                                  | V <sub>OUT</sub> = 1V <sub>P-P</sub> , 5MHz                       |      | -66   |      | dBc    |

|                            |                                                                             | V <sub>OUT</sub> = 2V <sub>P-P</sub> , 50MHz                      |      | -63   |      | dBc    |

| HD3                        | Third Harmonic Distortion                                                   | V <sub>OUT</sub> = 1V <sub>P-P</sub> , 5MHz                       |      | -84   |      | dBc    |

|                            |                                                                             | V <sub>OUT</sub> = 2V <sub>P-P</sub> , 50MHz                      |      | -76   |      | dBc    |

| dG                         | Differential Gain at 3.58MHz                                                | R <sub>L</sub> = 150Ω, A <sub>V</sub> = 2                         |      | 0.04  |      | %      |

| dθ                         | Differential Phase at 3.58MHz                                               | R <sub>L</sub> = 150Ω, A <sub>V</sub> = 2                         |      | 0.41  |      | 0      |

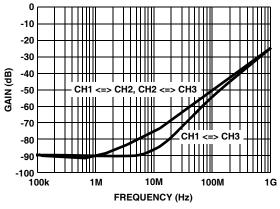

| es                         | Channel Separation at 100kHz                                                | EL5372 only                                                       |      | 90    |      | dB     |

| INPUT CHARAC               | TERISTICS                                                                   |                                                                   |      |       |      |        |

| V <sub>OS</sub>            | Input Referred Offset Voltage                                               |                                                                   |      | ±7    | ±25  | mV     |

| I <sub>IN</sub>            | Input Bias Current (V <sub>IN</sub> , V <sub>INB</sub> , V <sub>REF</sub> ) |                                                                   | -14  | -6    | -3   | μA     |

| R <sub>IN</sub>            | Differential Input Resistance                                               |                                                                   |      | 300   |      | kΩ     |

| C <sub>IN</sub>            | Differential Input Capacitance                                              |                                                                   |      | 1     |      | pF     |

| DMIR                       | Differential Input Range                                                    |                                                                   | ±2.1 | ±2.38 | ±2.5 | V      |

| CMIR+                      | Common Mode Positive Input Range at V <sub>IN</sub> +, V <sub>IN</sub> -    |                                                                   | 3.3  | 3.5   |      | V      |

| CMIR-                      | Common Mode Positive Input Range at $V_{IN}$ +, $V_{IN}$ -                  |                                                                   |      | -4.5  | -4.3 |        |

| V <sub>REFIN+</sub>        | Reference Input Positive Voltage Range                                      | $V_{IN} + = V_{IN} - = 0V$                                        | 3.3  | 3.7   |      | V      |

| V <sub>REFIN-</sub>        | Reference Input Negative Voltage Range                                      | $V_{IN} + = V_{IN} - = 0V$                                        |      | -3.9  | -3.6 |        |

# **Electrical Specifications** $V_{S}$ + = +5V, $V_{S}$ - = -5V, $T_{A}$ = +25°C, $V_{IN}$ = 0V, $R_{L}$ = 500 $\Omega$ , $R_{F}$ = 0, $R_{G}$ = OPEN, $C_{L}$ = 2.7pF, Unless Otherwise Specified. **(Continued)**

| PARAMETER              | DESCRIPTION                                | CONDITIONS                           | MIN                    | TYP   | MAX                    | UNIT |

|------------------------|--------------------------------------------|--------------------------------------|------------------------|-------|------------------------|------|

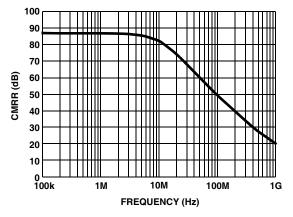

| CMRR                   | Input Common Mode Rejection Ratio          | $V_{IN} = \pm 2.5 V$                 | 75                     | 95    |                        | dB   |

| Gain                   | Gain Accuracy                              | V <sub>IN</sub> = 1                  | 0.985                  | 1     | 1.015                  | V    |

| OUTPUT CHAR            | ACTERISTICS                                |                                      | I                      |       |                        |      |

| V <sub>OUT</sub>       | Positive Output Voltage Swing              | $R_L = 500\Omega$ to GND             | 3.3                    | 3.63  |                        | V    |

|                        | Negative Output Voltage Swing              | $R_L = 500\Omega$ to GND             |                        | -3.87 | -3.5                   | V    |

| I <sub>OUT</sub> (Max) | Maximum Output Current                     | R <sub>L</sub> = 10Ω                 | ±60                    | ±95   |                        | mA   |

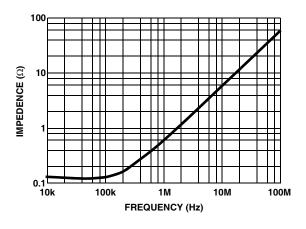

| R <sub>OUT</sub>       | Output Impedance                           |                                      |                        | 100   |                        | mΩ   |

| SUPPLY                 |                                            |                                      | L                      |       |                        |      |

| V <sub>SUPPLY</sub>    | Supply Operating Range                     | V <sub>S</sub> + to V <sub>S</sub> - | 4.75                   |       | 11                     | V    |

| I <sub>S (on)</sub>    | Power Supply Current Per Channel - Enabled |                                      | 4.6                    | 5.6   | 7                      | mA   |

| I <sub>S (off)</sub> + | Positive Power Supply Current - Disabled   | EN pin tied to 4.8V, EL5172          |                        | 80    | 100                    | μA   |

|                        |                                            | EN pin tied to 4.8V, EL5372          |                        | 1.7   | 5                      | μA   |

| I <sub>S (off)</sub> - | Negative Power Supply Current - Disabled   |                                      | -150                   | -120  | -90                    | μA   |

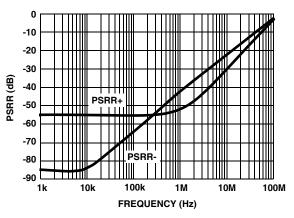

| PSRR                   | Power Supply Rejection Ratio               | V <sub>S</sub> from ±4.5V to ±5.5V   | 50                     | 58    |                        | dB   |

| ENABLE                 |                                            |                                      | <b>I</b>               |       |                        |      |

| t <sub>EN</sub>        | Enable Time                                |                                      |                        | 150   |                        | ns   |

| t <sub>DS</sub>        | Disable Time                               |                                      |                        | 1.4   |                        | μs   |

| V <sub>IH</sub>        | EN Pin Voltage for Power-up                |                                      |                        |       | V <sub>S</sub> + - 1.5 | V    |

| V <sub>IL</sub>        | EN Pin Voltage for Shut-down               |                                      | V <sub>S</sub> + - 0.5 |       |                        | V    |

| I <sub>IH-EN</sub>     | EN Pin Input Current High Per Channel      | At V <sub>EN</sub> = 5V              |                        | 40    | 60                     | μA   |

| I <sub>IL-EN</sub>     | EN Pin Input Current Low Per Channel       | At V <sub>EN</sub> = 0V              | -10                    | -3    |                        | μA   |

# **Pin Descriptions**

| EL5172 | EL5372               | PIN NAME   | PIN FUNCTION                                                                           |

|--------|----------------------|------------|----------------------------------------------------------------------------------------|

| 1      |                      | FB         | Feedback input                                                                         |

| 2      |                      | IN+        | Non-inverting input                                                                    |

| 3      |                      | IN-        | Inverting input                                                                        |

| 4      |                      | REF        | Sets the common mode output voltage level                                              |

| 5      |                      | EN         | Enabled when this pin is floating or the applied voltage $\leq$ V_S+ - 1.5             |

| 6      |                      | VS+        | Positive supply voltage                                                                |

| 7      |                      | VS-        | Negative supply voltage                                                                |

| 8      |                      | OUT        | Output voltage                                                                         |

|        | 1, 5, 9              | REF1, 2, 3 | Reference input, controls common-mode output voltage                                   |

|        | 2, 6, 10             | INP1, 2, 3 | Non-inverting inputs                                                                   |

|        | 3, 7, 11             | INN1, 2, 3 | Inverting inputs                                                                       |

|        | 4, 8, 12, 18, 21, 24 | NC         | No connect; grounded for best crosstalk performance                                    |

|        | 13, 16, 22           | OUT1, 2, 3 | Non-inverting outputs                                                                  |

|        | 14, 17, 23           | FB1, 2, 3  | Feedback from outputs                                                                  |

|        | 15                   | EN         | Enabled when this pin is floating or the applied voltage $\leq$ V <sub>S</sub> + - 1.5 |

|        | 19                   | VSN        | Negative supply                                                                        |

|        | 20                   | VSP        | Positive supply                                                                        |

6

intersil

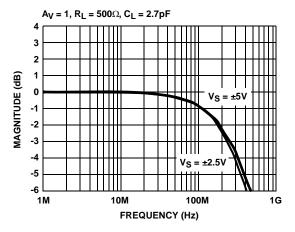

#### **Typical Performance Curves**

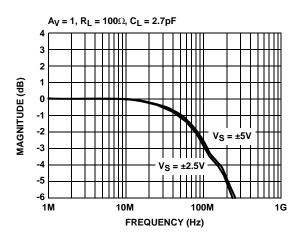

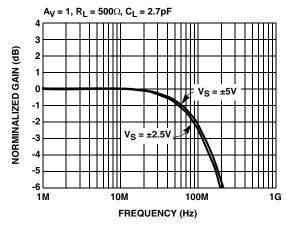

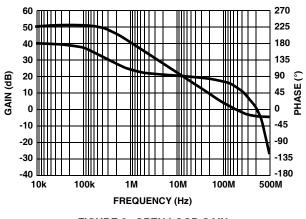

FIGURE 1. FREQUENCY RESPONSE vs SUPPLY VOLTAGE

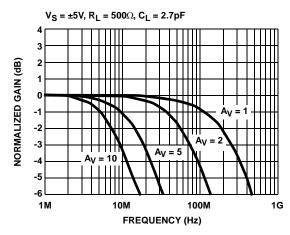

FIGURE 3. FREQUENCY RESPONSE vs VARIOUS GAIN

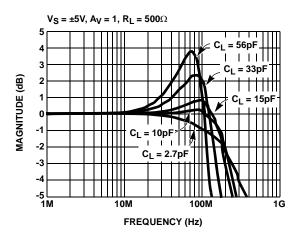

FIGURE 5. FREQUENCY RESPONSE vs CL

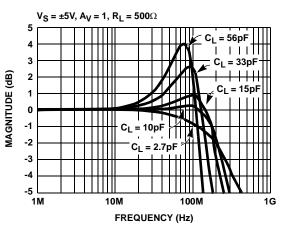

FIGURE 2. FREQUENCY RESPONSE vs SUPPLY VOLTAGE

FIGURE 4. FREQUENCY RESPONSE vs CL

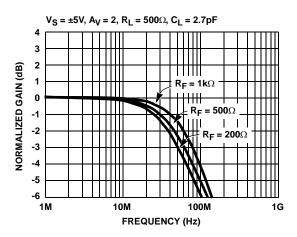

FIGURE 6. FREQUENCY RESPONSE FOR VARIOUS RF

#### Typical Performance Curves (Continued)

FIGURE 7. FREQUENCY RESPONSE FOR VREF

FIGURE 9. OUTPUT IMPEDANCE vs FREQUENCY

FIGURE 11. CMRR vs FREQUENCY

FIGURE 10. PSRR vs FREQUENCY

FIGURE 12. VOLTAGE AND CURRENT NOISE vs FREQUENCY

#### Typical Performance Curves (Continued)

FIGURE 13. CHANNEL ISOLATION vs FREQUENCY

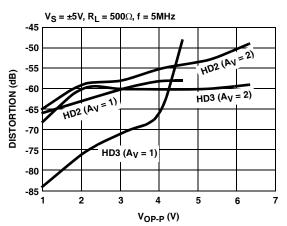

FIGURE 14. HARMONIC DISTORTION vs OUTPUT VOLTAGE

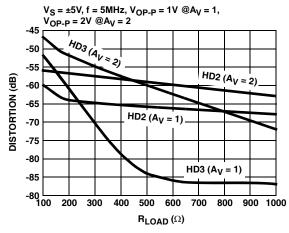

FIGURE 15. HARMONIC DISTORTION vs LOAD RESISTANCE

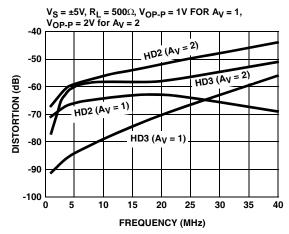

FIGURE 16. HARMONIC DISTORTION vs FREQUENCY

9

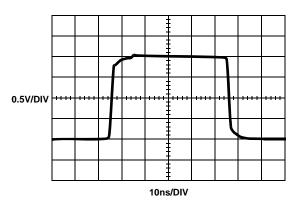

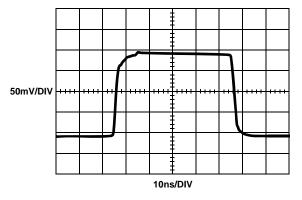

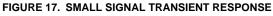

FIGURE 18. LARGE SIGNAL TRANSIENT RESPONSE

## Typical Performance Curves (Continued)

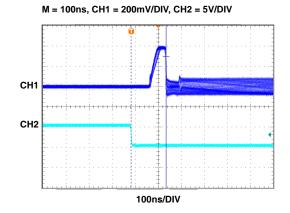

FIGURE 20. DISABLED RESPONSE

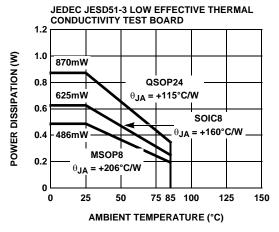

FIGURE 21. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

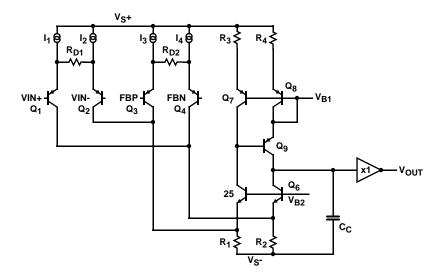

# Simplified Schematic

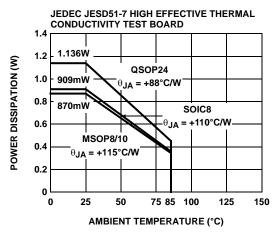

FIGURE 22. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

in<u>tersi</u>l

10

# Description of Operation and Application Information

#### **Product Description**

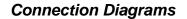

The EL5172 and EL5372 are wide bandwidth, low power and single/differential ended to single ended output amplifiers. The EL5172 is a single channel differential to single ended amplifier. The EL5372 is a triple channel differential to single ended amplifier. The EL5172 and EL5372 are internally compensated for closed loop gain of +1 or greater. Connected in gain of 1 and driving a 500 $\Omega$ load, the EL5172 and EL5372 have a -3dB bandwidth of 250MHz. Driving a 150 $\Omega$  load at gain of 2, the bandwidth is about 50MHz. The bandwidth at the REF input is about 450MHz. The EL5172 and EL5372 are available with a power-down feature to reduce the power while the amplifier is disabled.

#### Input, Output and Supply Voltage Range

The EL5172 and EL5372 have been designed to operate with a single supply voltage of 5V to 10V or a split supplies with its total voltage from 5V to 10V. The amplifiers have an input common mode voltage range from -4.3V to 3.3V for  $\pm$ 5V supply. The differential mode input range (DMIR) between the two inputs is about from -2.3V to +2.3V. The input voltage range at the REF pin is from -3.6V to 3.3V. If the input common mode or differential mode signal is outside the above-specified ranges, it will cause the output signal to be distorted.

The output of the EL5172 and EL5372 can swing from -3.8V to 3.6V at  $500\Omega$  load at  $\pm$ 5V supply. As the load resistance becomes lower, the output swing is reduced respectively.

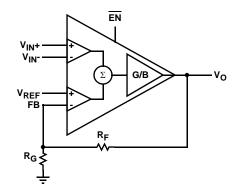

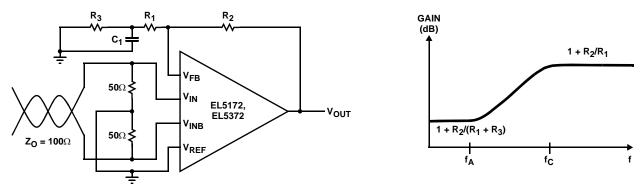

#### **Over All Gain Settings**

The gain setting for the EL5172 and the EL5372 is similar to the conventional operational amplifier. The output voltage is equal to the difference of the inputs plus  $V_{\text{REF}}$  and then times the gain.

$$V_{O} = (V_{IN} + -V_{IN} - +V_{REF}) \times \left(1 + \frac{R_{F}}{R_{G}}\right)$$

FIGURE 23.

#### Choice of Feedback Resistor and Gain Bandwidth Product

For applications that require a gain of +1, no feedback resistor is required. Just short the OUT pin to the FB pin. For gains greater than +1, the feedback resistor forms a pole with the parasitic capacitance at the inverting input. As this pole becomes smaller, the amplifier's phase margin is reduced. This causes ringing in the time domain and peaking in the frequency domain. Therefore, R<sub>F</sub> has some maximum value that should not be exceeded for optimum performance. If a large value of R<sub>F</sub> must be used, a small capacitor in the few Pico farad range in parallel with R<sub>F</sub> can help to reduce the ringing and peaking at the expense of reducing the bandwidth.

The bandwidth of the EL5172 and EL5372 depends on the load and the feedback network. R<sub>F</sub> and R<sub>G</sub> appear in parallel with the load for gains other than +1. As this combination gets smaller, the bandwidth falls off. Consequently, R<sub>F</sub> also has a minimum value that should not be exceeded for optimum bandwidth performance. For a gain of +1, R<sub>F</sub> = 0 is optimum. For the gains other than +1, optimum response is obtained with R<sub>F</sub> between 500 $\Omega$  to 1k $\Omega$ . For A<sub>V</sub> = 2 and R<sub>F</sub> = R<sub>G</sub> = 1k $\Omega$ , the BW is about 80MHz and the frequency response is very flat.

The EL5172 and EL5372 have a gain bandwidth product of 100MHz. For gains  $\geq$ 5, its bandwidth can be predicted by Equation 1:

| $Gain \times BW = 100MHz$ | (EQ. 1) |

|---------------------------|---------|

|---------------------------|---------|

#### Driving Capacitive Loads and Cables

The EL5172 and EL5372 can drive 56pF capacitance in parallel with 500 $\Omega$  load to ground with 4dB of peaking at gain of +1. If less peaking is desired in applications, a small series resistor (usually between 5 $\Omega$  to 50 $\Omega$ ) can be placed in series with each output to eliminate most peaking. However, this will reduce the gain slightly. If the gain setting is greater than 1, the gain resistor R<sub>G</sub> can then be chosen to make up for any gain loss which may be created by the additional series resistor at the output.

When used as a cable driver, double termination is always recommended for reflection-free performance. For those applications, a back-termination series resistor at the amplifier's output will isolate the amplifier from the cable and allow extensive capacitive drive. However, other applications may have high capacitive loads without a back-termination resistor. Again, a small series resistor at the output can help to reduce peaking.

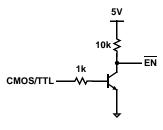

#### Disable/Power-Down

The EL5172 and EL5372 can be disabled and its outputs placed in a high impedance state. The turn-off time is about 1.4 $\mu$ s and the turn-on time is about 150ns. When disabled, the amplifier's supply current is reduced to 80 $\mu$ A for I<sub>S</sub>+ and

120µA for I<sub>S</sub>- typically, thereby effectively eliminating the power consumption. The amplifier's power-down can be controlled by standard CMOS signal levels at the ENABLE pin. The applied logic signal is relative to V<sub>S</sub>+ pin. Letting the EN pin float or applying a signal that is less than 1.5V below V<sub>S</sub>+ will enable the amplifier. The amplifier will be disabled when the signal at EN pin is above V<sub>S</sub>+ - 0.5V. If a TTL signal is used to control the enabled/disabled function, Figure 24 could be used to convert the TTL signal to CMOS signal.

#### **Output Drive Capability**

The EL5172 and EL5372 have internal short circuit protection. Its typical short circuit current is  $\pm$ 95mA. If the output is shorted indefinitely, the power dissipation could easily increase such that the part will be destroyed. Maximum reliability is maintained if the output current never exceeds  $\pm$ 60mA. This limit is set by the design of the internal metal interconnections.

#### **Power Dissipation**

With the high output drive capability of the EL5172 and EL5372, it is possible to exceed the +135°C absolute maximum junction temperature under certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for the application to determine if the load conditions or package types need to be modified for the amplifier to remain in the safe operating area.

The maximum power dissipation allowed in a package is determined according to Equation 2:

$$PD_{MAX} = \frac{T_{JMAX} - T_{AMAX}}{\Theta_{JA}}$$

(EQ. 2)

- T<sub>JMAX</sub> = Maximum junction temperature

- T<sub>AMAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

Assuming the REF pin is tied to GND for  $V_S = \pm 5V$ application, the maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or: For sourcing, use Equation 3:

$$PD_{MAX} = \left[ V_{S} \times I_{SMAX} + (V_{S} + -V_{OUT}) \times \frac{V_{OUT}}{R_{LOAD}} \right] \times i$$

(EQ. 3)

For sinking, use Equation 4:

$$PD_{MAX} = [V_{S} \times I_{SMAX} + (V_{OUT} - V_{S}) \times I_{LOAD}] \times i$$

(EQ. 4)

Where:

- V<sub>S</sub> = Total supply voltage

- I<sub>SMAX</sub> = Maximum quiescent supply current per channel

- V<sub>OUT</sub> = Maximum output voltage of the application

- R<sub>LOAD</sub> = Load resistance

- I<sub>LOAD</sub> = Load current

- i = Number of channels

By setting the two  $PD_{MAX}$  equations equal to each other, we can solve the output current and  $R_{LOAD}$  to avoid the device overheat.

# Power Supply Bypassing and Printed Circuit Board Layout

As with any high frequency device, a good printed circuit board layout is necessary for optimum performance. Lead lengths should be as short as possible. The power supply pin must be well bypassed to reduce the risk of oscillation. For normal single supply operation, where the V<sub>S</sub>- pin is connected to the ground plane, a single 4.7µF tantalum capacitor in parallel with a 0.1µF ceramic capacitor from V<sub>S</sub>+ to GND will suffice. This same capacitor combination should be placed at each supply pin to ground if split supplies are to be used. In this case, the V<sub>S</sub>- pin becomes the negative supply rail.

For good AC performance, parasitic capacitance should be kept to a minimum. Use of wire wound resistors should be avoided because of their additional series inductance. Use of sockets should also be avoided if possible. Sockets add parasitic inductance and capacitance that can result in compromised performance. Minimizing parasitic capacitance at the amplifier's inverting input pin is very important. The feedback resistor should be placed very close to the inverting input pin. Strip line design techniques are recommended for the signal traces.

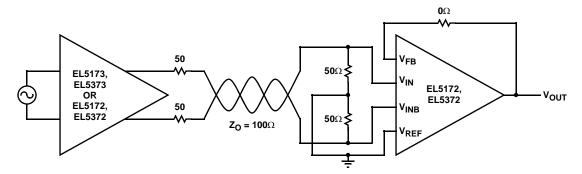

#### **Typical Applications**

FIGURE 25. TWISTED PAIR CABLE RECEIVER

As the signal is transmitted through a cable, the high frequency signal will be attenuated. One way to compensate for this loss is to boost the high frequency gain at the receiver side.

#### Level Shifter and Signal Summer

The EL5172 and EL5372 contains two pairs of differential pair input stages, which make sure that the inputs are all high impedance inputs. To take advantage of the two high impedance inputs, the EL5172 and EL5372 can be used as a signal summer to add two signals together. One signal can be applied to VIN+, the second signal can be applied to REF and V<sub>IN</sub>- is ground. The output is equal to Equation 5:

$$V_{O} = (V_{IN} + V_{REF}) \times Gain$$

(EQ. 5)

Also, the EL5172 and EL5372 can be used as a level shifter by applying a level control signal to the REF input.

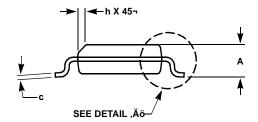

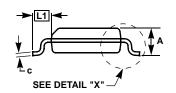

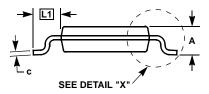

# Small Outline Package Family (SO)

#### MDP0027

SMALL OUTLINE PACKAGE FAMILY (SO)

|        |       |       |                  | INCHES                    |                  |                  |                  |           |       |

|--------|-------|-------|------------------|---------------------------|------------------|------------------|------------------|-----------|-------|

| SYMBOL | SO-8  | SO-14 | SO16<br>(0.150") | SO16 (0.300")<br>(SOL-16) | SO20<br>(SOL-20) | SO24<br>(SOL-24) | SO28<br>(SOL-28) | TOLERANCE | NOTES |

| А      | 0.068 | 0.068 | 0.068            | 0.104                     | 0.104            | 0.104            | 0.104            | MAX       | -     |

| A1     | 0.006 | 0.006 | 0.006            | 0.007                     | 0.007            | 0.007            | 0.007            | ±0.003    | -     |

| A2     | 0.057 | 0.057 | 0.057            | 0.092                     | 0.092            | 0.092            | 0.092            | ±0.002    | -     |

| b      | 0.017 | 0.017 | 0.017            | 0.017                     | 0.017            | 0.017            | 0.017            | ±0.003    | -     |

| С      | 0.009 | 0.009 | 0.009            | 0.011                     | 0.011            | 0.011            | 0.011            | ±0.001    | -     |

| D      | 0.193 | 0.341 | 0.390            | 0.406                     | 0.504            | 0.606            | 0.704            | ±0.004    | 1, 3  |

| Е      | 0.236 | 0.236 | 0.236            | 0.406                     | 0.406            | 0.406            | 0.406            | ±0.008    | -     |

| E1     | 0.154 | 0.154 | 0.154            | 0.295                     | 0.295            | 0.295            | 0.295            | ±0.004    | 2, 3  |

| е      | 0.050 | 0.050 | 0.050            | 0.050                     | 0.050            | 0.050            | 0.050            | Basic     | -     |

| L      | 0.025 | 0.025 | 0.025            | 0.030                     | 0.030            | 0.030            | 0.030            | ±0.009    | -     |

| L1     | 0.041 | 0.041 | 0.041            | 0.056                     | 0.056            | 0.056            | 0.056            | Basic     | -     |

| h      | 0.013 | 0.013 | 0.013            | 0.020                     | 0.020            | 0.020            | 0.020            | Reference | -     |

| Ν      | 8     | 14    | 16               | 16                        | 20               | 24               | 28               | Reference | -     |

Rev. M 2/07

NOTES:

- 1. Plastic or metal protrusions of 0.006" maximum per side are not included.

- 2. Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994

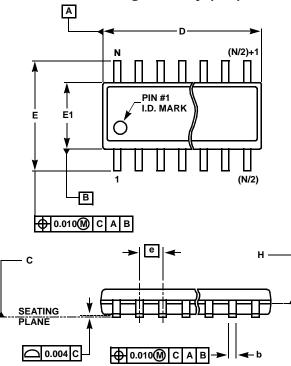

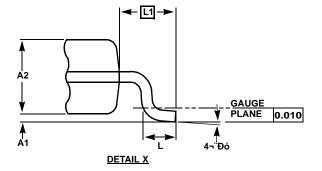

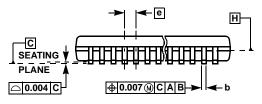

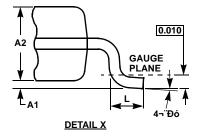

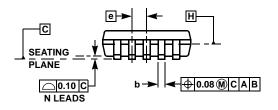

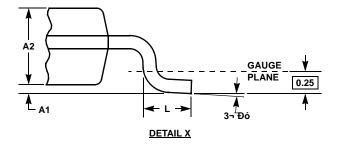

# Quarter Size Outline Plastic Packages Family (QSOP)

#### MDP0040

QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|        | INCHES |        |        |           |            |

|--------|--------|--------|--------|-----------|------------|

| SYMBOL | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES      |

| А      | 0.068  | 0.068  | 0.068  | Max.      | -          |

| A1     | 0.006  | 0.006  | 0.006  | ±0.002    | -          |

| A2     | 0.056  | 0.056  | 0.056  | ±0.004    | -          |

| b      | 0.010  | 0.010  | 0.010  | ±0.002    | -          |

| с      | 0.008  | 0.008  | 0.008  | ±0.001    | -          |

| D      | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3       |

| E      | 0.236  | 0.236  | 0.236  | ±0.008    | -          |

| E1     | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3       |

| е      | 0.025  | 0.025  | 0.025  | Basic     | -          |

| L      | 0.025  | 0.025  | 0.025  | ±0.009    | -          |

| L1     | 0.041  | 0.041  | 0.041  | Basic     | -          |

| N      | 16     | 24     | 28     | Reference | -          |

|        |        |        |        | R         | ev. F 2/07 |

NOTES:

1. Plastic or metal protrusions of 0.006" maximum per side are not included.

2. Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

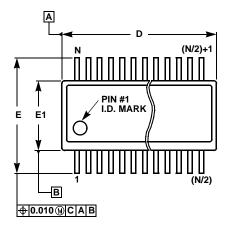

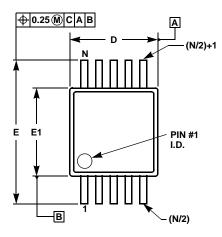

## Mini SO Package Family (MSOP)

MINI SO PACKAGE FAMILY

|        | MILLIN | <b>IETERS</b> |             |       |

|--------|--------|---------------|-------------|-------|

| SYMBOL | MSOP8  | MSOP10        | TOLERANCE   | NOTES |

| А      | 1.10   | 1.10          | Max.        | -     |

| A1     | 0.10   | 0.10          | ±0.05       | -     |

| A2     | 0.86   | 0.86          | ±0.09       | -     |

| b      | 0.33   | 0.23          | +0.07/-0.08 | -     |

| С      | 0.18   | 0.18          | ±0.05       | -     |

| D      | 3.00   | 3.00          | ±0.10       | 1, 3  |

| Е      | 4.90   | 4.90          | ±0.15       | -     |

| E1     | 3.00   | 3.00          | ±0.10       | 2, 3  |

| е      | 0.65   | 0.50          | Basic       | -     |

| L      | 0.55   | 0.55          | ±0.15       | -     |

| L1     | 0.95   | 0.95          | Basic       | -     |

| Ν      | 8      | 10            | Reference   | -     |

NOTES:

- 1. Plastic or metal protrusions of 0.15mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25mm maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com