Technical Documents

bq24250, bq24251, bq24253

SLUSBA1H-OCTOBER 2012-REVISED AUGUST 2015

## bq2425x 2A Single-Input I<sup>2</sup>C, Stand-Alone Switched-Mode Li-Ion Battery Charger With **Power-Path Management**

### **Features**

- High-Efficiency Switched-Mode Charger With Separate Power Path

- Startup System From Deeply Discharged or Missing Battery

- **USB Charging Compliant**

- Selectable Input Current Limit of 100 mA, 500 mA, 900 mA, 1.5 A, and 2 A

- BC1.2 Compatible D+, D- Detection

- In Host Mode (After I<sup>2</sup>C Communication Starts and Before Watchdog Timer Times Out)

- Programmable Battery Charge Voltage,

- Programmable Charge Current (I<sub>CHG</sub>)

- Programmable Input Current Limit (I<sub>LIM</sub>)

- Programmable Input Voltage-Based Dynamic Power Management Threshold, (VIN DPM)

- Programmable Input Overvoltage Protection Threshold (V<sub>OVP</sub>)

- Programmable Safety Timer

- Resistor Programmable Defaults for:

- I<sub>CHG</sub> up to 2 A With Current Monitoring Output (ISET)

- I<sub>LIM</sub> up to 2 A With Current Monitoring Output (ILIM)

- V<sub>IN DPM</sub> (VDPM)

- Watchdog Timer Disable Bit

- Integrated 4.9 V, 50 mA LDO

- Complete System-Level Protection

- Input UVLO, Input Overvoltage Protection (OVP), Battery OVP, Sleep Mode, VIN\_DPM

- Input Current Limit

- Charge Current Limit

- Thermal Regulation

- Thermal Shutdown

- Voltage-Based, JEITA Compatible NTC Monitoring Input

- Safety Timer

- 22 V Absolute Maximum Input Voltage Rating

- 10.5 V Maximum Operating Input Voltage

- Low R<sub>DS(on)</sub> Integrated Power FETs for a Charging Rate of up to 2 A

- Open-Drain Status Outputs

- Synchronous Fixed-Frequency PWM Controller Operating at 3 MHz for Small Inductor Support

- AnyBoot Robust Battery Detection Algorithm

- Charge Time Optimizer for Improved Charge Times at Any Given Charge Current

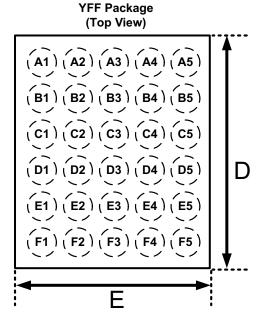

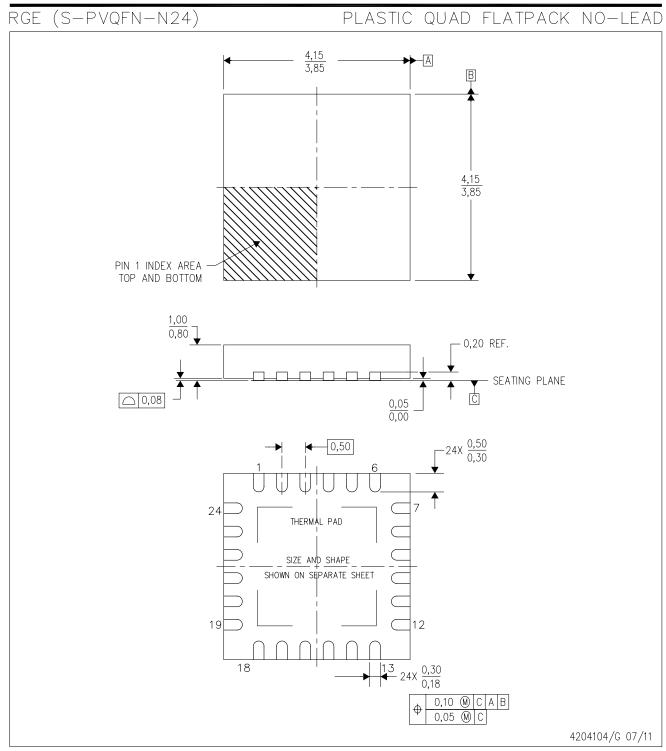

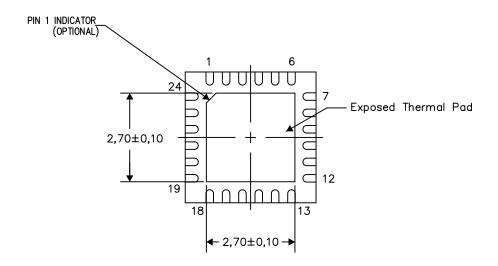

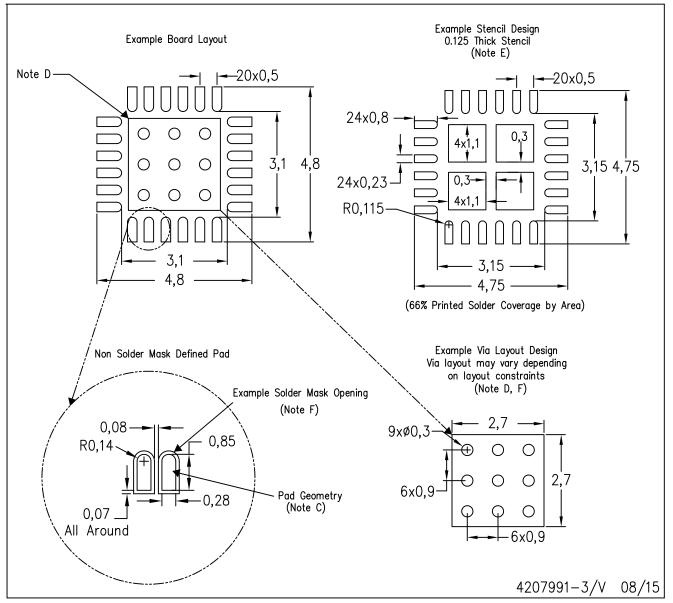

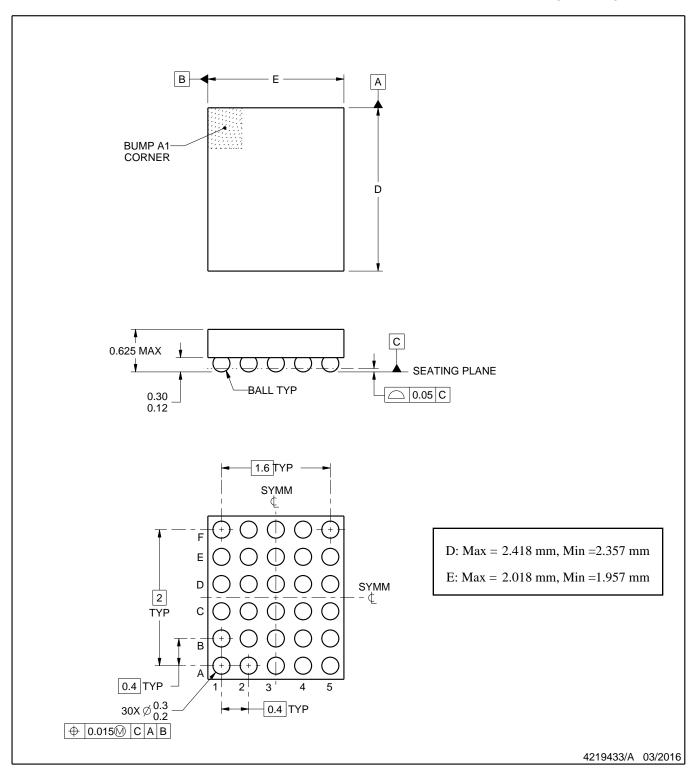

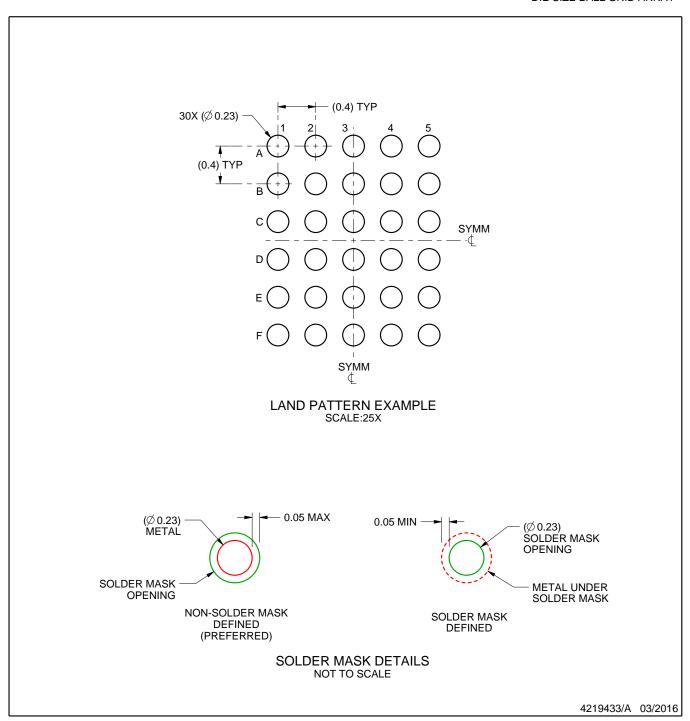

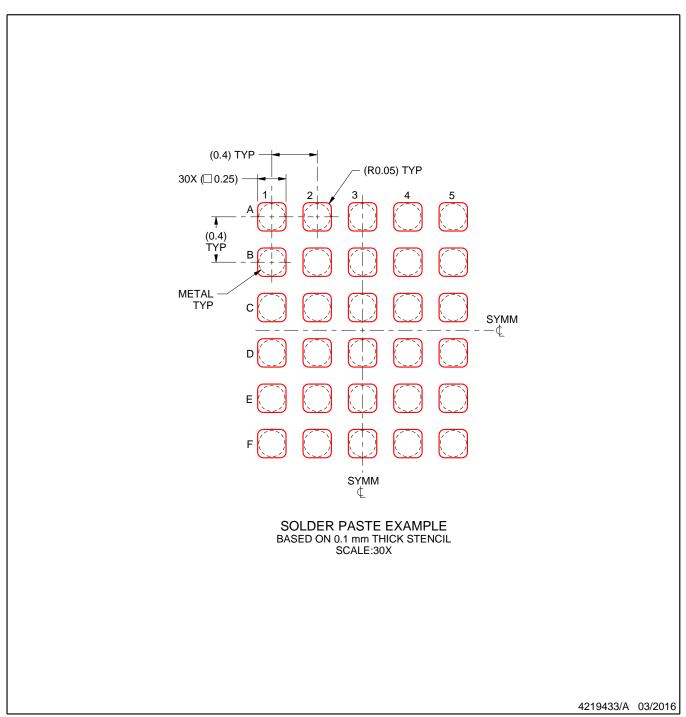

- 2.40-mm x 2.00-mm 30-Ball DSBGA and 4-mm x 4-mm 24-Pin QFN Packages

## 2 Applications

- Mobile Phones and Smart Phones

- MP3 Players

- Portable Media Players

- Handheld Devices

## 3 Description

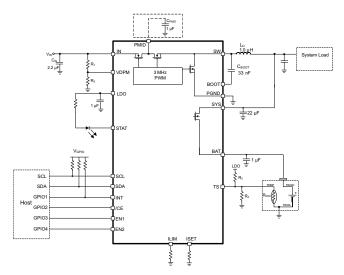

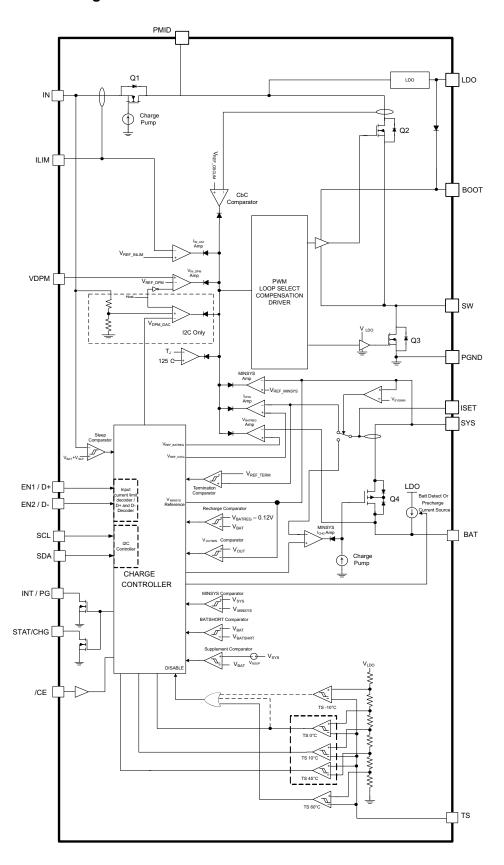

The bq24250, bq24251, and bq24253 are highly integrated single-cell Li-Ion battery chargers and system power-path management devices targeted for space-limited, portable applications with high-capacity batteries. The single-cell charger has a single input that operates from either a USB port or an AC wall adapter for a versatile solution.

## Device Information<sup>(1)</sup>

| PART NUMBER        | PACKAGE    | BODY SIZE (NOM)   |

|--------------------|------------|-------------------|

| bq24250            | VQFN (24)  | 4.00 mm x 4.00 mm |

| bq24251<br>bq24253 | DSBGA (30) | 2.40 mm x 2.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

### **Table of Contents**

| 1 | Ecoturos 1                             |    | 9.4 Device Functional Modes          | 30 |

|---|----------------------------------------|----|--------------------------------------|----|

| • | Features 1                             |    |                                      |    |

| 2 | Applications 1                         |    | 9.5 Programming                      |    |

| 3 | Description 1                          |    | 9.6 Register Maps                    | 33 |

| 4 | Revision History2                      | 10 | Application and Implementation       | 39 |

| 5 | Description (continued) 4              |    | 10.1 Application Information         | 39 |

| 6 | Device Options4                        |    | 10.2 Typical Application             | 39 |

| 7 | Pin Configuration and Functions        | 11 | Power Supply Recommendations         | 42 |

|   | •                                      | 12 | Layout                               | 42 |

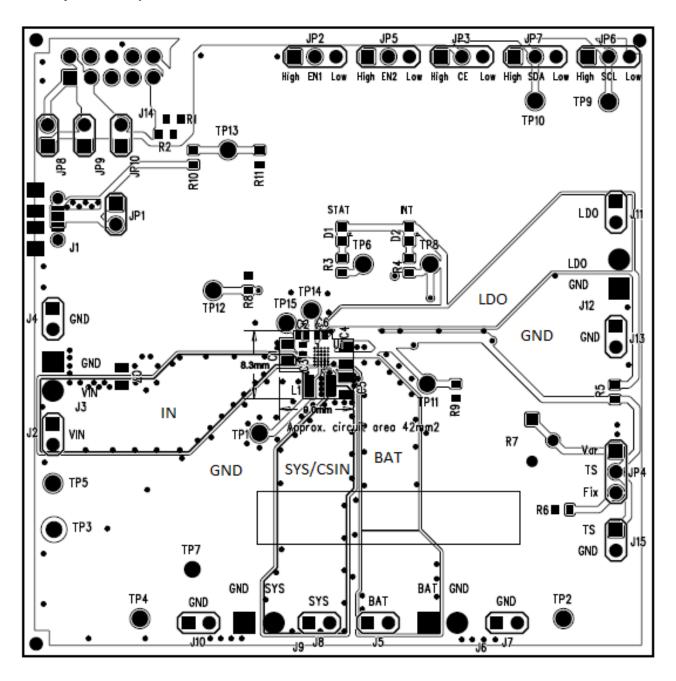

| 8 | Specifications                         |    | 12.1 Layout Guidelines               | 42 |

|   | 8.1 Absolute Maximum Ratings           |    | 12.2 Layout Example                  |    |

|   | 8.2 ESD Ratings 8                      |    | 12.3 Thermal Considerations          |    |

|   | 8.3 Recommended Operating Conditions 8 | 42 |                                      |    |

|   | 8.4 Thermal Information9               | 13 | Device and Documentation Support     |    |

|   | 8.5 Electrical Characteristics9        |    | 13.1 Related Links                   |    |

|   | 8.6 Typical Characteristics            |    | 13.2 Trademarks                      | 45 |

| 9 | Detailed Description                   |    | 13.3 Electrostatic Discharge Caution | 45 |

| 9 |                                        |    | 13.4 Glossary                        | 45 |

|   | 9.1 Overview                           | 14 | Mechanical, Packaging, and Orderable |    |

|   | 9.2 Functional Block Diagram 17        |    | Information                          | 45 |

|   | 9.3 Feature Description                |    | 14.1 Package Summary                 |    |

|   |                                        |    | 14.1 I ackage duminary               | 40 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | nanges from Revision G (January 2015) to Revision H Page                                                                                                                                                                                                                                                                                            |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | Changed 20 V Maximum Input Voltage Rating Feature bullet to 22 V to match Absolute Maximum Ratings table                                                                                                                                                                                                                                            |

| Cł | nanges from Revision F (December 2014) to Revision G                                                                                                                                                                                                                                                                                                |

| •  | Deleted Lead temperature (soldering) spec from Absolute Maximum Ratings table. See Package Option Addendum 8 Changed table heading from Handling Ratings to ESD Ratings. Moved T <sub>stg</sub> spec to the Absolute Maximum Ratings table 8 Changed the test condition of IBAT- Battery discharge current in SYSOFF mode: Removed "(BAT, SW, SYS)" |

| Cł | nanges from Revision E (December 2013) to Revision F                                                                                                                                                                                                                                                                                                |

| •  | Added Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section                                                             |

| •  | Deleted the minimum spec for RILIM-SHORT and changed the typical value to 55 ohm and maximum spec to 75 ohm. 11                                                                                                                                                                                                                                     |

| •  | Changed V <sub>LDO</sub> values to (4.65, 4.85, 5.04) and added description in the second column "bq24250". Added one row                                                                                                                                                                                                                           |

Submit Documentation Feedback

Changes from Revision D (July 2013) to Revision E

Copyright © 2012–2015, Texas Instruments Incorporated

**Page**

**NSTRUMENTS**

| •  | Changed text string in the Input Over-Voltage Protection description from: "turns the battery FET, sends a single 256µs pulse is sent on the STAT and INT outputs" to "turns the battery FET, sends a single 256µs pulse on the STAT and INT outputs"                                                                                                                                                                                                                                                                          |      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added Serial Interface Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| •  | Changed Register #3 description, B1(4)(5) Name from: "USB_DET_1/EN1" to: "USB_DET_1/EN2"                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| •  | Changed Register #3 description, B0(LSB) Name from: "USB_DET_0/EN0" to: "USB_DET_0/EN1"                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| •  | Changed Register #3 description, B1(4)(5) and B0(LSB) FUNCTION entries from: "Return USB detection result or pin EN1/EN0 status –" to "Return USB detection result or pin EN2/EN1 status –"; changed 00 - DCP detected / from: "EN1=0, EN0=0" to: "EN2=0, EN1=0"; changed 01 - CDP detected / from: "EN1=0, EN0=1" to: "EN2=0, EN1=1"; changed 10 - SDP detected / from: "EN1=1, EN0=0" to: "EN2=1, EN1=0"; and changed 11 - Apple/TT or non-standard adaptor detected / from: "EN1=1, EN0=1" to: "EN2=1, EN1=1", respectively |      |

| Cł | hanges from Revision C (June 2013) to Revision D                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

| •  | Changed VDPM Pin Description regulator reference from "1.23V" to "1.2"                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| •  | Changed text string in D+/D- pin description from "will remain low" to "will remain high impedance"                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|    | Added SCL and SDA to Pin Voltage Range spec in the Absolute Maximum Ratings table                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| •  | Changed spec conditions for Output Current (Continuous), from "IN, SW, SYS, BAT" to "IN, SYS, BAT" in ABS  Max Ratings table                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| •  | Changed Figure 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| •  | Added text to NTC Monitor description for clarification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| •  | Added text to Safety Timer description for clarification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| •  | Changed Fault Condition from "Input Good" to "Input Fault & LDO Low" in Fault Conditions table                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| •  | Changed Register #2 Reset state from "1010 1100" to "xxxxx 1100"                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| •  | Changed Register #4 Reset state from "0000 0000" to "1111 1000"                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| •  | Changed Bit B7, B6, B5, B4, B3 FUNCTION description from "(default 0)" to "(default 1)"                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| •  | Changed Register #4 Footnote (1) text from "current is 500ma" to "current is external"                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| •  | Changed <b>TS_EN</b> description from "When set to a '1' the TS function is disabled" to "When set to a '0', the TS function is disabled"                                                                                                                                                                                                                                                                                                                                                                                      |      |

| •  | Added text to <b>TS_STAT</b> description for clarification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| •  | Changed Register #7, Bit B3 FUNCTION description from "if TERM is true or EN_PTM is true" to "if TERM is true or Force PTM s true"                                                                                                                                                                                                                                                                                                                                                                                             |      |

| Cł | hanges from Revision B (May 2013) to Revision C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page |

| •  | Deleted PREVIEW status note from devices bq24250YFF, bq24251YFF, bq24251RGE, and bq24253RGE                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45   |

| Cł | hanges from Revision A (March 2013) to Revision B                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

| •  | Added PREVIEW status to devices in the Ordering Information table, except the bq24250RGER and bq24250RGET                                                                                                                                                                                                                                                                                                                                                                                                                      | Γ 45 |

| Cł | hanges from Original (October 2012) to Revision A                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

| •  | Changed From: Product Brief To: Full data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1    |

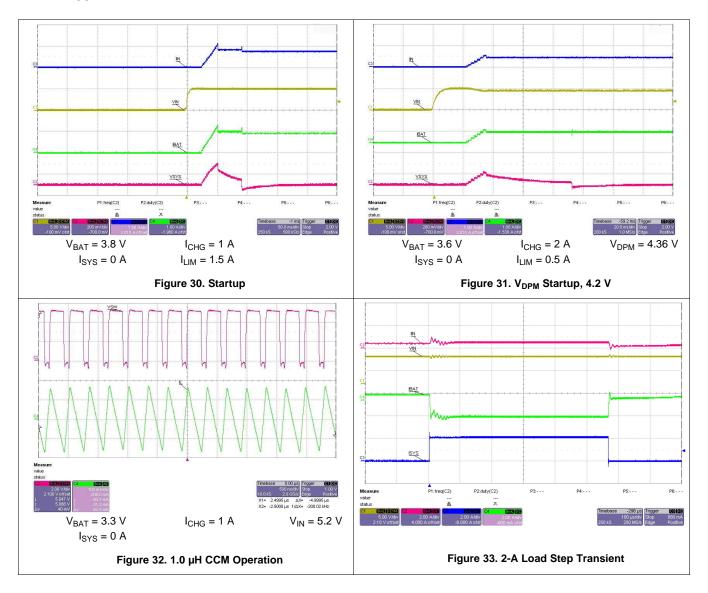

| •  | Added Typical Characteristics graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| •  | Added Typical Characteristics graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| •  | Added Typical Characteristics graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| •  | Changed Equation (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| •  | Changed text in the F/S Mode Protocol section from "to either transmit data to the slave (R/W bit 1) or receive                                                                                                                                                                                                                                                                                                                                                                                                                |      |

## bq24251: Not Recommended For New Designs

| bq24250, bq24251, bq24253         | bq24251: Not Recommended For New Designs | INSTRUMENTS |

|-----------------------------------|------------------------------------------|-------------|

| SLUSBA1H - OCTOBER 2012 - REVISED | AUGUST 2015                              | www.ti.com  |

| (R/W bit 1)" for clarification    |                                          | 32          |

## 5 Description (continued)

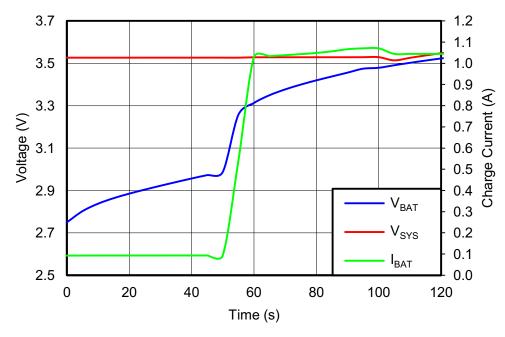

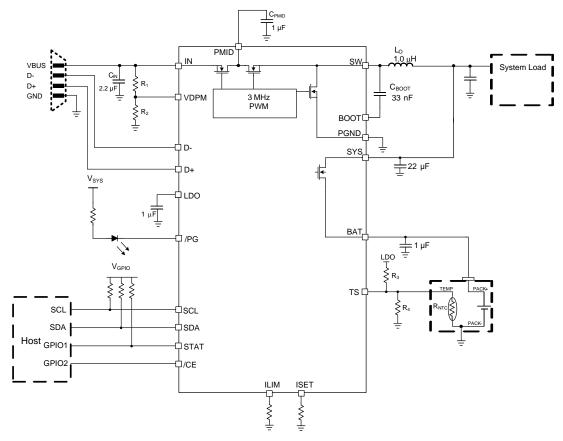

The power-path management feature allows the bq24250, bq24251, and bq24253 to power the system from a high-efficiency DC-DC converter while simultaneously and independently charging the battery. The charger monitors the battery current at all times and reduces the charge current when the system load requires current above the input current limit. This reduced charge current allows for proper charge termination and enables the system to run with a defective or absent battery pack. Additionally, this reduced charge current enables instant system turnon even with a totally discharged battery or no battery. The architecture of the power-path management also permits the battery to supplement the system current requirements when the adapter cannot deliver the peak system currents. This supplementation of current requirements enables the use of a smaller adapter.

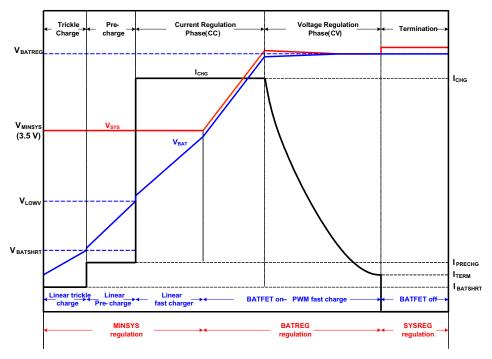

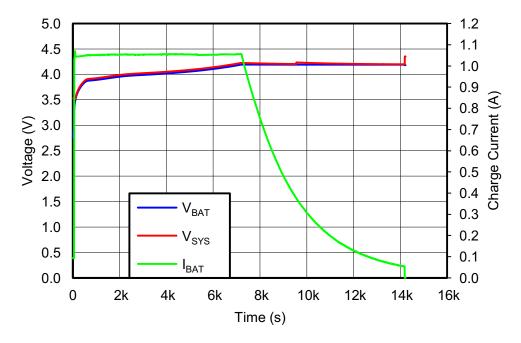

The battery is charged in four phases: trickle charge, precharge, constant current, and constant voltage. In all charge phases, an internal control loop monitors the IC junction temperature and reduces the charge current if the internal temperature threshold is exceeded. Additionally, a voltage-based, JEITA compatible battery pack thermistor monitoring input (TS) that monitors battery temperature for safe charging is included.

## **Device Options**

| DEVICE  | DEFAULT<br>OVP | D+/D- OR<br>EN1/EN2     | INT OR PG | DEFAULT<br>V <sub>OREG</sub> | MINSYS | TS PROFILE | I <sup>2</sup> C OR<br>STAND<br>ALONE | I <sup>2</sup> C<br>ADDRESS |

|---------|----------------|-------------------------|-----------|------------------------------|--------|------------|---------------------------------------|-----------------------------|

| bq24250 | 10.5V          | EN1/EN2                 | INT       | 4.2V                         | 3.5V   | JEITA      | $I^2C + SA$                           | 0x6A                        |

| bq24251 | 10.5V          | D+/D-                   | PG        | 4.2V                         | 3.5V   | JEITA      | $I^2C + SA$                           | 0x6A                        |

| bq24253 | 10.5V          | D+/D-<br>and<br>EN1/EN2 | PG        | 4.2V                         | 3.5V   | JEITA      | SA Only                               | N/A                         |

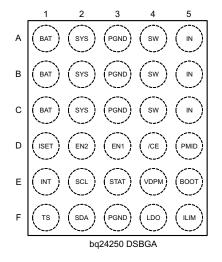

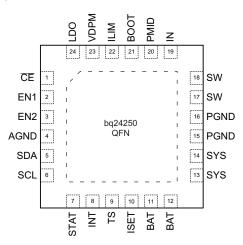

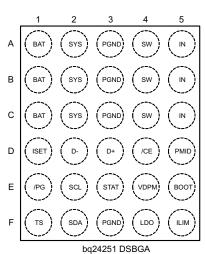

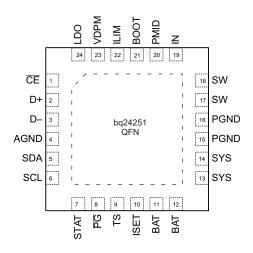

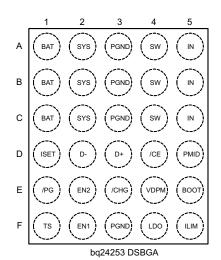

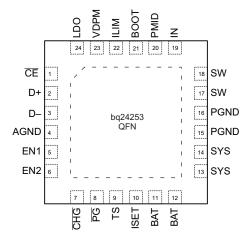

## 7 Pin Configuration and Functions

### DSBGA/QFN 30 Pins/24 Pins Top View

**NSTRUMENTS**

## **Pin Functions**

|      | PIN               |       |                   |       |                   |         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|------|-------------------|-------|-------------------|-------|-------------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | bq24              | 4250  | bq24              |       | ba24              | bq24253 |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|      | YFF               | RGE   | YFF               | RGE   | YFF               | RGE     | 1/0 | 3200 11011                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| IN   | A5,B5,C5          | 19    | A5,B5,C5          | 19    | A5,B5,C5          | 19      | ı   | Input power supply. IN is connected to the external DC supply (AC adapter or USB port). Bypass IN to PGND with >2µF ceramic capacitor                                                                                                                                                                                                                                                                                                                         |  |  |

| PMID | D5                | 20    | D5                | 20    | D5                | 20      | I   | Connection between blocking FET and high-side FET.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| sw   | A4, B4,<br>C4     | 17–18 | A4, B4,<br>C4     | 17–18 | A4, B4,<br>C4     | 17–18   | 0   | Inductor Connection. Connect to the switching side of the external inductor.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| воот | E5                | 21    | E5                | 21    | E5                | 21      | ı   | High Side MOSFET Gate Driver Supply. Connect a 0.033µF ceramic capacitor (voltage rating > 15V) from BOOT to SW to supply the gate drive for the high side MOSFETs.                                                                                                                                                                                                                                                                                           |  |  |

| PGND | A3, B3,<br>C3, F3 | 15–16 | A3, B3,<br>C3, F3 | 15–16 | A3, B3,<br>C3, F3 | 15–16   |     | Ground terminal. Connect to the ground plane of the circuit.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SYS  | A2, B2,<br>C2     | 13–14 | A2, B2,<br>C2     | 13–14 | A2, B2,<br>C2     | 13–14   | I   | System Voltage Sense and switched-mode power supply (SMPS) output filter connection. Connect SYS to the system output at the output bulk capacitors. Bypass SYS locally with >20µF.                                                                                                                                                                                                                                                                           |  |  |

| BAT  | A1, B1,<br>C1     | 11–12 | A1, B1,<br>C1     | 11–12 | A1, B1,<br>C1     | 11–12   | I/O | Battery Connection. Connect to the positive terminal of the battery. Additionally, bypass BAT with a >1µF capacitor.                                                                                                                                                                                                                                                                                                                                          |  |  |

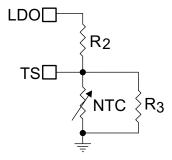

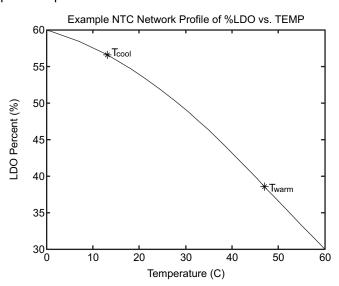

| TS   | F1                | 9     | F1                | 9     | F1                | 9       | ı   | Battery Pack NTC Monitor. Connect TS to the center tap of a resistor divider from LDO to GND. The NTC is connected from TS to GND. The TS function provides 4 thresholds for JEITA or PSE compatibility. See the <i>NTC Monitor</i> section for more details on operation and selecting the resistor values.                                                                                                                                                  |  |  |

| VDPM | E4                | 23    | E4                | 23    | E4                | 23      | I   | Input DPM Programming Input. Connect a resistor divider between IN and GND with VDPM connected to the center tap to program the Input Voltage based Dynamic Power Management threshold (V <sub>IN_DPM</sub> ). The input current is reduced to maintain the supply voltage at V <sub>IN_DPM</sub> . The reference for the regulator is 1.2V. Short pin to GND if external resistors are not desired—this sets a default of 4.68V for the input DPM threshold. |  |  |

| ISET | D1                | 10    | D1                | 10    | D1                | 10      | ı   | Charge Current Programming Input. Connect a resistor from ISET to GND to program the fast charge current. The charge current is programmable from 300mA to 2A.                                                                                                                                                                                                                                                                                                |  |  |

| ILIM | F5                | 22    | F5                | 22    | F5                | 22      | 1   | Input Current Limit Programming Input. Connect a resistor from ILIM to GND to program the input current limit for IN. The current limit is programmable from 0.5A to 2A. ILIM has no effect on the USB input. If an external resistor is not desired, short to GND for a 2A default setting.                                                                                                                                                                  |  |  |

| CE   | D4                | 1     | D4                | 1     | D4                | 1       | I   | Charge Enable Active-Low Input. Connect CE to a high logic level to place the battery charger in standby mode.                                                                                                                                                                                                                                                                                                                                                |  |  |

| EN1  | D3                | 2     | _                 | _     | F2                | 5       | I   | Input Current Limit Configuration Inputs. Use                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| EN2  | D2                | 3     | _                 | _     | E2                | 6       | I   | EN1, and EN2 to control the maximum input current and enable USB compliance. See Table 1 for programming details.                                                                                                                                                                                                                                                                                                                                             |  |  |

| CHG  | -                 | -     | -                 | _     | E3                | 7       | 0   | Charge Status Open Drain Output. CHG is pulled low when a charge cycle starts and remains low while charging. CHG is high impedance when the charging terminates and when no supply exists. CHG does not indicate recharge cycles.                                                                                                                                                                                                                            |  |  |

www.ti.com

## Pin Functions (continued)

|      |     |      | Р   | IN   |     |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-----|------|-----|------|-----|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | bq2 | 4250 | bq2 | 4251 | bq2 | 4253 | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | YFF | RGE  | YFF | RGE  | YFF | RGE  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PG   | -   | -    | E1  | 8    | E1  | 8    | 0   | Power Good Open Drain Output. $\overline{PG}$ is pulled low when a valid supply is connected to IN. A valid supply is between $V_{BAT} + V_{SLP}$ and $V_{OVP}$ . If no supply is connected or the supply is out of this range, $\overline{PG}$ is high impedance.                                                                                                                                                                                                                                                                             |

| STAT | E3  | 7    | E3  | 7    | -   | -    | 0   | Status Output. STAT is an open-drain output that signals charging status and fault interrupts. STAT pulls low during charging. STAT is high impedance when charging is complete or the charger is disabled. When a fault occurs, a 256µs pulse is sent out as an interrupt for the host. STAT is enabled/disabled using the EN_STAT bit in the control register. STAT will indicate recharge cycles. Connect STAT to a logic rail using an LED for visual indication or through a $10k\Omega$ resistor to communicate with the host processor. |

| INT  | E1  | 8    | -   | -    | -   | -    | 0   | Status Output. INT is an open-drain output that signals charging status and fault interrupts. INT pulls low during charging. INT is high impedance when charging is complete or the charger is disabled. When a fault occurs, a 256 $\mu$ s pulse is sent out as an interrupt for the host. INT will indicate recharge cycles. Connect INT to a logic rail through a $10k\Omega$ resistor to communicate with the host processor.                                                                                                              |

| SCL  | E2  | 6    | E2  | 6    | _   | _    | ı   | $\mbox{I}^2\mbox{C}$ Interface Clock. Connect SCL to the logic rail through a $10k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SDA  | F2  | 5    | F2  | 5    | _   | _    | I/O | $\mbox{I$^2$C}$ Interface Data. Connect SDA to the logic rail through a $10k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D+   | _   | -    | D3  | 2    | D3  | 2    | 1   | BC1.2 compatible D+/D- Based Adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| D-   | -   | -    | D2  | 3    | D2  | 3    | 1   | Detection. Detects DCP, SDP, and CDP. Also complies with the unconnected dead battery provision clause. D+ and D- are connected to the D+ and D− outputs of the USB port at power up. Also includes the detection of Apple <sup>™</sup> and TomTom™ adapters where a 500mA input current limit is enabled. The PG pin will remain high impedance until the detection has completed.                                                                                                                                                            |

| LDO  | F4  | 24   | F4  | 24   | F4  | 24   | 0   | LDO output. LDO is regulated to 4.9V and drives up to 50mA. Bypass LDO with a 1 $\mu$ F ceramic Capacitor. LDO is enabled when $V_{UVLO} < V_{IN}$ <18V.                                                                                                                                                                                                                                                                                                                                                                                       |

| AGND | -   | 4    | _   | 4    | _   | 4    |     | Analog Ground for QFN only. Connect to the thermal pad and the ground plane of the circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Submit Documentation Feedback

## 8 Specifications

## 8.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                       |                                                                                      | MIN  | MAX | UNIT |

|---------------------------------------|--------------------------------------------------------------------------------------|------|-----|------|

|                                       | IN                                                                                   | -0.3 | 22  | ٧    |

| Pin Voltage Range (with               | SW                                                                                   | -0.7 | 12  | V    |

|                                       | BOOT                                                                                 | -0.3 | 20  | V    |

| respect to GND)                       | LDO,STAT, INT, /CHG, /PG, EN1, EN2, EN3, /CE, D+, D-, ILIM, ISET, VDPM, TS, SCL, SDA | -0.3 | 7   | ٧    |

|                                       | SYS, BAT                                                                             | -0.3 | 5   | V    |

| BOOT relative to SW                   |                                                                                      | -0.3 | 7   | V    |

| Output Current                        | IN                                                                                   |      | 2   | ^    |

| (Continuous)                          | SYS, BAT                                                                             |      | 4   | A    |

| Output Sink Current                   | STAT, /CHG, /PG                                                                      |      | 5   | mA   |

| Operating free-air tempera            | ature range                                                                          | -40  | 85  | °C   |

| Junction temperature, T <sub>J</sub>  |                                                                                      | -40  | 125 | °C   |

| Input Power                           | IN                                                                                   |      | 15  | W    |

| Storage temperature, T <sub>stg</sub> |                                                                                      | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 8.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

All voltages are with respect to PGND if not specified. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the data book for thermal limitations and considerations of packages

|                     |                                                | MIN  | MAX               | UNIT |

|---------------------|------------------------------------------------|------|-------------------|------|

| V <sub>IN</sub>     | IN voltage range                               | 4.35 | 18 <sup>(1)</sup> | V    |

|                     | IN operating voltage range                     | 4.35 | 10.5              | V    |

| I <sub>IN</sub>     | Input current                                  |      | 2                 | Α    |

| I <sub>CHG</sub>    | Current in charge mode, BAT                    |      | 2                 | Α    |

| I <sub>DISCHG</sub> | Current in discharge mode, BAT                 |      | 4                 | Α    |

| R <sub>ISET</sub>   | Charge current programming resistor range      | 75   |                   | Ω    |

| R <sub>ILIM</sub>   | Input current limit programming resistor range | 105  |                   | Ω    |

| P <sub>IN</sub>     | Input Power                                    |      | 12                | W    |

| T <sub>J</sub>      | Operating junction temperature range           | 0    | 125               | °C   |

<sup>(1)</sup> The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the BOOT or SW pins. Small routing loops for the power nets in layout minimize switching noise.

<sup>2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

|                    | THERMAL METRIC(1)                            | YFF<br>(30 PINS) | RGE<br>(24 PINS) | UNIT |

|--------------------|----------------------------------------------|------------------|------------------|------|

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 76.5             | 32.9             | °C/W |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 0.2              | 32.8             | °C/W |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 44               | 10.6             | °C/W |

| $\Psi_{JT}$        | Junction-to-top characterization parameter   | 1.6              | 0.3              | °C/W |

| ΨЈВ                | Junction-to-board characterization parameter | 43.4             | 10.7             | °C/W |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | N/A              | 2.3              | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 8.5 Electrical Characteristics

$V_{\text{LIVLO}} < V_{\text{IN}} < V_{\text{OVP}}$  and  $V_{\text{IN}} > V_{\text{BAT}} + V_{\text{SLP}}$ ,  $T_{\text{J}} = 0^{\circ}\text{C} - 125^{\circ}\text{C}$  and  $T_{\text{J}} = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

| PARAMETER             |                                                                      | TEST CONDITIONS                                                                                                                                  | MIN                          | TYP                                                       | MAX                              | UNIT |

|-----------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------|----------------------------------|------|

| INPUT CU              | RRENTS                                                               |                                                                                                                                                  |                              |                                                           |                                  |      |

|                       |                                                                      | $V_{DPM} < V_{IN} < V_{OVP} \text{ AND } V_{IN} > V_{BAT} + V_{SLP} \text{ PWM switching,}$ CE Enable                                            |                              | 13                                                        |                                  | mA   |

| I <sub>IN</sub>       | Supply current from IN                                               | $\begin{split} &V_{DPM} < V_{IN} < V_{OVP} \text{ AND } V_{IN} > \\ &V_{BAT} + V_{SLP} \text{ PWM switching,} \\ &\text{CE Disable} \end{split}$ |                              |                                                           | 5                                | IIIA |

|                       |                                                                      | $V_{IN}$ = 5.5V, 0°C< $T_{J}$ < 85°C, High-Z Mode                                                                                                |                              | 170                                                       | 225                              | μΑ   |

|                       | Battery discharge current in high impedance mode, (BAT, SW, SYS)     | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 85^{\circ}\text{C}$ , VBAT = 4.2 V, VIN = 0V or 5V, High-Z Mode                                       |                              | 16                                                        | 22                               |      |

| I <sub>BAT</sub>      | Battery discharge current in SYSOFF mode                             | 0°C< T <sub>J</sub> < 85°C, VBAT = 4.2<br>V,<br>VIN < UVLO, SYSOFF Mode                                                                          |                              |                                                           | 1                                | μΑ   |

| POWER-P               | ATH MANAGEMENT                                                       |                                                                                                                                                  |                              |                                                           |                                  |      |

| 1                     | System Regulation Voltage                                            | MINSYS stage (no DPM or DPPM)                                                                                                                    | -1%                          | 3.52                                                      | 1%                               |      |

|                       |                                                                      | MINSYS stage (DPM or DPPM active)                                                                                                                | -1.50%                       | V <sub>MINSYS</sub><br>–200mV                             |                                  |      |

| V <sub>SYSREG</sub>   |                                                                      | BATREG stage                                                                                                                                     |                              | V <sub>BAT</sub><br>+ I <sub>CHG</sub><br>R <sub>on</sub> |                                  | V    |

|                       |                                                                      | SYSREG stage                                                                                                                                     | V <sub>BATREG</sub><br>+2.1% | V <sub>BATREG</sub><br>+3.1%                              | V <sub>BATRE</sub><br>G<br>+4.1% |      |

| $V_{SPLM}$            | Enter supplement mode voltage threshold                              | V <sub>BAT</sub> = 3.6V                                                                                                                          |                              | V <sub>BAT</sub> –<br>40mV                                |                                  | V    |

| I <sub>SPLM</sub>     | Exit supplement mode current threshold                               | V <sub>BAT</sub> = 3.6V                                                                                                                          |                              | 20                                                        |                                  | mA   |

| t <sub>DGL(SC1)</sub> | Deglitch Time, OUT Short Circuit during Discharge or Supplement Mode | Measured from (V <sub>BAT</sub> – V <sub>SYS</sub> ) = 300 mV                                                                                    |                              | 740                                                       |                                  | μs   |

| t <sub>REC(SC1)</sub> | Recovery Time, OUT Short Circuit during Discharge or Supplement Mode |                                                                                                                                                  |                              | 64                                                        |                                  | ms   |

| BATTERY               | CHARGER                                                              |                                                                                                                                                  |                              |                                                           | ,,                               |      |

| R <sub>ON(BAT-</sub>  | Internal hottom, charger MOSEET on resistance                        | Measured from BAT to SYS,<br>V <sub>BAT</sub> = 4.2V (WCSP)                                                                                      |                              | 20                                                        | 30                               | m0   |

| SYS)                  | Internal battery charger MOSFET on-resistance                        | Measured from BAT to SYS, V <sub>BAT</sub> = 4.2V (QFN)                                                                                          |                              | 30                                                        | 40                               | mΩ   |

Submit Documentation Feedback

## **Electrical Characteristics (continued)**

$V_{UVLO} < V_{IN} < V_{OVP}$  and  $V_{IN} > V_{BAT} + V_{SLP}$ ,  $T_J = 0^{\circ}C - 125^{\circ}C$  and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                              | PARAMETER                                                                        | TEST CONDITIONS                                                                          | MIN                           | TYP          | MAX   | UNIT  |

|------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------|--------------|-------|-------|

|                              | I <sup>2</sup> C host mode                                                       | Operating in voltage regulation, Programmable Range                                      | 3.5                           |              | 4.44  | V     |

| $V_{BATREG}$                 | SA mode or I <sup>2</sup> C default mode                                         |                                                                                          |                               | 4.2          |       |       |

|                              | Voltage Regulation Acquired.                                                     | T <sub>J</sub> = 25°C                                                                    | -0.5%                         |              | 0.5%  |       |

|                              | Voltage Regulation Accuracy                                                      | $T_J = 0$ °C to 125°C                                                                    | -0.75%                        |              | 0.75% |       |

| I <sub>CHG</sub>             | Fast Charge Current Range                                                        | $V_{LOWV} \le V_{BAT} < V_{BAT(REG)}$                                                    | 500                           |              | 2000  | mA    |

|                              | Fast Charge Current Accuracy                                                     | I <sup>2</sup> C mode                                                                    | -7%                           |              | 7%    |       |

| I <sub>CHG-LOW</sub>         | Low Charge Current Setting                                                       | Set via I <sup>2</sup> C                                                                 | 297                           | 330          | 363   | mA    |

| K <sub>ISET</sub>            | Programmable Fast Charge Current Factor                                          | $I_{CHG} = \frac{K_{ISET}}{R_{ISET}}$                                                    | 232.5                         | 250          | 267.5 | ΑΩ    |

| V <sub>ISET</sub>            | Maximum ISET pin voltage (in regulation)                                         |                                                                                          |                               | 0.42         |       | V     |

| R <sub>ISET</sub> -<br>SHORT | Short circuit resistance threshold                                               |                                                                                          | 45                            | 55           | 75    | Ω     |

| V                            | Pre-charge to fast charge threshold                                              | Rising                                                                                   | 2.9                           | 3            | 3.1   | V     |

| $V_{LOWV}$                   | Hysteresis for V <sub>LOWV</sub>                                                 | Battery voltage falling                                                                  |                               | 100          |       | mV    |

| I <sub>PRECHG</sub>          | Pr-charge current (V <sub>BATUVLO</sub> < V <sub>BAT</sub> < V <sub>LOWV</sub> ) | Ipre-chg is a precentile of the external fast charge settings.                           | 8                             | 10           | 12    | %     |

| t <sub>DGL(LOWV)</sub>       | Deglitch time for pre-charge to fast charge transition 32                        |                                                                                          |                               | ms           |       |       |

| $V_{BAT\_UVLO}$              | Battery Under voltage lockout threshold                                          | V <sub>BAT</sub> rising                                                                  | 2.37                          | 2.5          | 2.63  | V     |

|                              | Battery UVLO hysteresis                                                          |                                                                                          |                               | 200          |       | mV    |

| $V_{BATSHRT}$                | Trickle charge to pre-charge threshold                                           |                                                                                          | 1.9                           | 2            | 2.1   | V     |

|                              | Hysteresis for VBATSHRT                                                          | Battery voltage falling                                                                  |                               | 100          |       | mV    |

| I <sub>BATSHRT</sub>         | Trickle charge mode charge current (V <sub>BAT</sub> < V <sub>BATSHRT</sub> )    |                                                                                          | 25                            | 35           | 50    | mA    |

| $t_{\rm DGL(BATSH}$ RT)      | Deglitch time for trickle charge to pre-charge transition                        |                                                                                          |                               | 256          |       | us    |

| <b></b> .                    | Termination Current Threshold                                                    | Termination current on SA only                                                           |                               | 10           |       | %ICHG |

| ITERM                        | Termination Current Threshold Tolerance                                          |                                                                                          | -10%                          |              | 10%   |       |

| t <sub>DGL(TERM)</sub>       | Deglitch time for charge termination                                             | Both rising and falling, 2-mV over-drive, t <sub>RISE</sub> , t <sub>FALL</sub> = 100 ns |                               | 64           |       | ms    |

| $V_{RCH}$                    | Recharge threshold voltage                                                       | Below V <sub>BATREG</sub>                                                                | 70                            | 115          | 160   | mV    |

| $t_{\text{DGL(RCH)}}$        | Deglitch time                                                                    | V <sub>BAT</sub> falling below V <sub>RCH</sub> , t <sub>FALL</sub> = 100 ns             |                               | 32           |       | ms    |

| BATTERY                      | DETECTION                                                                        |                                                                                          |                               |              |       | ı     |

| $V_{BATREG\_HI}$             | Battery Detection High Regulation Voltage                                        | Same as V <sub>BATREG</sub>                                                              |                               | $V_{BATREG}$ |       | V     |

| V <sub>BATREG_L</sub><br>O   | Battery Detection Low Regulation Voltage                                         | 360 mV offset from V <sub>BATREG</sub>                                                   | V                             |              |       | V     |

| V <sub>BATDET Hi</sub>       | Battery detection comparator                                                     | V <sub>BATREG</sub> = VBATREG_HI                                                         | V <sub>BATREG</sub><br>–120mV |              | V     |       |

| V <sub>BATDET LO</sub>       | Battery detection comparator                                                     | V <sub>BATREG</sub> = V <sub>BATREG_LO</sub>                                             | V <sub>BATREG</sub><br>+120mV |              | V     |       |

| I <sub>DETECT</sub>          | Battery Detection Current Sink                                                   | Always on during battery detection                                                       | 7.5                           |              | mA    |       |

| t <sub>DETECT</sub>          | Battery detection time                                                           | For both V <sub>BATREG_HI</sub> and V <sub>BATREG_LO</sub>                               |                               | 32           |       | ms    |

| Tsafe                        | Safety Timer Accuracy                                                            |                                                                                          | -10%                          |              | +10%  |       |

## **Electrical Characteristics (continued)**

$V_{\text{UVLO}} < V_{\text{IN}} < V_{\text{OVP}}$  and  $V_{\text{IN}} > V_{\text{BAT}} + V_{\text{SLP}}$ ,  $T_{\text{J}} = 0^{\circ}\text{C} - 125^{\circ}\text{C}$  and  $T_{\text{J}} = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

|                                    | PARAMETER                                                                                       | TEST CONDITIONS                                                                                         | MIN                    | TYP                             | MAX                        | UNIT                         |

|------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------|---------------------------------|----------------------------|------------------------------|

| INPUT PRO                          | DTECTION                                                                                        |                                                                                                         |                        |                                 |                            |                              |

|                                    |                                                                                                 | I <sub>IN_LIMIT</sub> = 100 mA                                                                          | 90                     | 95                              | 100                        | mA                           |

|                                    |                                                                                                 | I <sub>IN_LIMIT</sub> = 150 mA                                                                          | 135                    | 142.5                           | 150                        |                              |

|                                    |                                                                                                 | I <sub>IN_LIMIT</sub> = 500 mA                                                                          | 450                    | 475                             | 500                        |                              |

|                                    | Land come of Parks a                                                                            | I <sub>IN_LIMIT</sub> = 900 mA                                                                          | 810                    | 860                             | 910                        |                              |

| I <sub>IN</sub>                    | Input current limiting                                                                          | I <sub>IN_LIMIT</sub> = 1500 mA                                                                         | 1400                   | 1475                            | 1550                       |                              |

|                                    |                                                                                                 | I <sub>IN_LIMIT</sub> = 2000 mA                                                                         | 1850                   | 1950                            | 2050                       |                              |

|                                    |                                                                                                 | I <sub>IN_LIMIT</sub> = External                                                                        | I <sub>LII</sub>       | $M = \frac{K_{ILIM}}{R_{ILIM}}$ |                            |                              |

| I <sub>LIM</sub>                   | Maximum input current limit programmable range for IN input                                     |                                                                                                         | 500                    |                                 | 2000                       | mA                           |

| K <sub>ILIM</sub>                  | Maximum input current factor for IN input                                                       | I <sub>LIM</sub> = 500 mA to 2.0 A                                                                      | 240                    | 270                             | 300                        | ΑΩ                           |

| V <sub>ILIM</sub>                  | Maximum ILIM pin voltage (in regulation)                                                        |                                                                                                         | 0.42                   |                                 | V                          |                              |

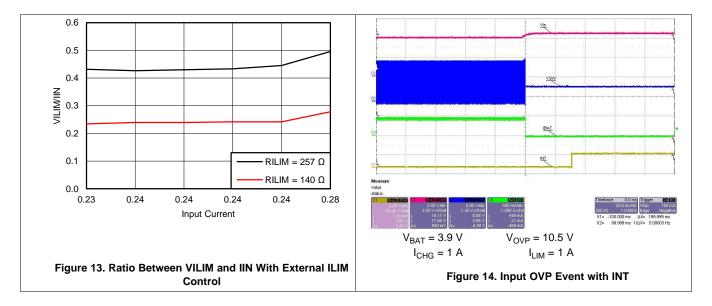

| I <sub>IN</sub> /I <sub>ILIM</sub> | Ratio between input current and the ILIM pin<br>current in external control or stand alone mode |                                                                                                         |                        | A/A                             |                            |                              |

| R <sub>ILIM</sub> -<br>SHORT       | Short circuit resistance threshold                                                              |                                                                                                         |                        | 55                              | 75                         | Ω                            |

|                                    | V threshold range                                                                               | SA mode                                                                                                 | 4.2                    |                                 | 10                         |                              |

| $V_{\text{IN\_DPM}}$               | V <sub>IN_DPM</sub> threshold range                                                             | I <sup>2</sup> C mode                                                                                   | 4.2                    |                                 | 4.76                       |                              |

|                                    | V <sub>IN_DPM</sub> threshold for USB Input in SA mode                                          | USB100, USB150, USB500,<br>USB900, current limit selected.<br>Also I <sup>2</sup> C register default.   | 4.27                   | 4.36                            | 4.45                       | V                            |

|                                    | V <sub>IN_DPM</sub> threshold with adaptor current limit and VDPM shorted to GND                | Must set to external resistor settings via the EN1/EN2 pins or the I <sup>2</sup> C register interface. | $V_{IN\_DPM}$          |                                 | V <sub>IN_DPM</sub><br>+2% |                              |

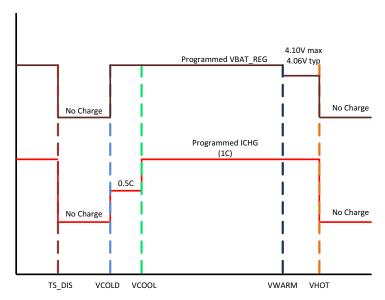

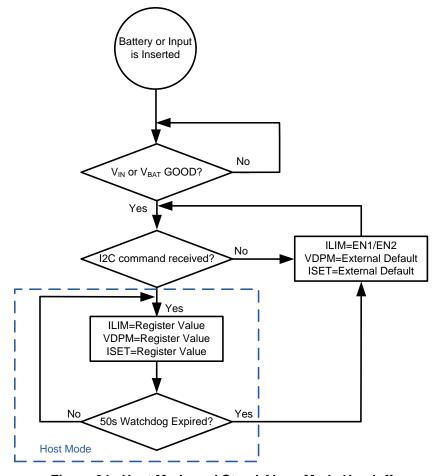

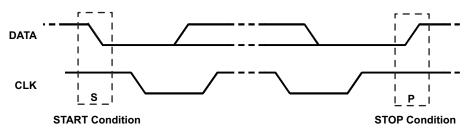

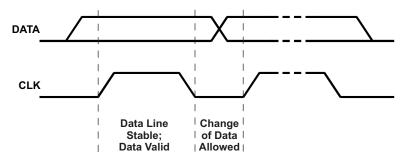

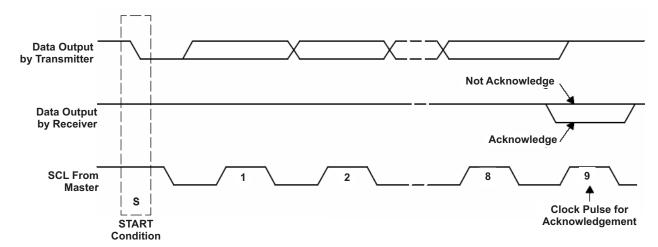

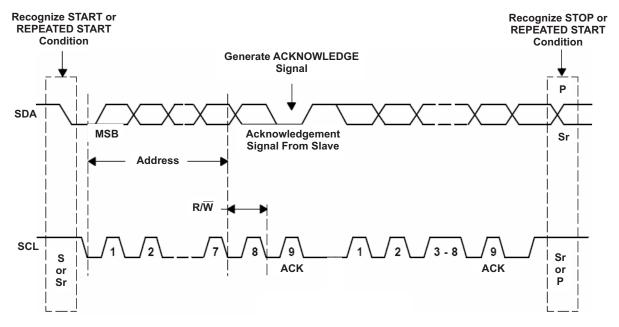

|                                    | V <sub>IN DPM</sub> threshold Accuracy                                                          | Both I <sup>2</sup> C and SA mode                                                                       | -2%<br>-2%             |                                 | 2%                         |                              |