# ANALOG DEVICES

# 3.0 V to 5.5 V, ±12 kV IEC ESD Protected, 50 Mbps RS-485 Transceiver

### Data Sheet

### FEATURES

TIA/EIA RS-485 compliant over full supply range 3.0 V to 5.5 V operating voltage range on  $V_{cc}$ ESD protection on the bus pins IEC 61000-4-2  $\geq$  ±12 kV contact discharge IEC 61000-4-2  $\geq \pm 12$  kV air discharge HBM  $\geq \pm 30 \text{ kV}$ Full hot swap support (glitch free power-up/power-down) High speed 50 Mbps data rate Full receiver short circuit, open circuit, and bus idle failsafe Extended temperature range up to 125°C Profibus compliant at  $V_{CC} \ge 4.5 V$ Half-duplex Allows connection of up to 128 nodes onto the bus Space-saving package options 8-lead 3 mm × 3 mm MSOP package 8-lead narrow body SOIC\_N package

### APPLICATIONS

Industrial fieldbuses Process control Building automation Profibus networks Motor control servo drives and encoders

### **GENERAL DESCRIPTION**

The ADM3065E is a 3.0 V to 5.5 V, IEC electrostatic discharge (ESD) protected RS-485 transceiver, allowing the device to withstand  $\pm 12$  kV contact discharges on the transceiver bus pins without latch-up or damage.

The ADM3065E is suitable for high speed 50 Mbps bidirectional data communication on multipoint bus transmission lines. The ADM3065E has a ¼ unit load input impedance, which allows up to 128 transceivers on a bus.

The ADM3065E is a half-duplex RS-485 transceiver, fully compliant to the Profibus<sup>\*</sup> standard with increased 2.1 V bus differential voltage at  $V_{CC} \ge 4.5$  V.

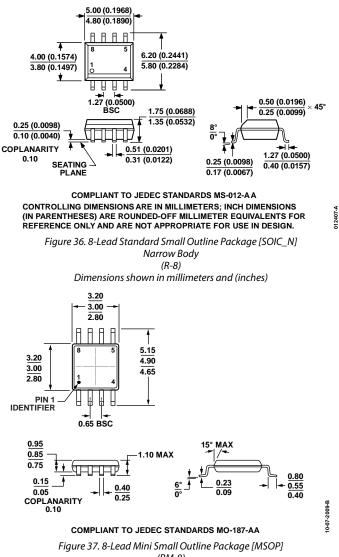

This RS-485 transceiver is available in two space-saving packages: the 8-lead 3 mm  $\times$  3 mm MSOP package and the 8-lead narrow body SOIC package.

# ADM3065E

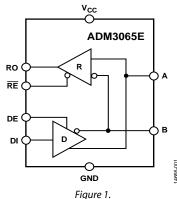

### FUNCTIONAL BLOCK DIAGRAM

Table 1. Summary of the ADM3065E Half-Duplex Operating Conditions—Data Rate Capability Across Temperature, Power Supply, and Package

| Maximum<br>Data Rate<br>(Mbps) <sup>1</sup> | Maximum<br>V <sub>cc</sub> (V) | Maximum<br>Temperature | Package Description              |

|---------------------------------------------|--------------------------------|------------------------|----------------------------------|

| 50                                          | 5.5                            | –40°C to<br>+105℃      | 8-Lead SOIC_N and 8-Lead<br>MSOP |

| 50                                          | 3.6                            | –40℃ to<br>+125℃       | 8-Lead SOIC_N and 8-Lead<br>MSOP |

<sup>1</sup> The ADM3065E data input (DI) is transmitting 50 Mbps clock data, and the ADM3065E driver enable (DE) is enabled for 50% of the DI transmit time.

Models with operating temperature ranges of  $-40^{\circ}$ C to  $+125^{\circ}$ C and  $-40^{\circ}$ C to  $+85^{\circ}$ C are available.

Excessive power dissipation caused by bus contention or by output shorting is prevented by a thermal shutdown circuit. If, during fault conditions, a significant temperature increase is detected in the internal driver circuitry, this feature forces the driver output into a high impedance state.

The ADM3065E guarantees a logic high receiver output when the receiver inputs are shorted, open, or connected to a terminated transmission line with all drivers disabled.

Table 1 presents an overview of the ADM3065E data rate capability across temperature and power supply in 8-lead SOIC\_N and 8-lead MSOP packages. Refer to the Ordering Guide for model numbering.

Rev. 0

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram1                    |

| General Description 1                        |

| Revision History 2                           |

| Specifications                               |

| Timing Specifications 4                      |

| Timing Diagrams                              |

| Absolute Maximum Ratings                     |

| Thermal Resistance                           |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions7 |

| Test Circuits                                |

| Typical Performance Characteristics          |

### **REVISION HISTORY**

3/2017—Revision 0: Initial Version

| 12 |

|----|

| 12 |

| 12 |

| 12 |

| 13 |

| 13 |

| 13 |

| 13 |

| 13 |

| 14 |

| 15 |

| 17 |

| 17 |

|    |

# SPECIFICATIONS

$V_{CC}$  = 3.0 V to 5.5 V,  $T_A$  =  $T_{MIN}$  (-40°C) to  $T_{MAX}$  (+125°C), unless otherwise noted. All typical specifications are at  $T_A$  = 25°C,  $V_{CC}$  = 3.3 V unless otherwise noted.

| Table 2.                                               |                          |                      |      |                      |      |                                                                                                                               |

|--------------------------------------------------------|--------------------------|----------------------|------|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              | Symbol                   | Min                  | Тур  | Max                  | Unit | Test Conditions/Comments                                                                                                      |

| POWER SUPPLY                                           |                          |                      |      |                      |      |                                                                                                                               |

| Supply Current                                         | lcc                      |                      | 2    | 7.5                  | mA   | No load, $DE = V_{CC}$ , $\overline{RE} = 0 V$                                                                                |

|                                                        |                          |                      |      | 7.5                  | mA   | No load, $DE = V_{CC}$ , $\overline{RE} = V_{CC}$                                                                             |

|                                                        |                          |                      |      | 4.5                  | mA   | No load, $DE = 0 V$ , $\overline{RE} = 0 V$                                                                                   |

|                                                        |                          |                      |      | 172                  | mA   | 50 Mbps, $R_L = 54 \Omega$ , $DE = V_{CC}$ , $\overline{RE} = 0 V$                                                            |

|                                                        |                          |                      | 67   | 75                   | mA   | 50 Mbps, $R_L = 54 \Omega$ , $DE = V_{CC}$ , $\overline{RE} = 0 V (V_{CC} = 3.0 V)$                                           |

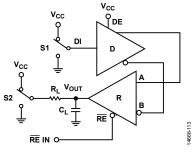

| Supply Current in Shutdown Mode                        | <b>I</b> <sub>SHDN</sub> |                      |      | 450                  | μA   | $DE = 0 V, \overline{RE} = V_{CC}$                                                                                            |

| DRIVER                                                 |                          |                      |      |                      |      |                                                                                                                               |

| Differential Outputs                                   |                          |                      |      |                      |      |                                                                                                                               |

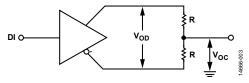

| Output Voltage, Loaded                                 | V <sub>OD2</sub>         | 2.0                  |      | Vcc                  | V    | $V_{CC} \ge 3.0 \text{ V}, \text{ R} = 50 \Omega$ , see Figure 7                                                              |

|                                                        | V <sub>OD2</sub>         | 1.5                  |      | Vcc                  | V    | $V_{CC} \ge 3.0$ V, R = 27 $\Omega$ (RS-485), see Figure 7                                                                    |

|                                                        | V <sub>OD2</sub>         | 2.1                  |      | Vcc                  |      | $V_{CC} \ge 4.5 \text{ V}, \text{ R} = 50 \Omega$ , see Figure 7                                                              |

|                                                        | VOD2                     | 2.1                  |      | Vcc                  | V    | $V_{CC} \ge 4.5 \text{ V}, \text{R} = 27 \Omega \text{ (RS-485), see Figure 7}$                                               |

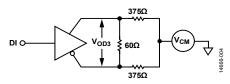

|                                                        | V <sub>OD3</sub>         | 1.5                  |      | Vcc                  | V    | $V_{CC} \ge 3.0 \text{ V}, -7 \text{ V} \le V_{CM} \le +12 \text{ V}$ , see Figure 8                                          |

|                                                        | V <sub>OD3</sub>         | 2.1                  |      | Vcc                  | V    | $V_{CC} \ge 4.5 \text{ V}, -7 \text{ V} \le V_{CM} \le +12 \text{ V}, \text{ see Figure 8}$                                   |

| Δ V <sub>OD</sub>   for Complementary Output<br>States | $\Delta  V_{OD} $        |                      |      | 0.2                  | V    | R = 27 $\Omega$ or 50 $\Omega$ , see Figure 7                                                                                 |

| Common-Mode Output Voltage                             | Voc                      |                      |      | 3.0                  | v    | R = 27 Ω or 50 Ω, see Figure 7                                                                                                |

| Δ V <sub>oc</sub>   for Complementary Output<br>States | Δ V <sub>oc</sub>        |                      |      | 0.2                  | V    | R = 27 $\Omega$ or 50 $\Omega$ , see Figure 7                                                                                 |

| Output Short-Circuit Current                           | los                      | -250                 |      | 250                  | mA   | $-7 V < V_{OUT} < +12 V$                                                                                                      |

| Logic Inputs (DE, RE, DI)                              |                          |                      |      |                      |      |                                                                                                                               |

| Input Voltage                                          |                          |                      |      |                      |      |                                                                                                                               |

| Low                                                    | VIL                      |                      |      | $0.33 \times V_{CC}$ | v    | DE, $\overline{\text{RE}}$ , DI, 3.0 V $\leq$ V <sub>CC</sub> $\leq$ 5.5 V                                                    |

| High                                                   | VIH                      | $0.67 \times V_{CC}$ |      |                      | v    | DE, $\overline{\text{RE}}$ , DI, 3.0 V $\leq$ V <sub>CC</sub> $\leq$ 5.5 V                                                    |

| Input Current                                          | lı -                     | -2                   |      | +2                   | μA   | DE, $\overline{\text{RE}}$ , DI, 3.0 V $\leq$ V <sub>CC</sub> $\leq$ 5.5 V, 0 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub> |

| RECEIVER                                               |                          |                      |      |                      |      |                                                                                                                               |

| Differential Inputs                                    |                          |                      |      |                      |      |                                                                                                                               |

| Differential Input Threshold Voltage                   | VTH                      | -200                 | -125 | -30                  | mV   | $-7 V < V_{CM} < +12 V$                                                                                                       |

| Input Voltage Hysteresis                               | V <sub>HYS</sub>         |                      | 30   |                      | mV   | $-7 V < V_{CM} < +12 V$                                                                                                       |

| Input Current (A, B)                                   | h                        |                      |      | 0.25                 | mA   | $DE = 0 V$ , $V_{CC} = powered/unpowered$ , $V_{IN} = 12 V$                                                                   |

|                                                        |                          | -0.20                |      |                      | mA   | $DE = 0 V$ , $V_{CC} = powered/unpowered$ , $V_{IN} = -7 V$                                                                   |

| Line Input Resistance                                  | R <sub>IN</sub>          | 48                   |      |                      | kΩ   | $-7 \text{ V} \le \text{V}_{\text{TST}} \le +12 \text{ V}$                                                                    |

| Logic Outputs                                          |                          |                      |      |                      |      |                                                                                                                               |

| Output Voltage                                         |                          |                      |      |                      |      |                                                                                                                               |

| Low                                                    | Vol                      |                      |      | 0.4                  | V    | $I_{OUT} = +2 \text{ mA}, V_{ID} \leq -0.2 \text{ V}$                                                                         |

| High                                                   | V <sub>OH</sub>          | 2.4                  |      |                      | V    | $I_{OUT} = -2 \text{ mA}, V_{ID} \ge +0.2 \text{ V}$                                                                          |

| Short-Circuit Current                                  |                          |                      |      | 85                   | mA   | $V_{OUT} = GND \text{ or } V_{CC}$                                                                                            |

| Three-State Output Leakage                             | I <sub>OZR</sub>         |                      |      | ±2                   | μA   | $RO = 0 V \text{ or } V_{CC}$                                                                                                 |

### TIMING SPECIFICATIONS

$V_{CC}$  = 3.0 V to 5.5 V,  $T_A$  =  $T_{MIN}$  (-40°C) to  $T_{MAX}$  (+125°C), unless otherwise noted. All typical specifications are at  $T_A$  = 25°C,  $V_{CC}$  = 3.3 V, unless otherwise noted.

| Parameter                         | Symbol                                | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                                  |

|-----------------------------------|---------------------------------------|-----|-----|------|------|-----------------------------------------------------------------------------------------------------------|

| DRIVER                            |                                       |     |     |      |      |                                                                                                           |

| Maximum Data Rate <sup>1</sup>    |                                       | 50  |     |      | Mbps |                                                                                                           |

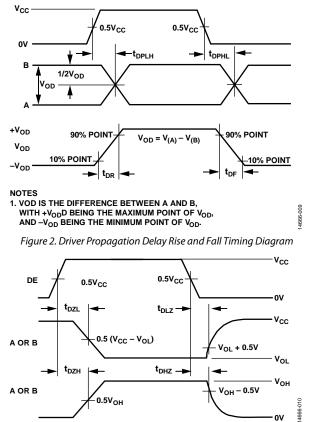

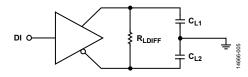

| Propagation Delay                 | t <sub>DPLH</sub> , t <sub>DPHL</sub> |     | 9   | 15   | ns   | $R_{LDIFF} = 54 \Omega$ , $C_{L1} = C_{L2} = 100 \text{ pF}$ , see Figure 9                               |

| Skew                              | t <sub>DSKEW</sub>                    |     | 1   | 2    | ns   | $R_{LDIFF} = 54 \Omega$ , $C_{L1} = C_{L2} = 100 \text{ pF}$ , see Figure 9                               |

| Rise/Fall Times                   | t <sub>DR</sub> , t <sub>DF</sub>     |     | 4   | 6.7  | ns   | $R_{LDIFF} = 54 \Omega$ , $C_{L1} = C_{L2} = 100 \text{ pF}$ , see Figure 9                               |

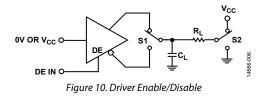

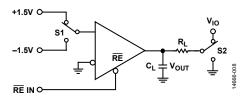

| Enable to Output High             | t <sub>DZH</sub>                      |     | 10  | 30   | ns   | $R_L = 110 \Omega$ , $C_L = 50 pF$ , see Figure 10                                                        |

| Enable to Output Low              | t <sub>DZL</sub>                      |     | 10  | 30   | ns   | $R_L = 110 \Omega$ , $C_L = 50 pF$ , see Figure 10                                                        |

| Disable Time from Low             | t <sub>DLZ</sub>                      |     | 10  | 30   | ns   | $R_L = 110 \Omega$ , $C_L = 50 pF$ , see Figure 10                                                        |

| Disable Time from High            | t <sub>DHZ</sub>                      |     | 10  | 30   | ns   | $R_L = 110 \Omega$ , $C_L = 50 pF$ , see Figure 10                                                        |

| Enable Time from Shutdown to High | t <sub>DZH(SHDN)</sub>                |     |     | 2000 | ns   | $R_L = 110 \Omega$ , $C_L = 50 pF$ , see Figure 10                                                        |

| Enable Time from Shutdown to Low  | t <sub>DZL(SHDN)</sub>                |     |     | 2000 | ns   | $R_L = 110 \Omega$ , $C_L = 50 pF$ , see Figure 10                                                        |

| RECEIVER                          |                                       |     |     |      |      |                                                                                                           |

| Maximum Data Rate                 |                                       | 50  |     |      | Mbps |                                                                                                           |

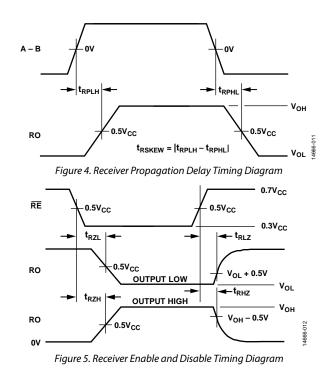

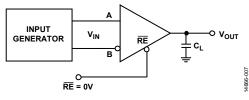

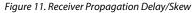

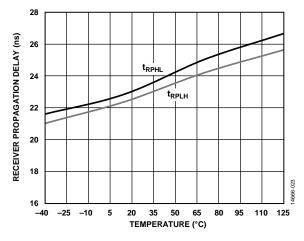

| Propagation Delay                 | t <sub>RPLH</sub> , t <sub>RPHL</sub> |     |     | 35   | ns   | $C_{L} = 15 \text{ pF},  V_{1D}  \ge 1.5 \text{ V}, \text{ see Figure 11}$                                |

| Skew/Pulse Width Distortion       | t <sub>RSKEW</sub>                    |     |     | 3    | ns   | $C_L = 15 \text{ pF},  V_{ID}  \ge 1.5 \text{ V}, V_{CM} = 1.5 \text{ V}, \text{ see Figure 11}$          |

| Enable to Output High             | t <sub>rzh</sub>                      |     | 10  | 35   | ns   | $R_L$ = 1 kΩ, $C_L$ = 15 pF, $ V_{ID} $ ≥ 1.5 V, DE high, see Figure 13                                   |

| Enable to Output Low              | t <sub>RZL</sub>                      |     | 10  | 35   | ns   | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , $ V_{ID}  \ge 1.5 \text{ V}$ , DE high, see Figure 13 |

| Disable Time from Low             | t <sub>RLZ</sub>                      |     | 10  | 35   | ns   | $R_L = 1 \text{ k}\Omega, C_L = 15 \text{ pF},  V_{ID}  \ge 1.5 \text{ V}, \text{ see Figure 13}$         |

| Disable Time from High            | t <sub>RHZ</sub>                      |     | 10  | 35   | ns   | $R_L = 1 \text{ k}\Omega, C_L = 15 \text{ pF},  V_{ID}  \ge 1.5 \text{ V}, \text{ see Figure 13}$         |

| Enable from Shutdown to High      | t <sub>RZH(SHDN)</sub>                |     |     | 2000 | ns   | $R_L = 1 \text{ k}\Omega, C_L = 15 \text{ pF},  V_{ID}  \ge 1.5 \text{ V}, \text{ see Figure 12}$         |

| Enable from Shutdown to Low       | t <sub>RZL(SHDN)</sub>                |     |     | 2000 | ns   | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , $ V_{ID}  \ge 1.5 \text{ V}$ , see Figure 12          |

| TIME TO SHUTDOWN                  | t <sub>shdn</sub>                     | 40  |     |      | ns   |                                                                                                           |

$^1$  Maximum data rate assumes a ratio of  $t_{\text{DR}}{:}t_{\text{BIT}}{:}t_{\text{DF}}$  equal to 1:1:1.

### **TIMING DIAGRAMS**

Figure 3. Driver Enable and Disable Timing Diagram

oν

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Table 4.                                          |                       |

|---------------------------------------------------|-----------------------|

| Parameter                                         | Rating                |

| V <sub>cc</sub> to GND                            | 6 V                   |

| Digital Input/Output Voltage (DE, RE, DI, and RO) | -0.3 V to Vcc + 0.3 V |

| Driver Output/Receiver Input Voltage              | -9 V to +14 V         |

| Operating Temperature Range                       | -40°C to +125°C       |

| Storage Temperature Range                         | –65°C to + 150°C      |

| Continuous Total Power Dissipation                |                       |

| 8-Lead SOIC_N                                     | 0.225 W               |

| 8-Lead MSOP                                       | 0.151 W               |

| Maximum Junction Temperature                      | 150°C                 |

| Lead Temperature                                  |                       |

| Soldering (10 Sec)                                | 300°C                 |

| Vapor Phase (60 Sec)                              | 215°C                 |

| Infrared (15 Sec)                                 | 220°C                 |

| ESD on the Bus Pins (A and B)                     |                       |

| IEC 61000-4-2 Contact Discharge                   | ±12 kV                |

| IEC 61000-4-2 Air Discharge                       |                       |

| Ten Positive and Ten Negative                     | ±12 kV                |

| Discharges                                        |                       |

| Three Positive or Negative                        | ±15 kV                |

| Discharges                                        |                       |

| ESD Human Body Model (HBM)                        |                       |

| On the Bus Pins (A and B)                         | >±30 kV               |

| All Other Pins                                    | ±8 kV                 |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered on a circuit board for surface-mount packages.

#### Table 5. Thermal Resistance

| Package Type  | θ」Α    | οıc   | Unit |

|---------------|--------|-------|------|

| 8-Lead SOIC_N | 110.88 | 58.63 | °C/W |

| 8-Lead MSOP   | 165.69 | 49.61 | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 6. ADM3065E 8-Lead Narrow Body SOIC\_N and 8-Lead MSOP

| Table 6. Pin I | Table 6. Pin Function Descriptions |                                                                                                                                                                                                               |  |  |  |  |

|----------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Number     | Mnemonic                           | Description                                                                                                                                                                                                   |  |  |  |  |

| 1              | RO                                 | Receiver Output Data. This output is high when $(A - B) > -30 \text{ mV}$ and low when $(A - B) < -200 \text{ mV}$ . This output is tristated when the receiver is disabled, that is, when RE is driven high. |  |  |  |  |

| 2              | RE                                 | Receiver Enable Input. This is an active low input. Driving this input low enables the receiver, and driving it<br>high disables the receiver.                                                                |  |  |  |  |

| 3              | DE                                 | Driver Output Enable. A logic high level on this pin enables the driver differential outputs, A and B. A logic<br>low level places the driver output into a high impedance state.                             |  |  |  |  |

| 4              | DI                                 | Transmit Data Input. Data to be transmitted by the driver is applied to this input.                                                                                                                           |  |  |  |  |

| 5              | GND                                | Ground.                                                                                                                                                                                                       |  |  |  |  |

| 6              | А                                  | Noninverting Driver Output/Receiver Input. When the driver is disabled, or when V <sub>CC</sub> is powered down, Pin A is put into a high impedance state to avoid overloading the bus.                       |  |  |  |  |

| 7              | В                                  | Inverting Driver Output/Receiver Input. When the driver is disabled, or when V <sub>CC</sub> is powered down, Pin B is put into a high impedance state to avoid overloading the bus.                          |  |  |  |  |

| 8              | V <sub>cc</sub>                    | 3.0 V to 5.5 V Power Supply. It is recommended adding a 0.1 $\mu$ F decoupling capacitor between Pin V <sub>cc</sub> and Pin GND.                                                                             |  |  |  |  |

### Table 6. Pin Function Descriptions

# ADM3065E

### **TEST CIRCUITS**

Figure 7. Driver Voltage Measurements

Figure 8. Driver Voltage Measurements over Common-Mode Range

Figure 9. Driver Propagation Delay

Figure 12. Receiver Enable/Disable from Shutdown

Figure 13. Receiver Enable/Disable

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 14. Shutdown Current (I<sub>SHDN</sub>) vs. Temperature

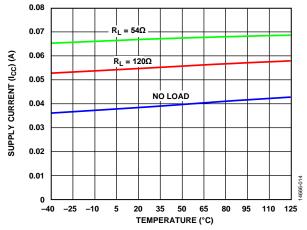

Figure 15. Supply Current ( $I_{CC}$ ) vs. Temperature, Data Rate = 50 Mbps,  $V_{CC}$  = 3.3 V

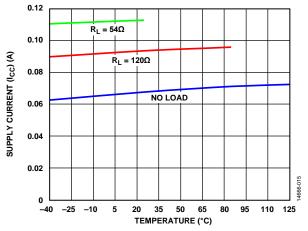

Figure 16. Supply Current ( $I_{CC}$ ) vs. Temperature, Data Rate = 50 Mbps,  $V_{CC}$  = 5.0 V

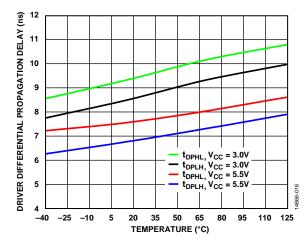

Figure 17. Driver Differential Propagation Delay vs. Temperature, 50 Mbps

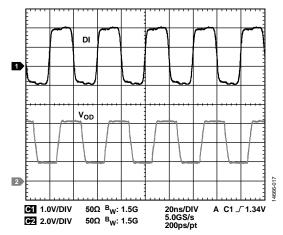

Figure 18. Driver Propagation Delay at 50 Mbps

### ADM3065E

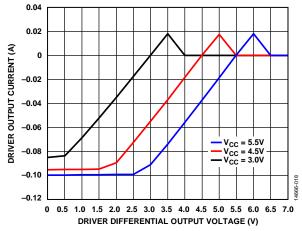

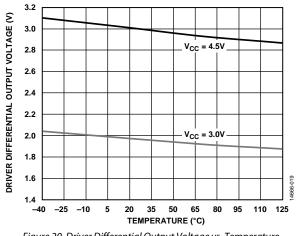

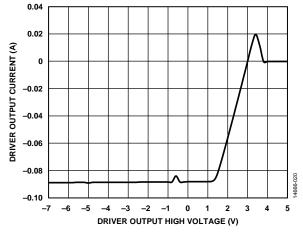

Figure 21. Driver Output Current vs. Driver Output High Voltage

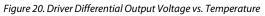

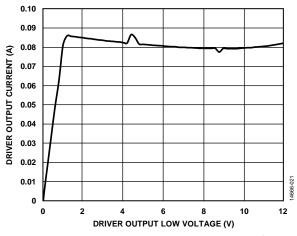

Figure 22. Driver Output Current vs. Driver Output Low Voltage

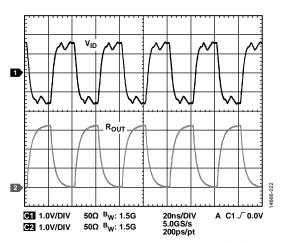

Figure 23. Receiver Propagation Delay at 50 Mbps,  $|V_{ID}| \ge 1.5 V$

# Data Sheet

# ADM3065E

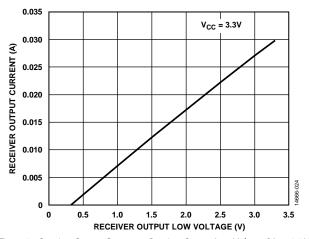

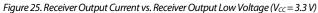

Figure 26. Receiver Output Current vs. Receiver Output High Voltage ( $V_{CC} = 3.3 V$ )

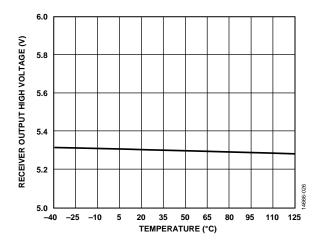

Figure 27. Receiver Output High Voltage vs. Temperature

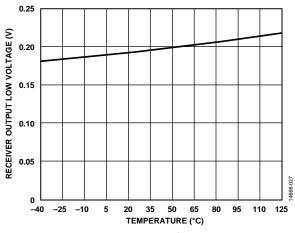

Figure 28. Receiver Output Low Voltage vs. Temperature

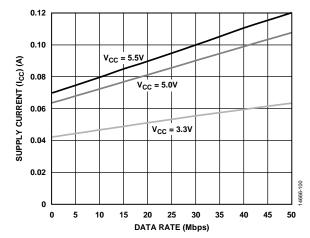

Figure 29. Supply Current (I<sub>CC</sub>) vs. Data Rate with 54  $\Omega$  Load Resistance

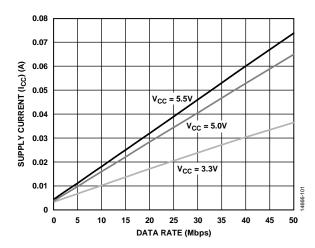

Figure 30. Supply Current (I<sub>CC</sub>) vs. Data Rate with No Load Resistance

### THEORY OF OPERATION HIGH SPEED IEC ESD PROTECTED RS-485

The ADM3065E is a 3.0 V to 5.5 V, 50 Mbps RS-485 transceiver with IEC 61000-4-2 Level 4 ESD protection on the bus pins. Tthe ADM3065E can withstand up to  $\pm 12$  kV contact discharge on transceiver bus pins (A and B) without latch-up or damage.

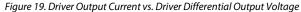

### HIGH DRIVER DIFFERENTIAL OUTPUT VOLTAGE

The ADM3065E has characteristics optimized for use in Profibus applications. When powered at  $V_{CC} \ge 4.5$  V, the ADM3065E driver output differential voltage meets or exceeds the Profibus requirements of 2.1 V with a 54  $\Omega$  load.

### IEC 61000-4-2 ESD PROTECTION

ESD is the sudden transfer of electrostatic charge between bodies at different potentials caused by near contact or induced by an electric field. It has the characteristics of high current in a short time period. The primary purpose of the IEC 61000-4-2 test is to determine the immunity of systems to external ESD events outside the system during operation. IEC 61000-4-2 describes testing using two coupling methods: contact discharge and air discharge. Contact discharge implies a direct contact between the discharge gun and the equipment under test (EUT). During air discharge testing, the charged electrode of the discharge gun is moved toward the EUT until a discharge occurs as an arc across the air gap. The discharge gun does not make direct contact with the EUT. A number of factors affect the results and repeatability of the air discharge test, including humidity, temperature, barometric pressure, distance, and rate of approach to the EUT. This method is a better representation of an actual ESD event but is not as repeatable. Therefore, contact discharge is the preferred test method.

During testing, the data port is subjected to at least 10 positive and 10 negative single discharges. Selection of the test voltage is dependent on the system end environment.

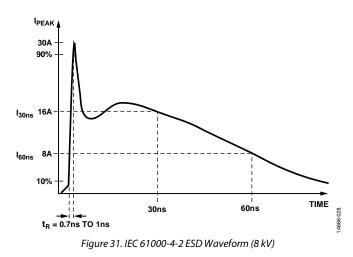

Figure 31 shows the 8 kV contact discharge current waveform as described in the IEC 61000-4-2 specification. Some of the key waveform parameters are rise times of less than 1 ns and pulse widths of approximately 60 ns.

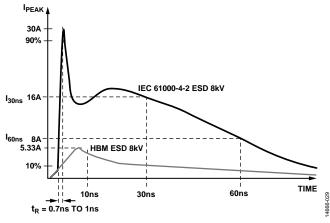

Figure 32 shows the 8 kV contact discharge current waveform from the IEC 61000-4-2 standard compared to the human body model (HBM) ESD 8 kV waveform. Figure 32 shows that the two standards specify a very different waveform shape and peak current. The peak current associated with a IEC 61000-4-2 8 kV pulse is 30 A, whereas the corresponding peak current for HBM ESD is more than five times less, at 5.33 A. The other difference is the rise time of the initial voltage spike, with the IEC 61000-4-2 ESD waveform having a much faster rise time of 1 ns, compared to the 10 ns associated with the HBM ESD waveform. The amount of power associated with an IEC ESD waveform is much greater than that of a HBM ESD waveform. The HBM ESD standard requires the EUT to be subjected to 3 positive and 3 negative discharges, while in comparison the IEC ESD Standard requires 10 positive and 10 negative discharge tests.

The ADM3065E with IEC 61000-4-2 ESD ratings is better suited for operation in harsh environments compared to other RS-485 transceivers that state varying levels of HBM ESD protection.

Figure 32. IEC 61000-4-2 ESD Waveform 8 kV Compared to HBM ESD Waveform 8 kV

### **TRUTH TABLES**

|                     | Inputs <sup>1</sup> |   | Transmitting Outputs |        |        |

|---------------------|---------------------|---|----------------------|--------|--------|

| Supply Status (Vcc) | RE DE               |   | DI                   | Α      | В      |

| On                  | Х                   | 1 | 1                    | 1      | 0      |

| On                  | Х                   | 1 | 0                    | 0      | 1      |

| On                  | 0                   | 0 | Х                    | High-Z | High-Z |

| On                  | 1                   | 0 | Х                    | High-Z | High-Z |

| Off                 | Х                   | Х | Х                    | High-Z | High-Z |

<sup>1</sup> X means don't care.

<sup>2</sup> High-Z means high impedance.

#### Table 8. Receiving Truth Table

| Supply                    | Inputs <sup>1</sup>      | Outputs |    |                     |

|---------------------------|--------------------------|---------|----|---------------------|

| Status (V <sub>cc</sub> ) | A – B                    | RE      | DE | (RO) <sup>2,3</sup> |

| On                        | >-0.03 V                 | 0       | Х  | 1                   |

| On                        | <-0.2 V                  | 0       | Х  | 0                   |

| On                        | -0.2 V < A - B < -0.03 V | 0       | Х  | I                   |

| On                        | Inputs open/shorted      | 0       | Х  | 1                   |

| On                        | Х                        | 1       | Х  | High-Z              |

| Off                       | Х                        | х       | Х  | High-Z              |

<sup>1</sup> X means don't care.

<sup>2</sup> I means indeterminate.

<sup>3</sup> High-Z means high impedance.

### **RECEIVER FAIL-SAFE**

The ADM3065E guarantees a logic high receiver output when the receiver inputs are shorted, open, or connected to a terminated transmission line with all drivers disabled; set the receiver input threshold between -30 mV and -200 mV. If the differential receiver input voltage (A – B) is greater than or equal to -30 mV, the RO pin is logic high.

If the A – B input is less than or equal to -200 mV, RO is logic low. In the case of a terminated bus with all transmitters disabled, the receiver differential input voltage is pulled to 0 V by the termination, resulting in a logic high with a 30 mV minimum noise margin.

#### HOT SWAP CAPABILITY

#### **Hot Swap Inputs**

When a circuit board is inserted into a powered (or hot) backplane, differential disturbances to the data bus can lead to data errors. During this period, processor logic output drivers are high impedance and are unable to drive the DE and  $\overline{\text{RE}}$  inputs of the RS-485 transceivers to a defined logic level. Leakage currents up to ±10 µA from the high impedance state of the processor logic drivers can cause standard CMOS enable inputs of a transceiver to drift to an incorrect logic level. Additionally, parasitic circuit board capacitance can cause coupling of V<sub>CC</sub> or GND to the enable inputs. Without the hot swap capability, these factors can improperly enable the driver or receiver of the transceiver. When V<sub>CC</sub> rises, an internal pull-down circuit holds DE low and  $\overline{\text{RE}}$  high. After the initial power-up sequence, the pull-down circuit becomes transparent resetting the hot swap tolerable input.

### **128 TRANSCEIVERS ON THE BUS**

The standard RS-485 receiver input impedance is 12 k $\Omega$  (1 unit load), and the standard driver can drive up to 32 unit loads. The ADM3065E of transceivers has a ¼ unit load receiver input impedance (48 k $\Omega$ ), allowing up to 128 transceivers to be connected in parallel on one communication line. Any combination of these devices and other RS-485 transceivers with a total of 32 unit loads or fewer can be connected to the line.

### **DRIVER OUTPUT PROTECTION**

The ADM3065E features two methods to prevent excessive output current and power dissipation caused by faults or by bus contention. Current limit protection on the output stage provides immediate protection against short circuits over the whole common-mode voltage range. In addition, a thermal shutdown circuit forces the driver outputs into a high impedance state if the die temperature rises excessively. This circuitry is designed to disable the driver outputs when a die temperature of 150°C is reached. As the device cools, the drivers are reenabled at a temperature of 140°C.

14666-030

# **APPLICATIONS INFORMATION**

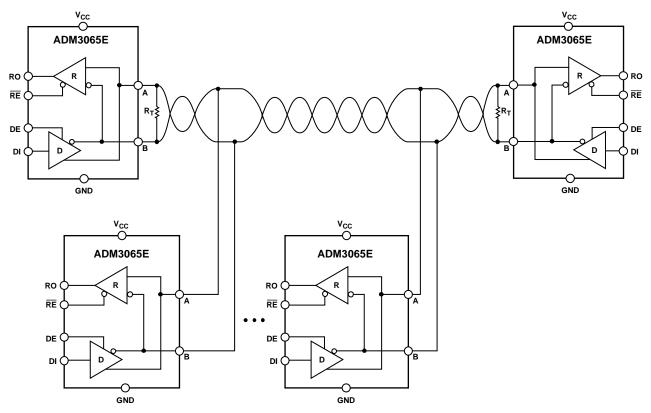

The ADM3065E transceiver is designed for bidirectional data communications on multipoint bus transmission lines. Figure 33 shows a typical network applications circuit.

To minimize reflections, terminate the line at both ends with a termination resistor (the value of the termination resistor must be equal to the characteristic impedance of the cable used) and keep stub lengths off the main line as short as possible.

NOTES

1. THE MAXIMUM NUMBER OF NODES IS 128. 2.  $R_{\rm T}$  IS EQUAL TO THE CHARACTERISTIC IMPEDANCE OF THE CABLE USED.

Figure 33. ADM3065E Typical Half-Duplex RS-485 Communications Network

### **ISOLATED HIGH SPEED RS-485 NODE**

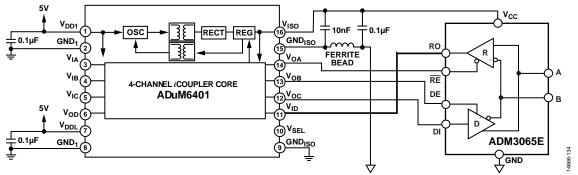

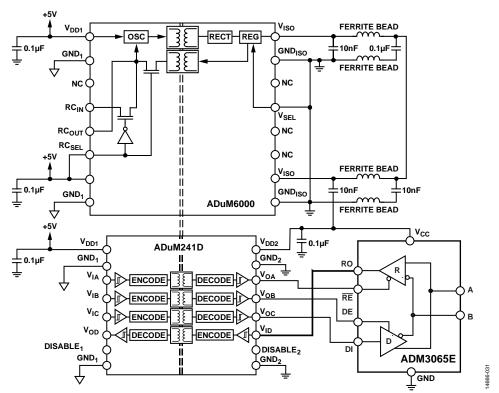

Galvanic isolation, with reinforced insulation and 5 kV rms transient withstand voltage, can be added to the ADM3065E using Analog Devices, Inc., *i*Coupler<sup>®</sup> and *iso*Power<sup>®</sup> technology. The ADuM6401 provides the required four channels of 5 kV rms signal isolation, operating at rates up to 25 Mbps, together with an integrated dc-to-dc converter. The ADuM6401 combines with the ADM3065E, shown in Figure 35, with the V<sub>ISO</sub> pin configured for 3.3 V by connecting the V<sub>SEL</sub> pin to GND<sub>ISO</sub> and a 5 V supply connected to V<sub>DD1</sub>. Operation at 3.3 V ensures the ADM3065E remains within the load capability of ADuM6401 even at 25 Mbps.

Operation at 50 Mbps data rates with isolation of the ADM3065E can be implemented using the ADuM241D quadchannel digital isolator and the ADuM6000 isolated dc-to-dc converter, as shown in Figure 34. The ADuM241D can operate at a data rate of up to 150 Mbps, offering the precise timing required to fully support the ADM3065E at 50 Mbps. Operation of ADM3065E at 3.3 V allows operation at the 50 Mbps data rate.

If 5 V operation is desired, V<sub>SEL</sub> on ADuM6000 can be tied to V<sub>ISO</sub>, and the maximum supported data rate becomes lower (for example, <10 Mbps). Refer to the Typical Performance Characteristics section, ADuM241D data sheet, and the ADuM6000 data sheet.

The dc-to-dc converters in the ADuM6401 and ADuM6000 *iso*Power devices provide regulated, isolated power to the ADM3065E (and the ADuM241D). These *iso*Power devices use high frequency switching elements to transfer power through their transformers. Take care during printed circuit board (PCB) layout to meet emissions standards. See the AN-0971 Application Note for PCB layout recommendations.

Figure 34. Signal and Power Isolated 50 Mbps RS-485 Solution (Simplified Diagram—All Connections Not Shown)

Figure 35. Signal and Power Isolated 25 Mbps RS-485 Solution (Simplified Diagram—All Connections Not Shown)

# **OUTLINE DIMENSIONS**

(RM-8) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                            | Package Option |

|--------------------|-------------------|------------------------------------------------|----------------|

| ADM3065EARZ        | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3065EARZ-R7     | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3065EBRZ        | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3065EBRZ-R7     | -40°C to +125°C   | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3065EARMZ       | -40°C to +85°C    | 8-Lead Mini Small Outline Package [MSOP]       | RM-8           |

| ADM3065EARMZ-R7    | -40°C to +85°C    | 8-Lead Mini Small Outline Package [MSOP]       | RM-8           |

| ADM3065EBRMZ       | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]       | RM-8           |

| ADM3065EBRMZ-R7    | -40°C to +125°C   | 8-Lead Mini Small Outline Package [MSOP]       | RM-8           |

| EVAL-ADM3065EEBZ   |                   | 8-Lead SOIC Evaluation Board                   |                |

| EVAL-ADM3065EEB1Z  |                   | 8-Lead MSOP Evaluation Board                   |                |

<sup>1</sup> Z = RoHS Compliant Part.

©2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D14666-0-3/17(0)

www.analog.com

Rev. 0 | Page 17 of 17