The MAX8505 step-down regulator operates from a 2.6V to 5.5V input and generates an adjustable output voltage from 0.8V to 0.85 × VIN at up to 3A. With a 2.6V to 5.5V bias supply, the input voltage can be as low as 2.25V.

The MAX8505 integrates power MOSFETs and operates at 1MHz/500kHz switching frequency to provide a compact design. Current-mode pulse-widthmodulated (PWM) control simplifies compensation with ceramic or polymer output capacitors and provides excellent transient response.

The MAX8505 features 1% accurate output over load, line, and temperature variations. Adjustable soft-start is achieved with an external capacitor. During the soft-start period, the voltage-regulation loop is active. This limits the voltage dip when the active devices, such as microprocessors or ASICs connected to the MAX8505's output, apply a sudden load current step upon passing their undervoltage thresholds.

The MAX8505 features current-limit, short-circuit, and thermal-overload protection and enables a rugged design. Open-drain power-OK (POK) monitors the output voltage.

> µP/ASIC/DSP/FPGA Core and I/O Supplies **Chipset Supplies** Server, RAID, and Storage Systems Network and Telecom Equipment

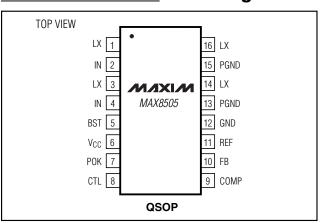

#### Pin Configuration

Applications

# M/IXI/M

Maxim Integrated Products 1

POWER-OK POK GND

**Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX8505EEE | -40°C to +85°C | 16 QSOP     |

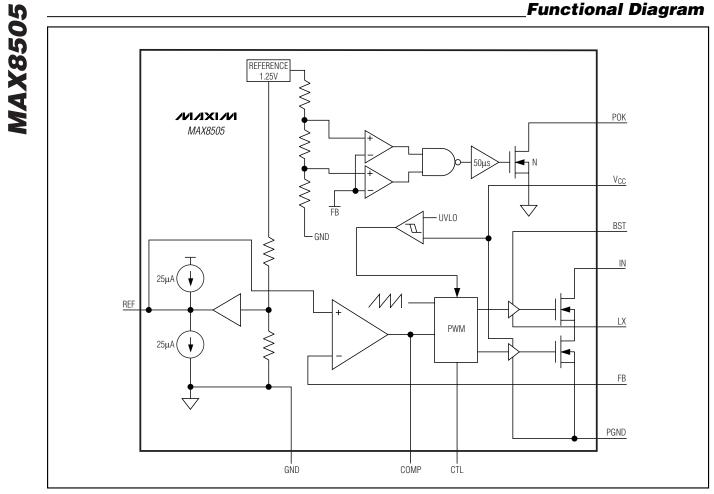

Functional Diagram appears at end of data sheet.

Saves Space—4.9mm x 6mm Footprint, 1µH

Inductor, 47µF Ceramic Output Capacitor

±1% Output Accuracy Over Load, Line, and

In-Regulation Soft-Start Limits Output-Voltage

Down to 2.25V with Bias Supply

♦ 0.8V to 0.85 × V<sub>IN</sub>, 3A Output

Fast Transient Response

POK Monitors Output Voltage

Adjustable Soft-Start

**Dips at Power-On**

Ceramic or Polymer Capacitors

Input Voltage Range

2.6V to 5.5V

Temperature

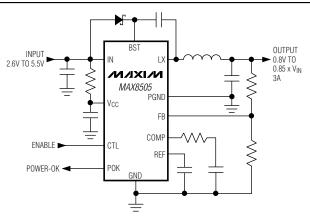

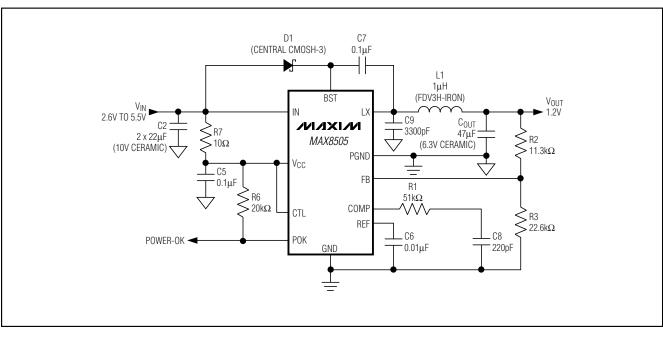

# Typical Operating Circuit

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| CTL, FB, IN, V <sub>CC</sub> to GND         | 0.3V to +6V      |

|---------------------------------------------|------------------|

| COMP, REF, POK to GND                       |                  |

| BST to LX                                   | -0.3V to +6V     |

| PGND to GND                                 |                  |

| Continuous Power Dissipation ( $T_A = +T_A$ |                  |

| 16-Pin QSOP (derate 12.5mW/°C ab            | ove +70°C)1000mW |

Operating Temperature Range

| MAX8505EEE                   | 40°C to +85°C  |

|------------------------------|----------------|

| Storage Temperature Range    | 65°C to +150°C |

| Junction Temperature         | +150°C         |

| Lead Temperature (soldering, | 10s)+300°C     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{CC} = V_{CTL} = +3.3V, V_{FB} = 0.8V, V_{COMP} = 1.25V, C_{REF} = 0.01\mu$ F, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted.)

| PARAMETER                                   | SYMBOL          | CONDITIONS                                                                  |                                | MIN   | ТҮР   | MAX   | UNITS |

|---------------------------------------------|-----------------|-----------------------------------------------------------------------------|--------------------------------|-------|-------|-------|-------|

| IN AND V <sub>CC</sub>                      |                 |                                                                             |                                |       |       |       |       |

| IN Voltage Range                            | V <sub>IN</sub> |                                                                             |                                | 2.25  |       | VCC   | V     |

| V <sub>CC</sub> Voltage Range               | V <sub>CC</sub> |                                                                             |                                | 2.6   |       | 5.5   | V     |

| IN Supply Current                           | lu i            | Switching with no load                                                      | $V_{IN} = 3.3V$                |       | 6     | 10    | m۸    |

| IN Supply Current                           | lin             |                                                                             | $V_{IN} = 5.5V$                |       | 10    |       | mA    |

| V <sub>CC</sub> Supply Current              | lcc             | Switching with no load                                                      | $V_{CC} = 3.3V$                |       | 3     | 10    | mA    |

| VCC Supply Current                          | ICC             | Switching with no load                                                      | $V_{CC} = 5.5V$                |       | 6     |       | ША    |

| Total Shutdown Current into IN and $V_{CC}$ | ISHDN           | $V_{IN} = V_{CC} = V_{BST} - V_{LX} = V_{LX} = 0$                           | = 5.5V, V <sub>CTL</sub> = 0V, |       | 20    | 50    | μA    |

| V <sub>CC</sub> Undervoltage Lockout        |                 | When LX starts/stops                                                        | V <sub>CC</sub> rising         |       | 2.40  | 2.55  | - V   |

| Threshold                                   | UVLOth          | switching                                                                   | V <sub>CC</sub> falling        | 2.2   | 2.35  |       |       |

| REF                                         |                 | ·                                                                           |                                |       |       |       |       |

| REF Voltage                                 | VREF            | $I_{REF} = 0\mu A$ , $V_{IN} = V_{CC} = 2.6V$ to 5.5V                       |                                | 0.792 | 0.800 | 0.808 | V     |

| REF Shutdown Resistance                     |                 | From REF to GND, V <sub>CTL</sub> = 0V                                      |                                |       | 13    | 100   | Ω     |

| REF Soft-Start Current                      |                 | $V_{REF} = 0.4 V$                                                           |                                | 20    | 25    | 30    | μA    |

| Soft-Start Ramp Time                        |                 | Output from 0% to 100%, $C_{REF} = 0.01 \mu F$ to $1\mu F$                  |                                |       | 32    |       | ms/µF |

| FB                                          | •               |                                                                             |                                | •     |       |       | •     |

| FB Regulation Voltage                       |                 | $V_{IN} = 2.6V$ to 5.5V                                                     |                                | 0.792 | 0.800 | 0.808 | V     |

| FB Input Bias Current                       |                 | $V_{FB} = 0.7V$                                                             |                                |       | 0.01  | 0.1   | μA    |

| Maximum Output Current                      | IOUT_MAX        | $V_{IN} = V_{CC} = 3.3V, V_{OUT} = 1.2V,$<br>L = 1µH/5.9m $\Omega$ (Note 1) |                                | 3     |       |       | А     |

|                                             |                 |                                                                             | FB high                        | 10.5  | 12    | 13.5  | 0/    |

| FB Threshold for POK Transition             |                 | FB rising or falling                                                        | FB low                         | -13.5 | -12   | -10.5 | %     |

| FB to POK Delay                             |                 | FB rising or falling                                                        |                                |       | 50    |       | μs    |

| СОМР                                        |                 |                                                                             |                                |       |       |       |       |

| COMP Transconductance                       |                 | From FB to COMP                                                             |                                | 60    | 100   | 160   | μS    |

| Gain from FB to COMP                        |                 | V <sub>COMP</sub> = 1.25V to 1.75V                                          |                                |       | 80    |       | dB    |

**MAX8505**

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = V_{CTL} = +3.3V, V_{FB} = 0.8V, V_{COMP} = 1.25V, C_{REF} = 0.01 \mu F, \textbf{T_A} = 0^{\circ} \textbf{C} \text{ to } +\textbf{85}^{\circ} \textbf{C}, \text{ unless otherwise noted.})$

| PARAMETER                        | SYMBOL | CONDITI                                                                      | ONS                                | MIN   | ТҮР   | MAX   | UNITS  |  |

|----------------------------------|--------|------------------------------------------------------------------------------|------------------------------------|-------|-------|-------|--------|--|

| COMP Clamp Voltage, Low          |        | V <sub>IN</sub> = V <sub>CC</sub> = 2.6V, 3.3V, 5.5V, V <sub>FB</sub> = 0.9V |                                    | 0.45  | 0.75  | 1.00  | V      |  |

| COMP Clamp Voltage, High         |        | V <sub>IN</sub> = V <sub>CC</sub> = 2.6V, 3.3V, 5                            | 5.5V, V <sub>FB</sub> = 0.7V       | 1.7   | 1.9   | 2.1   | V      |  |

| COMP Shutdown Resistance         |        | From COMP to GND, VC-                                                        | rL = 0V                            |       | 13    | 100   | Ω      |  |

| LX (All LX Outputs Connected Tog | ether) |                                                                              |                                    |       |       |       |        |  |

| LV On Desistance Llink           |        | $V_{\rm IN} = V_{\rm BST} - V_{\rm LX} = 3.3 V$                              |                                    |       | 38    | 74    |        |  |

| LX On-Resistance, High           |        | $V_{IN} = V_{BST} - V_{LX} = 2.6V$                                           |                                    |       | 42    |       | mΩ     |  |

| LV On Desistance Law             |        | $V_{\rm IN} = V_{\rm BST} - V_{\rm LX} = 3.3V$                               | $V_{IN} = V_{BST} - V_{LX} = 3.3V$ |       | 38    | 74    |        |  |

| LX On-Resistance, Low            |        | $V_{IN} = V_{BST} - V_{LX} = 2.6V$                                           |                                    |       | 42    |       | mΩ     |  |

| LX Current-Sense Transresistance | RT     | From LX to COMP                                                              |                                    | 0.068 | 0.086 | 0.104 | Ω      |  |

| LV Ourrent Limit Threadeald      |        | Sourcing, Typical Applica                                                    | ation Circuit                      | 4.6   | 5.6   | 6.6   | ٨      |  |

| LX Current-Limit Threshold       |        | Sinking, $V_{IN} = V_{CC} = 2.6$                                             | √ to 5.5V                          | -4.3  | -2.6  | -1.0  | A      |  |

|                                  |        | $V_{IN} = V_{CC} = 5.5V,$                                                    | LX = 5.5V                          |       |       | 100   |        |  |

| LX Leakage Current               |        | $V_{CTL} = 0$                                                                | LX = 0V                            | -100  |       |       | μA     |  |

| LV Quitching Fragmanau           |        | $V_{IN} = V_{CC} = 2.6V, 3.3V,$                                              | $CTL = V_{CC}$                     | 0.85  | 1     | 1.15  | NAL I- |  |

| LX Switching Frequency           |        | 5.5V                                                                         | $CTL = 2/3V_{CC}$                  | 0.44  | 0.5   | 0.56  | MHz    |  |

| LX Minimum Off-Time              |        | $V_{IN} = V_{CC} = 2.6V, 3.3V, 5$                                            | 5.5V                               | 95    | 110   | 135   | ns     |  |

| LX Movimum Duty Cyclo            |        | V <sub>IN</sub> = V <sub>CC</sub> = 2.6V, 3.3V,<br>5.5V                      | 500kHz                             | 90    | 94    |       | %      |  |

| LX Maximum Duty Cycle            |        |                                                                              | 1MHz                               | 84    | 89    |       | 70     |  |

| LX Minimum Duty Cycle            |        | $V_{IN} = V_{CC} = 2.6V, 3.3V,$                                              | 500kHz                             |       | 5     | 8     | 0/     |  |

|                                  |        | 5.5V                                                                         | 1MHz                               |       | 10    | 15    | %      |  |

| SLOPE COMPENSATION               |        |                                                                              |                                    |       |       |       |        |  |

| Slope Compensation               |        | Extrapolated to 100% duty cycle                                              |                                    | 245   | 300   | 400   | mV     |  |

| BST                              |        |                                                                              |                                    |       |       |       |        |  |

|                                  |        |                                                                              | $V_{LX} = 5.5V$                    |       |       | 10    |        |  |

| BST Shutdown Supply Current      |        | $(V_{BST} - V_{LX}) = V_{IN} =$<br>$V_{CC} = 5.5V, V_{CTL} = 0$              | $V_{LX} = 0V$                      |       |       | 10    | μA     |  |

|                                  |        | $V_{CC} = 0.5V, V_{CTL} = 0$                                                 | LX open                            |       |       | 10    |        |  |

| CTL                              | •      | 1                                                                            | 1                                  |       |       |       |        |  |

|                                  |        |                                                                              | For 1MHz                           | 80    |       |       | % of   |  |

| CTL Input Threshold              |        | $V_{IN} = V_{CC} = 2.6V,$<br>3.3V, 5.5V                                      | For 500kHz                         | 55    |       | 70    | VCC    |  |

|                                  |        |                                                                              | For shutdown                       |       |       | 45    | .00    |  |

| CTL Input Current                |        | $V_{CTL}$ = 0V or 5.5V, $V_{IN}$ =                                           | $V_{CC} = 5.5V$                    | -1    |       | +1    | μΑ     |  |

| POK (Power-OK)                   | •      | 1                                                                            |                                    | -     |       |       |        |  |

| POK Output Voltage, Low          |        | $V_{FB} = 0.6V \text{ or } 1.0V, I_{POK}$                                    | = 2mA                              |       | 25    | 100   | mV     |  |

| POK Leakage Current              |        | V <sub>POK</sub> = 5.5V                                                      |                                    |       | 0.001 | 1     | μΑ     |  |

| POK Fault Delay Time             |        | From FB to POK, any threshold                                                |                                    | 25    | 50    | 100   | μs     |  |

| THERMAL SHUTDOWN                 |        |                                                                              |                                    |       |       |       |        |  |

| Thermal-Shutdown Threshold       |        | When LX stops switching                                                      | T <sub>J</sub> rising              |       | +170  |       | °C     |  |

| Thermal-Shutdown Hysteresis      |        |                                                                              |                                    |       | 20    |       | °C     |  |

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{CC} = V_{CTL} = +3.3V, V_{FB} = 0.8V, V_{COMP} = 1.25V, C_{REF} = 0.01\mu$ F, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                                     | SYMBOL             | CONDITI                                                                     | SNS                                               | MIN   | TYP | MAX   | UNITS |  |

|---------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------|---------------------------------------------------|-------|-----|-------|-------|--|

| IN AND V <sub>CC</sub>                                        | •                  |                                                                             |                                                   |       |     |       |       |  |

| IN Voltage Range                                              | VIN                |                                                                             |                                                   | 2.25  |     | VCC   | V     |  |

| V <sub>CC</sub> Voltage Range                                 |                    |                                                                             |                                                   | 2.6   |     | 5.5   | V     |  |

| IN Supply Current                                             | I <sub>IN</sub>    | Switching with no load                                                      | $V_{IN} = 3.3V$                                   |       |     | 10    | mA    |  |

| V <sub>CC</sub> Supply Current                                | ICC                | Switching with no load                                                      | $V_{CC} = 3.3V$                                   |       |     | 10    | mA    |  |

| Total Shutdown Current into IN and $\mathrm{V}_{\mathrm{CC}}$ | ISHDN              | $V_{IN} = V_{CC} = V_{BST} - V_{LX} = V_{LX} = 0$                           | = 5.5V, V <sub>CTL</sub> = 0V,                    |       |     | 50    | μA    |  |

| V <sub>CC</sub> Undervoltage Lockout<br>Threshold             | UVLO <sub>th</sub> | When LX starts/stops switching                                              | V <sub>CC</sub> rising<br>V <sub>CC</sub> falling | 2.2   |     | 2.55  | V     |  |

| REF                                                           |                    |                                                                             |                                                   |       |     |       |       |  |

| REF Voltage                                                   | VREF               | $I_{REF} = 0\mu A$ , $V_{IN} = V_{CC} =$                                    | 2.6V to 5.5V                                      | 0.791 |     | 0.808 | V     |  |

| REF Shutdown Resistance                                       |                    | From REF to GND, VCTL                                                       | = 0V                                              |       |     | 100   | Ω     |  |

| REF Soft-Start Current                                        |                    | $V_{REF} = 0.4 V$                                                           |                                                   | 20    |     | 30    | μΑ    |  |

| FB                                                            |                    |                                                                             |                                                   |       |     |       |       |  |

| FB Regulation Voltage                                         | V <sub>FB</sub>    | $V_{IN} = 2.6V$ to 5.5V                                                     |                                                   | 0.791 |     | 0.808 | V     |  |

| FB Input Bias Current                                         |                    | $V_{FB} = 0.7V$                                                             |                                                   |       |     | 0.1   | μA    |  |

| Maximum Output Current                                        | IOUT_MAX           | $V_{IN} = V_{CC} = 3.3V, V_{OUT} = 1.2V,$<br>L = 1µH/5.9m $\Omega$ (Note 1) |                                                   | 3     |     |       | А     |  |

|                                                               |                    |                                                                             | FB high                                           | 10.5  |     | 13.5  | 0/    |  |

| FB Threshold for POK Transition                               |                    | FB rising or falling FB low                                                 |                                                   | -13.5 |     | -10.5 | %     |  |

| СОМР                                                          |                    |                                                                             |                                                   |       |     |       |       |  |

| COMP Transconductance                                         |                    | From FB to COMP                                                             |                                                   | 60    |     | 160   | μS    |  |

| COMP Clamp Voltage, Low                                       |                    | $V_{IN} = V_{CC} = 2.6V, 3.3V, 5$                                           | 5.5V, V <sub>FB</sub> = 0.9V                      | 0.45  |     | 1.00  | V     |  |

| COMP Clamp Voltage, High                                      |                    | $V_{IN} = V_{CC} = 2.6V, 3.3V, 5$                                           | 5.5V, V <sub>FB</sub> = 0.7V                      | 1.7   |     | 2.1   | V     |  |

| COMP Shutdown Resistance                                      |                    | From COMP to GND, VC-                                                       | TL = 0V                                           |       |     | 100   | Ω     |  |

| LX (All LX Outputs Connected Tog                              | jether)            |                                                                             |                                                   |       |     |       |       |  |

| LX On-Resistance, High                                        |                    | $V_{IN} = V_{BST} - V_{LX} = 3.3V$                                          |                                                   |       |     | 74    | mΩ    |  |

| LX On-Resistance, Low                                         |                    | $V_{IN} = V_{BST} - V_{LX} = 3.3V$                                          |                                                   |       |     | 74    | mΩ    |  |

| LX Current-Sense Transresistance                              | RT                 | From LX to COMP                                                             |                                                   | 0.068 |     | 0.104 | Ω     |  |

| LX Current-Limit Threshold                                    |                    | Sourcing, Typical Application Circuit                                       |                                                   | 4.6   |     | 5.6   | ^     |  |

|                                                               |                    | Sinking, $V_{IN} = V_{CC} = 2.6V$ to 5.5V                                   |                                                   | -4.3  |     | -1.0  | A     |  |

|                                                               |                    | $V_{IN} = V_{CC} = 5.5V,$ LX = 5.5V                                         |                                                   |       |     | 100   |       |  |

| LX Leakage Current                                            |                    | $V_{CTL} = 0$                                                               | LX = 0V                                           | -100  |     |       | μA    |  |

| LV Switching From Strong                                      |                    | $V_{\rm IN} = V_{\rm CC} = 2.6 V,$                                          | $CTL = V_{CC}$                                    | 0.85  |     | 1.15  | MALL- |  |

| LX Switching Frequency                                        |                    | 3.3V, 5.5V $CTL = 2/3 \times V_{CC}$                                        |                                                   | 0.44  |     | 0.56  | MHz   |  |

| LX Minimum Off-Time                                           |                    | V <sub>IN</sub> = V <sub>CC</sub> = 2.6V, 3.3V, 5                           | 5.5V                                              | 95    |     | 135   | ns    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = V_{CTL} = +3.3V, V_{FB} = 0.8V, V_{COMP} = 1.25V, C_{REF} = 0.01\mu$ F, **T<sub>A</sub> = -40°C to +85°C**, unless otherwise noted.) (Note 2)

| PARAMETER                   | SYMBOL | CONDITIONS                                                     |                  | MIN | ТҮР | MAX | UNITS       |

|-----------------------------|--------|----------------------------------------------------------------|------------------|-----|-----|-----|-------------|

| LY Maximum Duty Cycle       |        | $V_{IN} = V_{CC} = 2.6V, 3.3V,$                                | 500kHz           | 90  |     |     | %           |

| LX Maximum Duty Cycle       |        | 5.5V                                                           | 1MHz             | 84  |     |     |             |

| LX Minimum Duty Cycle       |        | $V_{IN} = V_{CC} = 2.6V, 3.3V,$                                | 500kHz           |     |     | 8   | %           |

| EX Minimum Duty Cycle       |        | 5.5V                                                           | 1MHz             |     |     | 15  | 70          |

| SLOPE COMPENSATION          |        |                                                                |                  |     |     |     |             |

| Slope Compensation          |        | Extrapolated to 100% dut                                       | y cycle          | 245 |     | 406 | mV          |

| BST                         |        |                                                                |                  |     |     |     |             |

|                             |        |                                                                | $V_{LX} = 5.5V$  |     |     | 10  | μΑ          |

| BST Shutdown Supply Current |        | $  (V_{BST} - V_{LX}) = V_{IN} =  V_{CC} = 5.5V, V_{CTL} = 0 $ | $V_{LX} = 0V$    |     |     | 10  |             |

|                             |        |                                                                | LX open          |     |     | 10  |             |

| CTL                         | -      | -                                                              | •                |     |     |     |             |

|                             |        | $V_{IN} = V_{CC} = 2.6V,$<br>3.3V, 5.5V                        | For 1MHz         | 80  |     |     | % of<br>Vcc |

| CTL Input Threshold         |        |                                                                | For 500kHz       | 55  |     | 70  |             |

|                             |        | 0.07, 0.07                                                     | For shutdown     |     |     | 45  | •00         |

| CTL Input Current           |        | $V_{CTL} = 0V \text{ or } 5.5V, V_{IN} = 7$                    | $V_{CC} = 5.5 V$ | -1  |     | +1  | μA          |

| POK (Power-OK)              |        |                                                                |                  |     |     |     |             |

| POK Output Voltage, Low     |        | $V_{FB} = 0.6V \text{ or } 1.0V, I_{POK} = 2mA$                |                  |     |     | 100 | mV          |

| POK Leakage Current         |        | V <sub>POK</sub> = 5.5V                                        |                  |     |     | 1   | μΑ          |

| POK Fault Delay Time        |        | From FB to POK, any threshold                                  |                  | 25  |     | 100 | μs          |

Note 1: Under normal operating conditions, COMP moves between 1.25V and 2.15V as the duty cycle changes from 10% to 90% and peak inductor current changes from 0 to 3A. Maximum output current is related to peak inductor current, inductor value input voltage, and output voltage by the following equations:

$$I_{OUT\_MAX} = \frac{I_{LIM} - (1-D) \times t_S \times V_{OUT} / 2L}{1 + (1-D) \times t_S \times (R_{NLS} + R_L) / 2L}$$

where  $V_{OUT}$  = output voltage;  $I_{LIM}$  = current limit of high-side switch;  $t_S$  = switching period;  $R_L$  = ESR of inductor;  $R_{NLS}$  = on-resistance of low-side switch; L = inductor. Equations for  $I_{LIM}$  and D are shown as follows:

$$I_{\text{LIM}} = I_{\text{LIM}}_{\text{DC100}} + V_{\text{SW}} \frac{1 - D}{R_{\text{T}}}$$

where  $I_{LIM_DC100}$  = current limit at D = 100%;  $R_T$  = transresistance from LX to COMP;  $V_{SW}$  = slope compensation (310mV ±20%); D = duty cycle:

$$D = \frac{V_{OUT} + I_O(R_{NLS} + R_L)}{V_{IN} + I_O(R_{NLS} - R_{NHS})}$$

where  $V_{OUT}$  = output voltage;  $V_{IN}$  = input voltage;  $I_O$  = output current;  $R_L$  = ESR of inductor;  $R_{NHS}$  = on-resistance of highside switch;  $R_{NLS}$  = on-resistance of low-side switch. See the *Typical Application Circuit* for external components.

- **Note 2:** Specifications to -40°C are guaranteed by design and not production tested.

- Note 3: LX has internal clamp diodes to PGND and IN pins 2 and 4. Applications that forward bias these diodes should take care not to exceed the IC's package power dissipation limits.

- **Note 4:** When connected together, the LX output is designed to provide 3.5A<sub>RMS</sub> current.

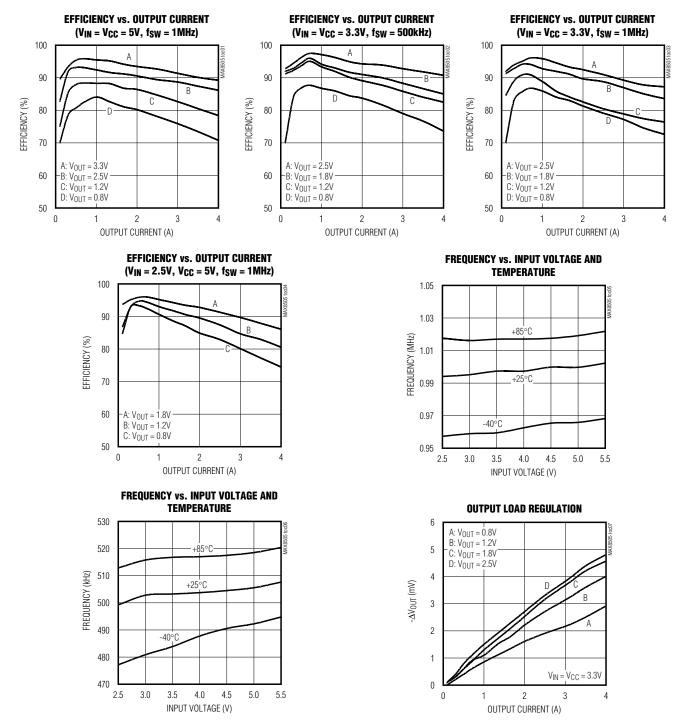

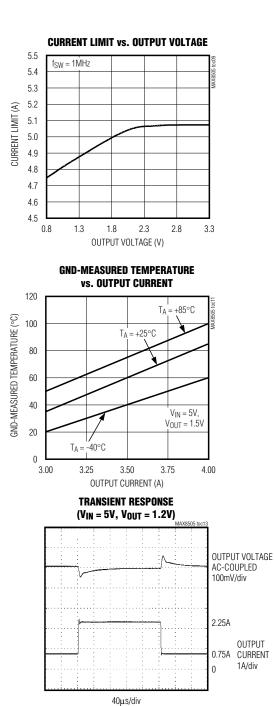

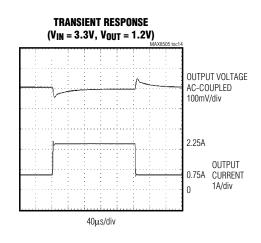

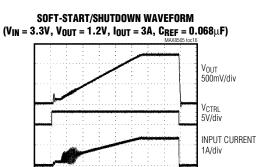

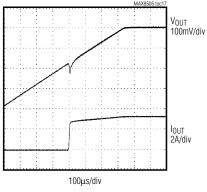

(Typical values are at V<sub>IN</sub> = V<sub>CC</sub> = V<sub>CTL</sub> = 5V, V<sub>OUT</sub> = 1.2V, I<sub>OUT</sub> = 3A, and T<sub>A</sub> = +25°C, unless otherwise noted.)

**Typical Operating Characteristics**

MIXIM

**MAX8505**

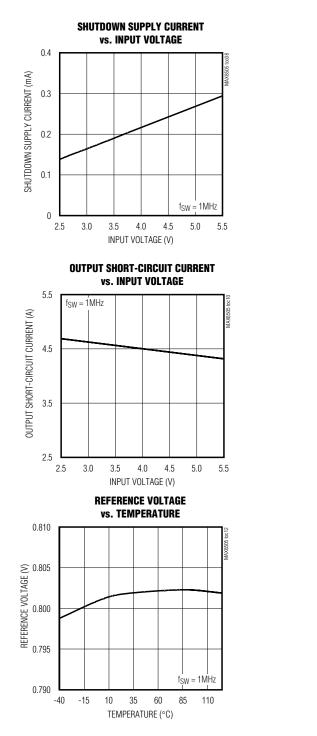

# **Typical Operating Characteristics (continued)**

(Typical values are at  $V_{IN} = V_{CC} = V_{CTL} = 5V$ ,  $V_{OUT} = 1.2V$ ,  $I_{OUT} = 3A$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# **MAX8505**

# Typical Operating Characteristics (continued)

(Typical values are at  $V_{IN} = V_{CC} = V_{CTL} = 5V$ ,  $V_{OUT} = 1.2V$ ,  $I_{OUT} = 3A$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

400µs/div

V<sub>POK</sub> 5V/div

TRANSIENT RESPONSE DURING SOFT-START

# Pin Description

| PIN          | NAME            | FUNCTION                                                                                                                                                                                     |

|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 14, 16 | LX              | Inductor Connection. Connect an inductor between these pins and the regulator output. All LX pins must be connected together externally. Connect a 3300pF ceramic capacitor from LX to PGND. |

| 2, 4         | IN              | Power-Supply Inputs. Ranges from 2.6V to 5.5V. Bypass with two ceramic 22µF capacitors to GND. All IN pins must be connected together externally.                                            |

| 5            | BST             | Bootstrapped Voltage Input. High-side driver supply pin. Bypass to LX with a $0.1\mu$ F capacitor. Charged from IN with an external Schottky diode.                                          |

| 6            | V <sub>CC</sub> | Supply Voltage and Gate-Drive Supply for Low-Side Driver. Decouple with a $10\Omega$ resistor and bypass to GND with 0.1 $\mu\text{F}.$                                                      |

| 7            | POK             | Power-OK Output. Open-drain output of a window comparator that pulls POK low when the FB pin is outside the 0.8V ±12% range.                                                                 |

| 8            | CTL             | Output Control. When at GND, the regulator is off. When at $V_{CC}$ , the regulator is operating at 1MHz. For a 500kHz application, raise the pin to 2/3 $V_{CC}$ .                          |

| 9            | COMP            | Regulator Loop Compensation. Connect a series RC network to GND. This pin is pulled to GND when the output is shut down, or in UVLO or thermal shutdown.                                     |

| 10           | FB              | Feedback Input. This pin regulates to 0.8V. Use an external resistive-divider from the output to set the output voltage.                                                                     |

| 11           | REF             | Place a capacitor at this pin to set the soft-start time. This pin goes to 0V when the part is shut down.                                                                                    |

| 12           | GND             | Ground                                                                                                                                                                                       |

| 13, 15       | PGND            | Power Ground. Connect this pin to GND at a single point.                                                                                                                                     |

# **Detailed Description**

The MAX8505 is a high-efficiency synchronous buck regulator capable of delivering up to 3A of output current. It operates in PWM mode at a high fixed frequency of 500kHz or 1MHz, thereby reducing external component size. The MAX8505 operates from a 2.6V to 5.5V input voltage and can produce an output voltage from 0.8V to  $0.85 \times V_{IN}$ .

#### **Controller Block Function**

The MAX8505 step-down converter uses a PWM current-mode control scheme. An open-loop comparator compares the voltage-feedback error signal against the sum of the amplified current-sense signal and the slope compensation ramp. At each rising edge of the internal clock, the internal high-side MOSFET turns on until the PWM comparator trips. During this on-time, current ramps up through the inductor, sourcing current to the output and storing energy in the inductor. The current-mode feedback system regulates the peak inductor current as a function of the output-voltage error signal. Since the average inductor current is nearly the same as the peak inductor current, the circuit acts as a switch-mode transconductance amplifier. To preserve inner-loop stability and eliminate inductor staircasing, a slope-

compensation ramp is summed into the main PWM comparator. During the second half of the cycle, the internal high-side N-channel MOSFET turns off, and the internal low-side N-channel MOSFET turns on. The inductor releases the stored energy as its current ramps down while still providing current to the output. The output capacitor stores charge when the inductor current exceeds the load current, and discharges when the inductor current is lower, smoothing the voltage across the load. Under overload conditions, when the inductor current exceeds the current limit (see the *Current Limit* section), the high-side MOSFET does not turn on at the rising edge of the clock and the low-side MOSFET remains on to let the inductor current ramp down.

#### **Current Sense**

An internal current-sense amplifier produces a current signal proportional to the voltage generated by the high-side MOSFET on-resistance and the inductor current (R<sub>DS(ON)</sub> × I<sub>L</sub>x). The amplified current-sense signal and the internal slope-compensation signal are summed together into the comparator's inverting input. The PWM comparator turns off the internal high-side MOSFET when this sum exceeds the feedback voltage from the voltage-error amplifier.

#### **Current Limit**

The MAX8505 offers both high-side and low-side current limits. The high-side current limit monitors the inductor peak current and the low-side current limit monitors the inductor valley current. Current-limit thresholds are 6A (typ) for high side and 3.8A (typ) for low side. If the output inductor current exceeds the highside current limit during its on-time, the high-side MOS-FET turns off and the synchronous rectifier turns on. The inductor current is continuously monitored during the on-time of the low-side MOSFET. If the inductor current is still above the low-side current limit at the moment of the next clock cycle, the high-side MOSFET is not turned on and the low-side MOSFET is kept on to continue discharging the output inductor current. Once the inductor current is below the low-side current limit, the high-side MOSFET is turned on at the next clock cycle. If the inductor current stays less than the high-side current limit during the minimum on duty ratio, the normal operation resumes at the next clock cycle. Otherwise, the current-limit operation continues.

**Vcc Decoupling** Due to the high switching frequency and tight output tolerance (1%), decouple V<sub>CC</sub> from IN with a  $10\Omega$ resistor and bypass to GND with a  $0.1\mu$ F capacitor. Place the capacitor as close to V<sub>CC</sub> as possible.

#### Bootstrap (BST)

Gate-drive voltage for the high-side N-channel switch is generated by a bootstrapped capacitor boost circuit. The bootstrapped capacitor is connected between the BST pin and LX. When the low-side N-channel MOSFET is on, it forces LX to ground and charges the capacitor to V<sub>IN</sub> through diode D1. When the low-side N-channel MOSFET turns off and the high-side N-channel MOSFET turns on, LX is pulled to V<sub>IN</sub>. D1 prevents the capacitor from discharging into V<sub>IN</sub> and the voltage on the bootstrapped capacitor is boosted above V<sub>IN</sub>. This provides the necessary voltage for the high driver. A Schottky diode should be used for D1.

#### Frequency Selection/Enable (CTL)

The MAX8505 includes a frequency selection circuit to allow it to run at 500kHz or 1MHz. The operating frequency is selected through a control input, CTL, which has three input threshold ranges that are ratiometric to the input supply voltage. When CTL is driven to GND, it acts like an enable pin, switching the output off. When the CTL input is driven to >0.8 × V<sub>CC</sub>, the MAX8505 is enabled with 1MHz switching. When the CTL input is between 0.55 × V<sub>CC</sub> and 0.7 × V<sub>CC</sub>, the part operates at 500kHz. When the CTL input is <0.45 × V<sub>CC</sub>, the device is in shutdown.

Soft-Start

To reduce input transient currents during startup, a programmable soft-start is provided. The soft-start time is given by:

$$t_{SOFT\_START} = C_{REF} \times \frac{0.8V}{25\mu A}$$

A minimum capacitance of  $0.01\mu$ F at REF is recommended to reduce the susceptibility to switching noise.

#### **Power-OK (POK)**

The MAX8505 also includes an open-drain POK output that indicates when the regulator output is within  $\pm 12\%$  of its nominal output. If the output voltage moves outside this range, the POK output is pulled to ground. Since this comparator has no hysteresis on either threshold, a 50µs delay time is added to prevent the POK output from chattering between states. The POK should be pulled to V<sub>IN</sub> or another supply voltage less than 5.5V through a resistor.

#### UVLO

If V<sub>CC</sub> drops below +2.25V, the UVLO circuit inhibits switching. Once V<sub>CC</sub> rises above +2.35V, the UVLO clears, and the soft-start sequence activates.

#### **Thermal Protection**

Thermal-overload protection limits total power dissipation in the device. When the junction temperature exceeds  $T_J = +170$ °C, a thermal sensor forces the device into shutdown, allowing the die to cool. The thermal sensor turns the device on again after the junction temperature cools by 20°C, resulting in a pulsed output during continuous overload conditions. Following a thermal-shutdown condition, the soft-start sequence begins anew.

#### **Design Procedure**

#### **Duty Cycle**

The equation below shows how to calculate the resulting duty cycle when series losses from the inductor and internal switches are accounted for:

$$\begin{split} D &= \frac{V_{OUT} + I_{OUT}(R_{NLS} + R_L)}{V_{IN} + I_{OUT}(R_{NLS} - R_{NHS})} = \frac{V_{OUT} + I_{OUT}(R_{NLS} + R_L)}{V_{IN}} \\ \text{if } R_{NLS} &= R_{NHS} \end{split}$$

where  $V_{OUT}$  = output voltage;  $V_{IN}$  = input voltage;  $I_{OUT}$  = output current (3A maximum);  $R_L$  = ESR of the inductor;  $R_{NHS}$  = on-resistance of the high-side switch; and  $R_{NLS}$  = on-resistance of the low-side switch.

#### **Output Voltage Selection**

The output voltage of the MAX8505 can be adjusted from 0.8V to 85% of the input voltage at 500kHz or up to 80% of the input voltage at 1MHz. This is done by connecting a resistive-divider (R2 and R3) between the output and the FB pin (see the *Typical Operating Circuit*). For best results, keep R3 below 50k $\Omega$  and select R2 using the following equation:

$$R2 = R3 \times \left(\frac{V_{OUT}}{V_{REF}} - 1\right)$$

where  $V_{REF} = 0.8V$ .

#### Inductor Design

When choosing the inductor, the key parameters are inductor value (L) and peak current (IPEAK). The following equation includes a constant, denoted as LIR, which is the ratio of peak-to-peak inductor AC current (ripple current) to maximum DC load current. A higher value of LIR allows smaller inductance but results in higher losses and ripple. A good compromise between size and losses is found at approximately 20% to 30% ripple-current to load-current ratio (LIR = 0.20 to 0.30):

$$L = \frac{V_{OUT} \times (1 - D)}{I_{OUT} \times LIR \times f_S}$$

where fs is the switching frequency and

Choose an inductor with a saturation current at least as high as the peak inductor current. Additionally, verify the peak inductor current does not exceed the current limit. The inductor selected should exhibit low losses at the chosen operating frequency.

**Output Capacitor Design and Output Ripple**

The key selection parameters for the output capacitor are capacitance, ESR, ESL, and the voltage rating requirements. These affect the overall stability, output ripple voltage, and transient response of the DC-DC converter. The output ripple occurs due to variations in the charge stored in the output capacitor, the voltage drop due to the capacitor's ESR, and the voltage drop due to the capacitor's ESL. Calculate the output voltage ripple due to the output capacitance, ESR, and ESL as:

$$V_{RIPPLE} = \sqrt{V_{RIPPLE(C)}^2 + V_{RIPPLE(ESR)}^2 + V_{RIPPLE(ESL)}^2}$$

where the output ripples due to output capacitance, ESR, and ESL are:

$$V_{\text{RIPPLE}(\text{C})} = \frac{I_{\text{P}-\text{P}}}{8 \times C_{\text{OUT}} \times f_{\text{S}}}$$

$$V_{RIPPLE(ESR)} = I_{P-P} \times ESR$$

$$V_{\text{RIPPLE}(\text{ESL})} = \frac{l_{\text{P}-\text{P}}}{t_{\text{ON}}} \times \text{ESL} \text{ or } \frac{l_{\text{P}-\text{P}}}{t_{\text{OFF}}} \times \text{ESL},$$

or, whichever is greater.

The ESR is the main contribution to the output voltage ripple.

IP-P, the peak-to-peak inductor current, is:

$$I_{P-P} = \frac{(V_{IN} - V_{OUT})}{f_S \times L} \times \frac{V_{OUT}}{V_{IN}}$$

Use these equations for initial capacitor selection, but determine final values by testing a prototype or evaluation circuit. As a rule, a smaller ripple current results in less output voltage ripple. Since the inductor ripple current is a factor of the inductor value, the output voltage ripple decreases with larger inductance. Use ceramic capacitors for their low ESR and ESL at the switching frequency of the converter. The low ESL of ceramic capacitors makes ripple voltages negligible. Load-transient response depends on the selected output capacitor. During a load transient, the output instantly changes by ESR × ILOAD. Before the controller can respond, the output deviates further, depending on the inductor and output capacitor values. After a short time (see Transient Response in the Typical Operating Characteristics), the controller responds by regulating the output voltage back to its nominal state. The controller response time depends on the closed-loop bandwidth, the inductor value, and the slew rate of the transconductance amplifier. A higher bandwidth yields a faster response time, thus preventing the output from deviating further from its regulating value.

#### M/IXI/M

#### Input Capacitor Design

The input capacitor reduces the current peaks drawn from the input power supply and reduces switching noise in the IC. The impedance of the input capacitor at the switching frequency should be less than that of the input source so high-frequency switching currents do not pass through the input source but instead are shunted through the input capacitor. A high source impedance requires larger input capacitance. The input capacitor must meet the ripple current requirement imposed by the switching currents. The RMS input ripple current is given by:

$$I_{\text{RIPPLE}} = I_{\text{LOAD}} \times \sqrt{\frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}}^2}}$$

where IRIPPLE is the input RMS ripple current.

Use sufficient input bypass capacitance to ensure that the absolute maximum voltage rating of the MAX8505 is not exceeded in any condition. When input supply is not located close to the MAX8505, a bulk bypass input capacitor may be needed.

#### Compensation Design

The double pole formed by the inductor and output capacitor of most voltage-mode controllers introduces a large phase shift, which requires an elaborate compensation network to stabilize the control loop. The MAX8505 controller utilizes a current-mode control scheme that regulates the output voltage by forcing the required current through the external inductor, eliminating the double pole caused by the inductor and output capacitor, and greatly simplifying the compensation network. A simple type 1 compensation with single compensation resistor (R1) and compensation capacitor (C8) create a stable and high-bandwidth loop (see the *Typical Operating Circuit*).

An internal transconductance error amplifier compensates the control loop. Connect a series resistor and capacitor between COMP (the output of the error amplifier) and GND to form a pole-zero pair. The external inductor, internal current-sensing circuitry, output capacitor, and external compensation circuit determine the loop stability. Choose the inductor and output capacitor based on performance, size, and cost. Additionally, select the compensation resistor and capacitor to optimize controlloop stability. The component values shown in the *Typical Operating Circuit* yield stable operation over a broad range of input-to-output voltages. For customized compensation networks that increase stability or transient response, the simplified loop gain can be described by the equation:

$$\begin{split} A_{VOL} &= \frac{V_{FB}}{V_{OUT}} \times gm_{ERR} \times R_{OERR} \times \\ & \left( \frac{s \times C_{COMP} \times R_{COMP} + 1}{(s \times C_{COMP} \times R_{COMP} + 1) \times (s \times C_{PARA} \times R_{COMP} + 1)} \right) \times \\ & \frac{R_L}{R_T} \times \left( \frac{s \times C_{OUT} \times R_{ESR} + 1}{s \times C_{OUT} \times R_L + 1} \right) \end{split}$$

where:

gm<sub>ERR</sub> (COMP transconductance) = 100µmho

$R_{OERR}$  (output resistance of transconductance amplifier) =  $20 M \Omega$

CCOMP (compensation capacitor at COMP pin)

$R_T$  (current-sense transresistance) = 0.086 $\Omega$

CPARA (parasitic capacitance at COMP pin) = 10pF

R<sub>L</sub> (load resistor)

COUT (output capacitor)

RESR (series resistance of COUT)

$s = j2\pi f$

In designing the compensation circuit, select an appropriate converter bandwidth (f<sub>C</sub>) to stabilize the system while maximizing transient response. This bandwidth should not exceed 1/10 of the switching frequency. Use 100kHz as a reasonable starting point. Calculate C<sub>COMP</sub> based on this bandwidth using the following equation:

$$R_{COMP} = \frac{I_{OUT} \times R_T \times (R3 + R2) \times 2\pi \times f_C \times C_{OUT}}{V_{OUT} \times gm_{ERR} \times R2}$$

where R2 and R3 are the feedback resistors.

Calculate  $C_{COMP}$  to cancel out the pole created by RL and  $C_{OUT}$  using the following equation;

$$C_{COMP} = R_L \times \frac{C_{OUT}}{R_{COMP}}$$

## **Applications Information**

#### **PC Board Layout Considerations**

Careful PC board layout is critical to achieve clean and stable operation. The switching power stage requires particular attention. Follow these guidelines for good PC board layout:

- Place decoupling capacitors as close to the IC as possible. Keep power ground plane (connected to PGND) and signal ground plane (connected to GND) separate.

- Connect input and output capacitors to the power ground plane; connect all other capacitors to the signal ground plane.

- 3) Keep the high-current paths as short and wide as possible. Keep the path of switching current short and minimize the loop area formed by the high-side MOSFET, the low-side MOSFET, and the input capacitors. Avoid vias in the switching paths.

- 4) If possible, connect IN, LX, and PGND separately to a large copper area to help cool the IC to further improve efficiency and long-term reliability.

- 5) Ensure all feedback connections are short and direct. Place the feedback resistors as close to the IC as possible.

- 6) Route high-speed switching nodes away from sensitive analog areas (FB, COMP).

**Chip Information**

TRANSISTOR COUNT: 3352 PROCESS: BICMOS

# **Typical Application Circuit**

**MAX8505**

## **Functional Diagram**

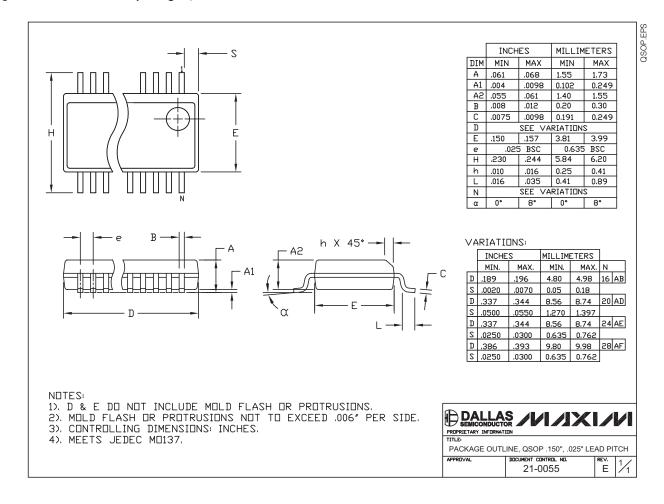

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2003 Maxim Integrated Products

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.