# 安路科技 ELF 系列 CPLD 数据手册

DS002 (v1.8) 2018/2/2

## 目 录

| Ħ   | 灵     |                               | . 1 |

|-----|-------|-------------------------------|-----|

| 1   | 简介.   |                               | . 1 |

| 1.  | 1 ELI | F 器件系列特性                      | 1   |

| 1.3 | 2 ELI | F CPLD 器件市场定位                 | 4   |

| 2   | ELF   | <i>哭构概述</i>                   | . 5 |

| 2.  | 1 PLI | B 模块                          | 6   |

|     | 2.1.1 | PFB 操作模式                      | 7   |

|     | 2.1.2 | 寄存器                           | 7   |

|     | 2.1.3 | 互连(Routing)                   | 8   |

| 2.5 | 2 时年  | 钟和全局信号资源                      | 8   |

| 2.3 | 3 输   | 入输出逻辑( <b>IOL</b> )           | 10  |

|     | 221   | <b>给</b> λ 宏                  | 10  |

|     | 2.3.2 | <i>輸出寄存器</i>                  | 10  |

| 2.4 | 4 输)  | 入输出缓冲器(IOB)                   | 11  |

|     | 2.4.1 | 简介                            | 11  |

|     | 2.4.2 | I/O BANK                      | 12  |

|     | 2.4.3 |                               |     |

|     |       | F CPLD 位流配置说明                 |     |

|     | 2.5.1 | 配置模式                          | 18  |

|     | 2.5.2 | 配置流程                          | 18  |

|     | 2.5.3 | MSPI 配置模式                     | 19  |

|     | 2.5.4 | SFL(Self Flash Loader)自下载配置模式 | 21  |

|     | 2.5.5 | Dual Boot 模式                  | 21  |

|     | 2.5.6 | JTAG 配置模式                     | 22  |

|     | 2.5.7 | OTP 功能                        | 22  |

|   | 2.5.8   | 上电延迟               | 23 |

|---|---------|--------------------|----|

|   | 2.5.9   | 保密配置选项             | 23 |

|   | 2.5.10  | 内部振荡器              | 23 |

|   | 2.5.11  | 配置接口 <b>IP</b>     | 24 |

| 3 | 直流和     | 口交流特性              | 25 |

| 3 |         | <b></b>            | 25 |

|   | 3.1.1   | 最大绝对额定值            | 25 |

|   | 3.1.2   | 推荐基本操作条件           | 26 |

|   | 3.1.3   | 静态供电电流 1,2         | 27 |

|   | 3.1.4   | 热插拔规格              | 27 |

|   | 3.1.5   | 上电复位电压阈值           | 27 |

|   | 3.1.6   | I/O 直流电气特性         | 28 |

|   | 3.1.7   | I/O 管脚电容           | 29 |

|   | 3.1.8   | 差分 I/O 电学特性        | 29 |

|   | 3.1.9   | 单端 I/O 直流电学特性      | 30 |

| 3 | 3.2 交流  | <b></b>            | 31 |

|   | 3.2.1   | 时钟性能               | 31 |

|   | 3.2.2   | I/O 接口性能           | 31 |

|   | 3.2.3   | 配置模块和 JTAG 规格      | 32 |

| 1 | 引脚和     | <i>口封装</i>         | 33 |

| 4 | 4.1 引服  | 却定义和规则             | 33 |

| 4 | 4.2 电测  | 原电压管脚              | 34 |

| 4 | 1.3 EL1 | 1L300、EL1F650 引脚说明 | 35 |

|   | 4.3.1   | TQFP100            | 35 |

|   | 4.3.2   | TQFP144            | 37 |

| 4 | 1.4 EL1 | 1A300、EL1A650 引脚说明 | 40 |

|   |         |                    |    |

|   | 4.4.1  | TQFP100      | 40 |

|---|--------|--------------|----|

|   | 4.4.2  | TQFP144      | 42 |

|   | 4.4.3  | PQFP44       | 45 |

| 2 | 4.5 封约 | 装信息          | 46 |

|   | 4.5.1  | TQFP100 封装规格 | 46 |

|   | 4.5.2  | TQFP144 封装规格 | 47 |

|   | 4.5.3  | PQFP44 封装规格  | 48 |

| 5 | 订购     | 信息           | 49 |

|   |        | <br>信息       | 50 |

## 1 简介

#### 1.1 ELF 器件系列特性

- 内嵌 Flash 的快速上电 CPLD 器件

- 先进的 130nm flash 低功耗工艺

- 内嵌非易失性 Flash

- 可支持快速上电工作(<1 ms)

- 静态功耗 < 2mA

- 3.3~2.5 V 单电源供电(Vccext)

- 3.3~1.2 V IO 电压 ( Vccio )

- 基于灵活的 CPLD 可配置逻辑模块(PLBs)

- 每个 PLB 包含 8 个基于 4 输入查找表和 DFF 锁存器构成的逻辑单元 (LE)。

- 多种可编程逻辑单元规模可选 (等效 300 个 LE~650 个 LE )

- 每个 PLB 内嵌专用进位链可实现 8 位算术逻辑。

- 内部 PLB 可配置成独立的深度为 32, 宽度为 4的 RAM

- 丰富的互连资源保证布通率,8个全局时钟

- 高性能,灵活的输入/输出缓冲器

- 4个IO BANK, 支持热插拔

- 除支持标准 CMOS/TTL 接口外, BANK1 支持差分输入,四个 BANK 均支持 EMULATED LVDS 输出

- 内嵌非易失性 eFlash 存储器

- 支持 DualBoot,存储 2 套码流,主码流失效时自动加载备用码流

- 只存储 1 套码流时,用户可用内部 Flash 存储空间 16Kbyte

- 若用外部接口下载,则可用空间 32Kbyte

- 支持 OTP 模式,提供用户码流保密,eFlash 存储器可进行访问控制,用户可设置禁止读或写eFlash 内部码流

- Single-Boot 模式时,用户可使用 16K Bytes 内部 Flash 空间

• 支持 42 位 DNA: 每个芯片拥有唯一的 34 位芯片 DNA 和至少 8 位用户 trace ID

#### ■ 配置模式

- JTAG 模式 (IEEE-1532)

- 上电自动加载内部 eFlash 存储的码流

- 主动 SPI 接口

#### ■ 封装

- TQFP 44/100/144 封装

- 为用户提供更多的可用 IO,最大可用 IO数:

- 84(100pin 封装)

- 120(144pin 封装)

- 31(44pin 封装)

#### 表 1-1 ELF 系列选型器件参数列表

| 参数                  | Elf-300  | Elf-650  |

|---------------------|----------|----------|

| 等效 4 输入查找表(LUT4)    | 300      | 650      |

| 分布式 RAM(Kbits)      | 2K       | 7K       |

| Vccext 电压           | 2.5/3.3V | 2.5/3.3V |

| 用户可用内部 Flash 容量(KB) | 161      | 161      |

| I/O Banks           | 4        | 4        |

| 最大可用 I/O 数目         | 84       | 120      |

| LVDS 输入对数           | 10       | 12       |

| 封装和可用 IO 数目         | X        |          |

| 100-pin TQFP        | 84       | 84       |

| 144-pin TQFP        | /        | 120      |

| 44-pin TQFP         | 31       |          |

## 说明:

- 1. 位流存储于芯片内部时,内部 32KB eFlash 中 16KB 空间用于存储位流,用户可使用剩余的 16KB 空间。

- 2. 位流存储于芯片外部时,用户可以使用内部 32KB eFlash 空间。

## 1.2 ELF CPLD 器件市场定位

安路 ELF 系列 CPLD 器件,定位于低成本、低功耗可编程 CPLD 市场。相比对标器件更多逻辑容量、分布式 RAM 支持、更多 IO 支持、多种封装支持等特性,使得 ELF 器件合适通信、工业、消费等应用领域中逻辑桥接、接口扩展、系统控制等功能。ELF 器件支持 OTP 模式,上电 1ms 快速上电启动功能适合于上电时间敏感的运动控制领域和安全应用领域。

## 2 ELF 架构概述

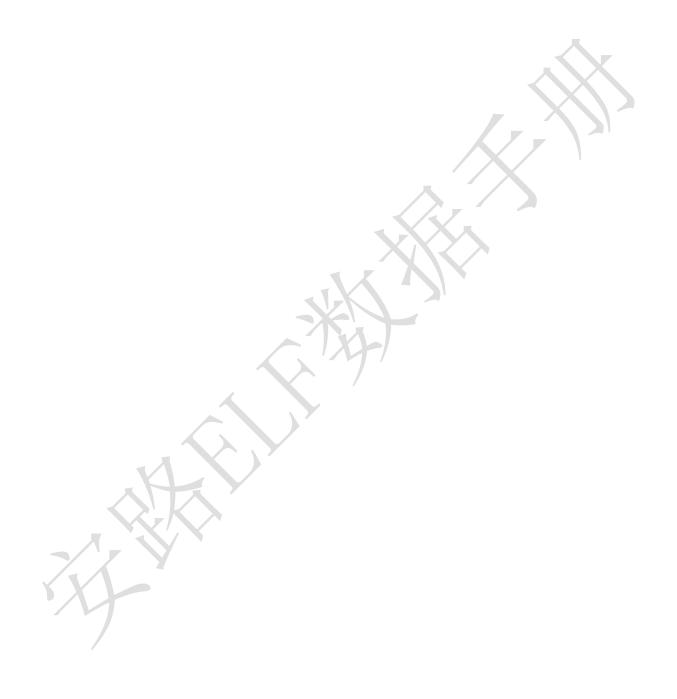

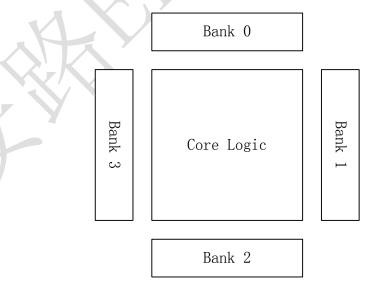

图 2-1: ELF 器件简化框图

ELF 系列器件由查找表逻辑模块(PLB)阵列构成核心资源,输入输出缓冲器分布在芯片四边。ELF 器件基于 eFlash 工艺,内部集成有 32K BYTE 的非易失存储器,用户可以通过 JTAG 接口编写 eFlash。

ELF 芯片 IO 有 4 个 BANK, 其中 BANK-1 的 IO 增加了对差分输入信号的支持, 四个 BANK 均支持 EMULATED LVDS 输出。

## 2.1 PLB 模块

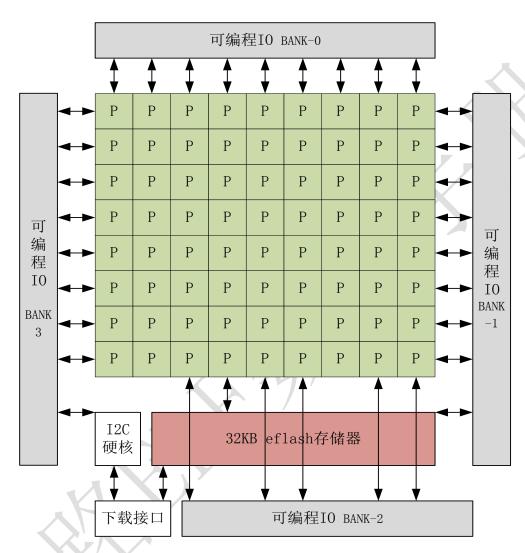

可编程逻辑块(PLB)按照行/列规则排布成二维阵列,每个 PLB 包括可编程互连 (routing)和可编程功能块(Programmable Functional Block, PFB)。PFB 是 CPLD 的可编 程功能核心。ELF 器件内部 PFB 可实现:逻辑,算术 ROM 功能以及信号锁存 DFF。

ELF PFB 分为两类: MPFB 和 LPFB。其唯一不同点是: LPFB 不具有分布式 RAM (distribute RAM) 功能。PFB 内部包含 4 个 SLICE, 编号 0~3。SLICE 0,1 为 MSLICE 类型, SLICE 2,3 为 LSLICE 类型。

图 2-1-1:可编程功能块(PFB)结构图:

#### 2.1.1 PFB 操作模式

MPFB 有 4 种操作模式:逻辑,算术,分布式 RAM 和 ROM。

LPFB有3种操作模式:逻辑,算术和ROM。

#### 逻辑模式

在逻辑模式中, PFB 中的 LUT4 配置成 4 输入组合逻辑查找表,任意 4 输入函数都可以用这个查找表实现。PFB 内的 LUT 还可以通过内部输出组合电路级联成更大的查找表。

#### 算术模式

算术模式会利用 SLICE 内部快速进位链实现快速、高效的算术功能,每个 PLB 可实现 8bit 算术逻辑。可支持的算术逻辑有:加法,减法,带控制选择的加/减法器,计数器,以及比较器。

上下相邻 PFB 可级联实现更宽位宽的算术逻辑。

#### 分布式 RAM 模式

MPFB 可配置成此模式,一个 MPFB 可配置成 32x4 的简单双口 RAM(一口写/一口读)。多个 MPFB 组合可实现深度/位宽的扩展,也可以实现真双口 RAM。

#### ROM 模式

所有 SLICE 在 LUT 逻辑下可用作 ROM 模式,用户可以通过软件设置 ROM 初值。

#### 2.1.2 寄存器

PFB 内每个 SLICE 包含 2 个可配置寄存器。可锁存 LUT 的输出或者来自互连的 MI 输入。寄存器配置选项:

- 边沿触发的锁存器(DFF)或电平使能锁存器(LATCH)

- 支持同步复位的同时且支持异步复位 0 或置位 1

- SLOAD 功能和移位功能。

- 是否使用 ClockEnable 使能

- CLK/CE/SR 支持上升沿/下降沿/0/1 选择

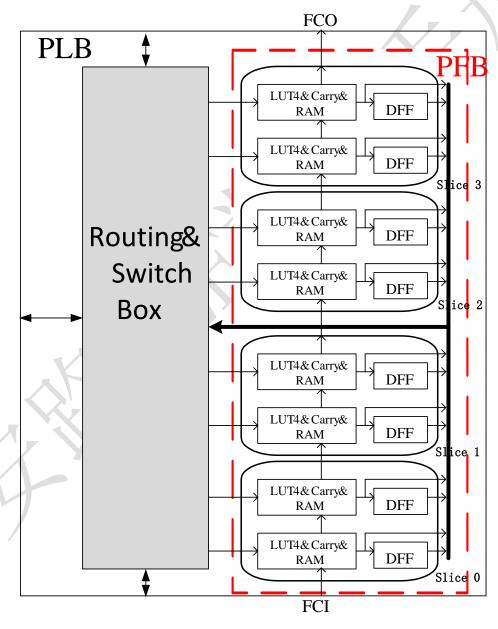

#### 2.1.3 **互连**(Routing)

可编程互连实现 CPLD 内部各个功能块之间的信号传输。ELF 系列器件内部拥有丰富的互连资源,包括线间选通开关、线缓冲器以及信号走线。ELF 系列互连线全部带有缓冲器,从而实现高速信号传输和可靠的信号完整性。

图 2-1-4: ELF 互连架构

PFB 间信号通过水平通道和垂直通道传输。PFB 可以直接驱动水平/垂直通道。通道之间通过 channel RSB(routing switch box) 进行切换。通道上传输的信号通过 local RSB 进入 PFB。

## 2.2 时钟和全局信号资源

ELF 系列器件每边有 2 个合计 8 个专用全局时钟输入管脚,为全局时钟树提供高品质的 clock 输入。当这些脚不用做时钟输入时也可以配置为普通用户 IO。

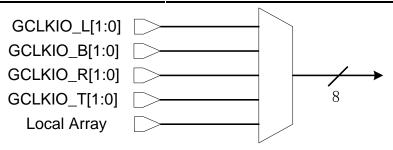

ELF 系列内部时钟资源提供 8 个低延迟、低偏斜、互联的全局时钟/信号网络。全局时钟/信号网络能够为 CPLD 各个模块提供统一的高性能、低抖动、低偏斜时钟源和复位信号,同时全局时钟也可用于高扇出信号。每一个全局时钟网络可以驱动芯片内的每一个 PFB、IOB 中 DFF 资源。图 2-2-1 给出了全局时钟 CMUX 的输入资源。

图 2-2-1:全局时钟 CMUX 的输入资源

#### 动态时钟使能(DCE)

动态时钟使能(DCE)模块允许用户逻辑控制动态控制时钟网络。当选定时钟被禁止,所有被该时钟驱动的逻辑都静止,从而减少功耗。

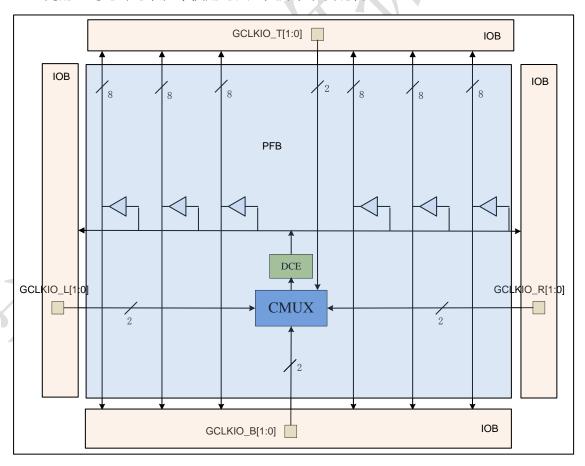

#### 全局时钟分布树

全局时钟网络驱动到每一个独立的 PFB 列,每一列的 8 个全局时钟从 PFB 列的底端延伸至顶端。每一列的全局时钟可以在不使用时独立关掉以节省功耗。

图 2-2-2:全局时钟分布树

2.3 输入输出逻辑(IOL)

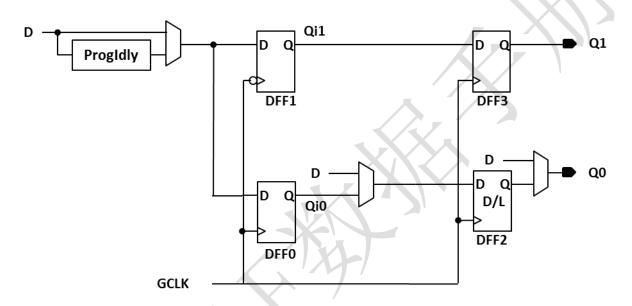

#### 2.3.1 输入寄存器

输入输出逻辑(IOL)中的输入寄存器用来处理高速接口,将其降低为内部核心逻辑可以处理的 频率。输入寄存器中均包含可配置延时单元作为数据采样处理辅助。在次基本功能基础上增强了 对普通双边沿数据(GDDR)的支持。

图 2-3-1: 输入寄存器框图

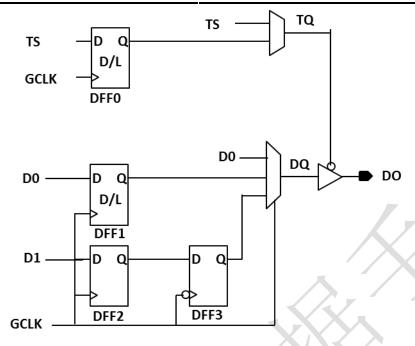

#### 2.3.2 输出寄存器

输入输出逻辑(IOL)中的输出寄存器用来处理内部核心逻辑到高速 I/O 接口的时序。

图 2-3-1: 输入寄存器框图。

图 2-3-2 输出寄存器框图

## 2.4 输入输出缓冲器 (IOB)

## 2.4.1 简介

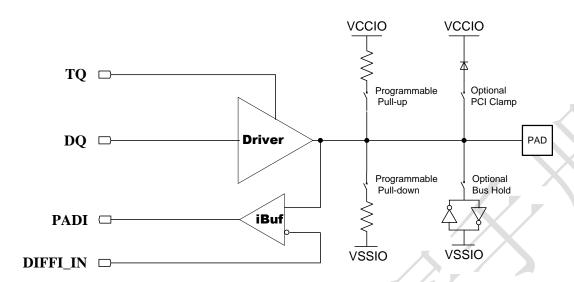

ELF 具有可配置宽电压范围的 I/O 驱动器和接收器,可支持种类繁多的标准接口。强大的功能集包括输出强度和斜率的可编程控制。

每个 IOB 包含输入、输出和三态驱动器。这些驱动器可以按照各种 I/O 标准配置。

- 单端 I/O 标准 (LVCMOS、LVTTL、HSTL、SSTL、GTL、PCI)

- BANK1 IO 支持差分输入(LVDS),四个 BANK 均支持 EMULATED LVDS 输出 IOB 支持上述电平标准的同时,IOB 支持以下配置项:

- 输出驱动能力调节

- 输出 Slew Rate 调节

- 弱上拉/下拉电阻选择配置

- PCI Clamp 使能

- Bus Hold 功能使能

图 2-4-1:基本 IOB 及其与内部逻辑和器件焊盘的连接

各 IOB 直接连接 IOL 组成逻辑对,该逻辑对包含输入和输出逻辑资源,可用于数据和 IOB 的三态控制。

#### 2.4.2 I/O BANK

ELF 器件有 4 个 I/O 组 Bank 0~3。所有的下载端口(包括 JTAG 口)和用户 IO 复用,为客户提供最大数量的可用 IO。位于芯片右侧的组 1 可支持高速 LVDS 差分输入。每一个 I/O 组由对应的  $V_{\text{CCIO}}$  供电。

图 2-4-2: I/O 组示意图

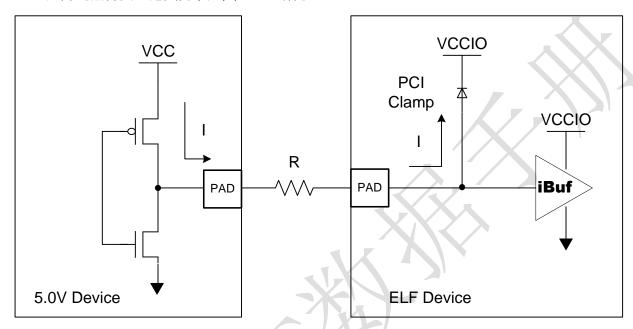

#### 2.4.3 兼容 5V 输入

ELF I/O 可以工作在 1.2-3.3V 电压范围,不能直接接收 5V 输入。如果 5V 电压信号驱动到 ELF 器件的输入,需要外部串接电阻和打开 ELF I/O 内部的 PCI 箝位二极管把输入端口接收到的电压降到器件安全范围内,如图 2-4-3 所示。

图 2-4-3:5V 输入驱动 AL3 器件

电阻 R 值依赖于 PCI 箝位二极管的电流特性,二极管的电压电流特性见表 2-4-1。

为支持 5V 输入,建议 VCCIO 电压工作在 2.5-3.0V 范围。I/O 器件最大容限绝对电压为 VIMAX=3.7V,设置 VCCIO=2.5V,则二极管上的压降为 VDIO = VI – VCCIO = 3.3 – 2.5 = 0.8V。IDIO @0.8V = 2.85Ma, R = (5 – 3.3)V/2.85Ma = 596Ohm。

表 2-4-1: PCI 箝位二极管的电流特性

| V <sub>D</sub> (V) | I <sub>max</sub> | Unit |

|--------------------|------------------|------|

| 0.0                | 0.92             | Ua   |

| 0.1                | 9.2              | Ua   |

| 0.2                | 20               | Ua   |

| 0.3                | 30.4             | Úa   |

| 0.4                | 43.3             | Ua   |

| 0.5                | 76.5             | Ua   |

| 0.6                | 0.15             | Ma   |

| 0.7                | 0.36             | Ma   |

| 0.8                | 2.85             | Ma   |

| 0.9                | 9.42             | Ма   |

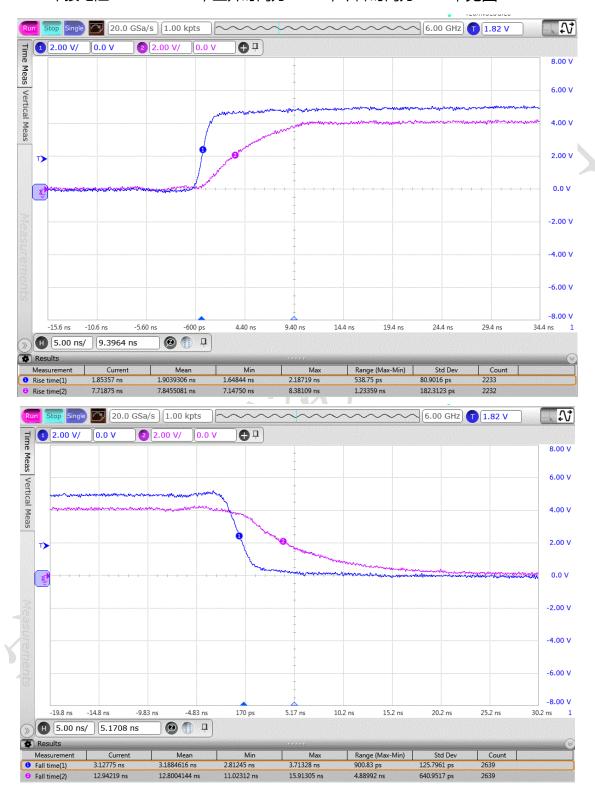

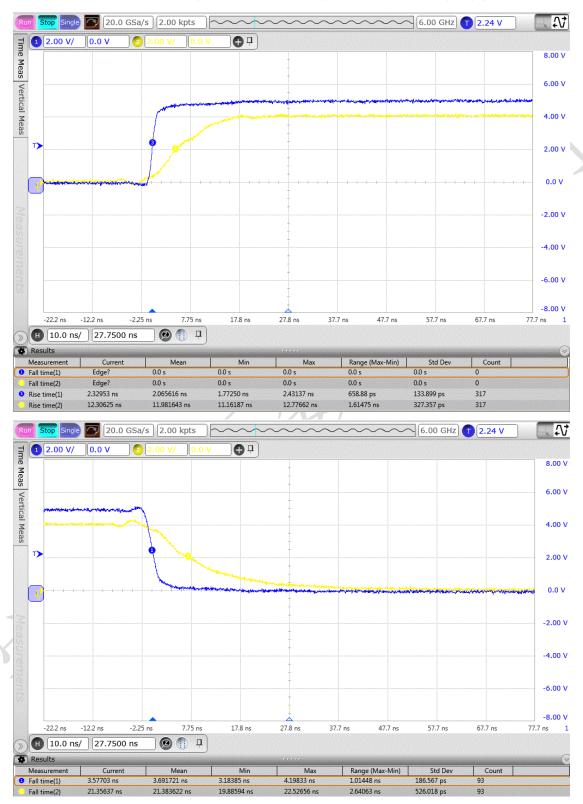

在输入信号频率为 800KHz 条件下,箝位通路分别串接不同阻值电阻,在 ELF 接收端测量波形如图 2-4-4 ~图 2-4-6 所示。

■ 串接电阻 R=330 Ohm, 上升时间为 7.8ns, 下降时间为 12ns, 见图 2-4-4

图 2-4-4:5V 输入驱动 ELF 器件接收端波形 @R=330 Ohm

■ 串接电阻 R=560 Ohm, 上升时间为 12ns, 下降时间为 21ns, 见图 2-4-5

图 2-4-5:5V 输入驱动 ELF 器件上升/下降沿 @R=560 Ohm

## 2.5 ELF CPLD 位流配置说明

ELF CPLD 芯片支持多种配置方式。ELF CPLD 芯片所有配置引脚都和用户 IO 复用,复用引脚在配置完成之后会根据用户的设置转换到用户输入输出模式或保持配置模式,用户可使用 TD 软件在 Elf Attr option 中设置配置引脚是否复用。

#### ELF 提供的位流加载方式有:

- JTAG 模式:可对内部 eFlash 进行位流编程,可直接下载位流进内部 SRAM

- CPLD 上电自加载:芯片如同 CPLD,内部电路直接加载芯片内 eFlash 中的位流,加载时间最快<1ms,实现上电即工作

- 外部 MSPI 串行下载

- Dual Boot 配置, 首先从芯片内 eFlash 加载位流, 如果失败, 会从 eFlash 或外部 spi Flash 下载另外一个受保护的位流

配置模式 SFL MSPI **Dual Boot JTAG** 类型 配置引脚名 自配置模式 外部 SPI 双重启动 **PROGRAMN PROGRAMN** 复用 INITN 复用 INITN DONE 复用 **DONE** TMS TCK JTAG 复用 TDO TDI **JTAGEN** MOSI 复用 MOSI-MISO 复用 MISO **SPICSN SPICSN** 复用 SCLK 复用 SCLK

表 2-5-1 为 ELF 配置模式及引脚

#### 所有配置模式共用信号:

- 配置开始信号引脚(PROGRAMN),内部带上拉电阻

- 配置完成引脚(DONE),漏端开路输出,内部带上拉电阻

- 配置错误指示引脚(INITN),漏端开路输出,内部带上拉电阻

在 Elf Attr option 中可以分别设置属性 program\_pin\_persistn、done\_pin\_persist 和 init pin persist 来决定是配置 IO 或者用户 IO 。

#### 其他配置专用信号:

- 边界扫描相关引脚(TDI, TDO, TMS, TCK, JTAGEN)

- SPI 模式片选输出(SPICSN)

- SPI 模式数据输出(MOSI)

- SPI 模式数据输入(MISO)

- SPI 模式时种输出 (SCLK)

## 2.5.1 配置模式

ELF CPLD 支持 4 种配置方式,分别是 SFL, MSPI, DUAL BOOT 模式和 JTAG 配置模式。配置模式由 TD 软件定义,并写入内部 FLASH 的 Elf Attr option 中的模式选择位。

ELF 系列 CPLD 中 ELF-300 和 ELF-650 配置位流长度约为 11K BYTE。

## 2.5.2 配置流程

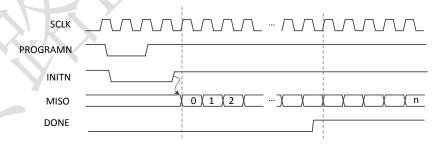

ELF CPLD 芯片的整个配置过程可以分三个部分。首先,在芯片上电复位或者系统复位信号有效后进入复位阶段,等待内部信号和电源稳定后,系统进入初始化和内部配置信息清除,初始化完成后,CPLD 开始接受配置数据写入,写入完成后,CPLD 进入芯片启动阶段。

#### 1. 初始化过程

ELF 芯片上电后,系统需要经过初始化过程才能进入配置下载状态。另外,用户如果需要重新对配置数据下载,拉低 PROGRAMN 并放开后,系统进入初始化过程,初始化过程中,CPLD将清除内部所有配置点,复位内部寄寄存器。

#### 2. 配置数据写入

ELF 初始化完成后,INITN 信号变为高电平,此时用户配置数据开始写入 ELF CPLD。

INITN 信号变为高的时候,CPLD 根据 Elf Attr option 中 Boot\_Mode 确定配置模式。JTAG配置模式在 INITN 信号变高后,可以在任何时间点进入。

#### 3. 启动阶段

ELF 完成所有配置数据写入之后,进入启动过程。ELF CPLD 启动主要完成以下功能:

- 1.释放 DONE 信号。DONE 信号从低电平变为高电平表示 ELF CPLD 顺利完成数据配置;如果一直保持低电平则表示没有顺利完成配置。

- 2.释放全局 I/O 使能信号 GOE。I/O 使能信号 GOE 的释放,能够使能所有 I/O 管脚。

- 3.释放全局复位/置位信号GSRN,允许所有的触发器根据用户逻辑改变状态。

- 4.释放全局写使能信号 GWE, 允许所有的 RAM 和触发器能够被写入。

#### 2.5.3 MSPI 配置模式

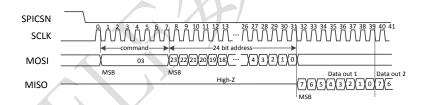

在 MSPI 模式下, ELF CPLD 为 SPI 接口提供 4 个专用信号 SCLK, MISO, MOSI 和 SPICSN, 其中 SCLK 信号提供时钟, MISO 信号是数据输入, MOSI 信号提供读命令, 地址等信息, SPICSN 为 SPI 片选。在 Elf Attr option 中设置 boot\_select 为 MSPI 或 SLF-MSPI, ELF CPLD 使能 MSPI 配置模式,并在配置阶段将这些 IO 作为配置 IO 使用。

ELF CPLD 芯片 SCLK 输出驱动配置芯片,配置芯片的数据比特位流输出给 ELF CPLD 芯片的 MISO 引脚。ELF CPLD 芯片在每个 SCLK 的上升沿接收数据,DONE 拉高表示配置完成,如果配置过程中有错误,会把 INITN 信号拉低。

MSPI 模式下的时钟 SCLK 由内部振荡器产生,用户可以设置 SCLK 频率范围。芯片上电时 SCLK 默认设定为一个的低频率值,用户可以通过 TD 软件来修改 SCLK 频率,SCLK 频率范围从 2MHz~40MHz。

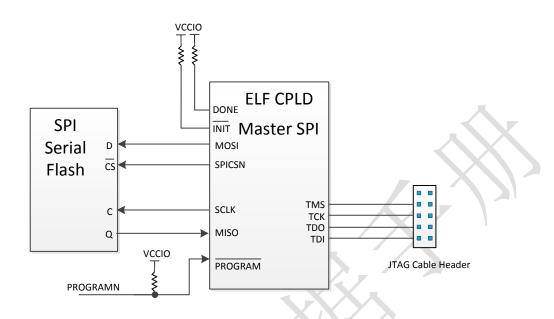

SPI Flash 数据可以使用安路 CPLD 下载线通过 JTAG 在线写入,连接如图 2-5-1 所示,也可以使用专用的烧写工具直接写入。

图 2-5-1 是 MSPI 配置方式连接图 ,PROGRAMN 信号控制复位 ELF CPLD 配置 ,其中 INITN 和 DONE 信号为漏端开路输出信号 ,内部带上拉电阻 ,DONE 信号变高 ,表示配置成功 ,芯片开始工作。配置时序如图 2-5-2 所示。

图 2-5-1: ELF CPLD MSPI 配置方式

图 2-5-2: MSPI 配置模式时序图

图 2-5-3:串行配置模式时序图

MSPI 配置方式的时序如图 2-5-3 所示。PROGRAMN 拉低后,INITN 信号被拉低,表示芯片开始初始化,大约 1ms 后芯片初始化完成,INITN 回到高电平,配置开始,CPLD 在时钟的上升沿采集配置数据,在配置完成之后,DONE 信号变高,表示配置成功,芯片开始工作。

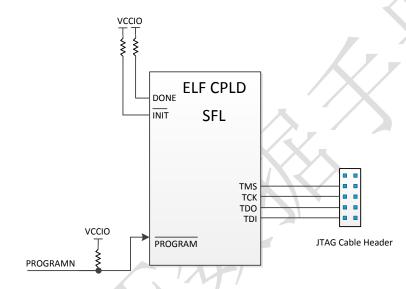

#### 2.5.4 SFL(Self Flash Loader)自下载配置模式

Self Flash Loader 模式是 ELF CPLD 的主要下载模式。该模式的优点如下:

■ 减少 BOM 成本:不需要额外的片外存储器,通过片内 eFlash 存储配置

■ 安全性:下载过程中位流不可见,可以保护用户数据,防止被读出

■ 即时工作:整个下载过程只需要1ms,满足芯片快速启动要求

图 2-5-4: SFL 配置图

## 2.5.5 Dual Boot 模式

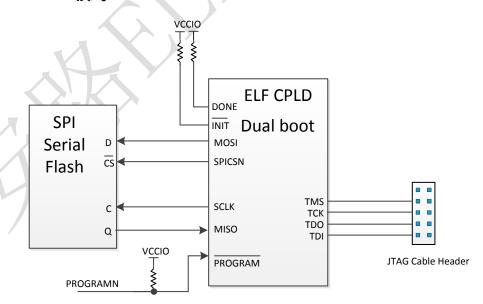

图 2-5-5 ELF CPLD Dual Boot 配置方式

片内 eFlash 分为 2 块存储空间 CFM/UFM。CFM 用来存储配置位流。UFM 用来存储用户数据或配置位流。当 UFM 存储用户配置位流时,ELF CPLD 可设置为 Dual Boot 状态;当 CFM 中的位流配置失败后,能自动跳转到 UFM 的位流进行下载。Dual boot 模式可以提高用户设计的可靠性,在一个配置数据被破坏的情况下,通过另一个配置数据启动工作。

另外 Dual Boot 配置方式也可以将 SFL 和 MSPI 结合在一起。这种设置情况下,可以设置为首先尝试从内部 eFlash 的 CFM 开始配置,如果内部配置失败,ELF 再尝试通过 MSPI 从外部配置。

#### 2.5.6 JTAG 配置模式

ELF CPLD 提供标准 JTAG 接口,可以通过 JTAG 方式进行配置。JTAG 方式配置是通过 ELF 4 个配置引脚(TDI, TDO, TMS, TCK)进行的。JTAG 配置模式在 INITN 信号变高后,不管配置模式如何,或者其他模式正在配置过程中,JTAG 均可以通过指令中断其他配置过程,进入 JTAG 配置模式。JTAG 提供以下功能:

- 片外 SPI Flash 编程

- 片内 SRAM 编程

- 片内 eFlash CFM/UFM 后台编程

- 片内 eFlash Elf Attr Option 读写

JTAG 配置使用安路 USB 下载线,配合 TD 软件进行,可以通过软件查看配置状态。ELF 芯片的 TDI,TDO,TMS,TCK 是复用引脚。在 Elf Attr option 中设置

JTAG\_PIN\_PERSISTN=Disable,TDI,TDO,TMS,TCK 在用户模式做用户 IO 使用,在这种情况下,如果需要继续使用 JTAG 接口,可以使用 JTAGEN 引脚控制,拿回 JTAG 引脚的控制权。

#### 2.5.7 OTP 功能

用户可根据使用需求对 CFM/UFM/SRAM/ATTR 设定一次性可编程。通过设置 Elf Attroption 中 CFM\_OTP, UFM\_OTP, SRAM\_OTP 和 ATTR\_OTP 属性来实现,设置后对应块的数据不能被擦除或改写。

#### 2.5.8 上电延迟

ELF CPLD 有 50ms , 5ms 和 0.05ms 3 档上电延迟选择。用户可通过设置 Elf Attr option 中 POR\_Delay 属性来实现 , 默认为 0.05ms。

#### 2.5.9 保密配置选项

ATTR\_SEC: Elf Attr option 决定了 ELF CPLD 的配置功能和安全设置,其中 ATTR\_SEC=Yes 时将禁止读取 Elf Attr option 中的数据。

DNA: ELF CPLD 引入 DNA 功能,每颗 ELF CPLD 器件有一个 42 位唯一 ID。这 42 位 ID中有 34 位是不可改变的,在生产时决定。另外的 8 了位是 Elf Attr option中 DNA\_MSB,由用户决定。TD 软件提供读取 DNA的 IP,用户可以通过对比 DNA 和用户应用中的数据,来对用户的应用进行保护。

用户配置安全选项: 当用户分别设置了 SRAM 和 CFM 的安全选项后, SRAM 和 CFM 的读操作被禁止。如果用户同时设置了 UFM 的安全选项后, UFM 的读操作也被禁止。ELF CPLD 必须在 eFlash 被擦除后才能重置用户配置安全选项。

#### 2.5.10 内部振荡器

ELF CPLD 内部有 OSC 振荡器,主要是用于程序加载使用。该 OSC 输出经过一个分频器后,也可供用户使用。用户可以通过调用库 IP ELF\_PHY\_OSC 来使用该时钟。该 IP 的原型如下:

```

module ELF_PHY_OSC (osc_dis, osc_clk);

```

input osc\_dis;

output osc\_clk;

parameter FREQ = "60"; // 60, 30 MHz

从模型可以看出该 IP 可以输出 30MHz 和 60MHz 两个时钟频率,频率选择通过 parameter 参数确定。该时钟的频率精度不高,大概为±30%,所以该时钟不可作为通信,定时等使用。

该模块的端口有两个信号, osc\_dis 指定时钟使能, 1 代表使能输出; osc\_clk 是 OSC 分频器的输出,可以直接供用户逻辑使用。

endmodule

## 2.5.11 配置接口 IP

ELF\_UFM\_IP: TBD

ELF\_DNA\_IP: TBD

## 3 直流和交流特性

如无特殊说明,以下信息适用于:同一商业和工业级别规定的交流和直流特性。所有参数均为电压对地时的值。

## 3.1 直流电气特性

#### 3.1.1 最大绝对额定值

表 3-1 最大绝对额定值

| Symbol              | 参数         | 最小   | 最大    | 单位 |

|---------------------|------------|------|-------|----|

| VCCEXT              | 辅助电源       | -0.5 | 3.75  | V  |

| V <sub>CCIO</sub>   | I/O驱动供电电压  | -0.5 | 3.75  | V  |

| VI                  | 直流输入电压     | -0.5 | 3.75  | V  |

| V <sub>ESDHBM</sub> | 人体模型静电放电电压 | 1    | ±2000 | V  |

| V <sub>ESDCDM</sub> | 机器模型静电放电电压 | 7    | ±200  | V  |

| T <sub>STG</sub>    | 存储温度       | -65  | 150   | ℃  |

| Тл                  | 结点温度       | -40  | 125   | °C |

超过以上最大绝对额定值可能会导致器件永久性损坏。这些值仅表示在该额定值下操作不会损坏器件,但不表示器件在此极限值下功能正常。器件的功能性操作或基于此的任何条件最大绝对额定值可能会造成器件永久损坏。器件长期在极值条件下运行,会严重的影响器件的可靠性。

#### 3.1.2 推荐基本操作条件

表 3-2 ELF 推荐基本操作条件 1

| Symbol              | 参               | 最小     | 典型      | 最大              | 单位                |            |

|---------------------|-----------------|--------|---------|-----------------|-------------------|------------|

| $V_{CCEXT}^2$       | 辅助电源            | 2.25   | 2.5/3.3 | 3.465           | V                 |            |

|                     | I/O供电电压 @       | 3.3V   | 3.135   | 3.3             | 3.465             | V          |

|                     | I/O供电电压 @       | 2.5V   | 2.375   | 2.5             | 2.625             | V          |

| $V_{\text{CCIO}^3}$ | I/O供电电压 @ 1.8V  |        | 1.71    | 1.8             | 1.89              | V          |

|                     | I/O供电电压 @ 1.5V  |        | 1.425   | 1.5             | 1.575             | V          |

|                     | I/O供电电压 @       | 1.2V   | 1.14    | 1.2             | 1.26              | V          |

| $V_{\rm I}$         | 直流输入电压          | 直流输入电压 |         |                 | 3.6               | V          |

| $V_{O}$             | 输出电压            | N-K    | 0       | <b>&gt;</b> \ - | V <sub>CCIO</sub> | V          |

| Tı                  | 结点温度            | 商业     | 0       | -               | 85                | $^{\circ}$ |

| .,                  | 工业              |        | -40     | ı               | 100               | $^{\circ}$ |

| T <sub>RAMP</sub>   | 电源缓变率           |        | 10      | -               | 100               | V/ms       |

| $I_{Diode}$         | PCI-clamp 二极管电流 |        | -       | -               | 10                | Ма         |

- 1. 器件工作时要求所有 I/O 的 Vccio 必须连接好电源

- 2. 器件工作时要求 Vccext 必须连接好电源

- 3. 所有输入输出缓冲器由 Vccio 供电

#### 3.1.3 静态供电电流 1,2

表 3-3 静态电源电流

| Symbol              | 参数                                | 器件      | 典型  | 单位 |

|---------------------|-----------------------------------|---------|-----|----|

| I <sub>VCCEXT</sub> | 拉心中语                              | ELF-300 | 3   | Ма |

| TVCCEXT             | 核心电源                              | ELF-650 | 3   | Ma |

| I <sub>VCCIO</sub>  | I/O 组电源, @V <sub>CCIO</sub> =2.5V | ELF-300 | 0.6 | Ma |

| 1VCCIO              | 170 記名(M)( W VCCIO-2.3V           | ELF-650 | 0.6 | Ma |

- 1. 该表中的数值基于通用的推荐操作条件,室温下(T」=25℃)使用典型器件测得。

- 2. 典型值为空白器件,没有输出电流负载,高阻抗状态下,并当所有上拉/下拉电阻器在 I/O 引脚禁止时,测量的所有 I/O 驱动的静态电源电流。

## 3.1.4 热插拔规格

表 3-4 热插拔规格 1

| Symbol                 | 参数          | 最大 | 单位 |

|------------------------|-------------|----|----|

| I <sub>IOPIN(DC)</sub> | DC电流,每个I/O  | 1  | Ma |

| Iopin(ac)              | AC电流, 每个I/O | 81 | Ма |

1. 电源缓变率等于或大于 10ns。

## 3.1.5 上电复位电压阈值

表 3-5 上电复位电压阈值

27

| Symbol                   | 参数                        | 最小   | 典型  | 最大   | 单位 |

|--------------------------|---------------------------|------|-----|------|----|

| V <sub>CCEXT_PORUP</sub> | V <sub>CCEXT</sub> 上电检测阈值 | 1.95 | 2.0 | 2.05 | V  |

| VCCEXT_PORDN             | Vccexт掉电检测阈值              | -    | -   | 1.8  | V  |

## 3.1.6 I/O 直流电气特性

## 表 3-6 ELF 推荐基本操作条件

| Symbol                            | 参数          | 条件                                            | 最小            | 典型  | 最大                   | 单位 |

|-----------------------------------|-------------|-----------------------------------------------|---------------|-----|----------------------|----|

| I <sub>IL</sub> , I <sub>IH</sub> | 输入漏电电流      | 0≦V <u>I</u> ≦V <sub>CCIO</sub> -0.5V         | -10           | -   | 10                   | Ua |

| $I_{\mathrm{IH}}$                 | 输入漏电电流      | $V_{CCIO}$ -0.5 $V \le V_{I} \le V_{IH\_MAX}$ | -             | -   | 150                  | Ua |

| ${ m I}_{ m PU}$                  | I/O 弱上拉电流   |                                               | 35            | -   | 250                  | Ua |

| $I_{PD}$                          | I/O 弱下拉电流   |                                               | 35            | 7   | 250                  | Ua |

| I <sub>BHLS</sub>                 | 总线保持0维持电流   |                                               | 40            |     | 7                    | Ua |

| I <sub>BHHS</sub>                 | 总线保持1维持电流   |                                               | 40            | -   | -                    | Ua |

| $I_{BHLO}$                        | 总线保持 0 改写电流 | 0≦V <sub>I</sub> ≦V <sub>CCIO</sub>           | X_            | -   | 350                  | Ua |

| $I_{BHHO}$                        | 总线保持1改写电流   | 0≦V <sub>I</sub> ≦V <sub>CCIO</sub>           | -/            | -   | 350                  | Ua |

| $V_{BHT}$                         | 总线保持触发电平    | (1 <del>.</del> K)                            | $V_{IL\_max}$ | -   | $V_{\text{IH\_min}}$ | V  |

|                                   |             | V <sub>CCIO</sub> =3.3V,HYST=Large            | -             | 500 | -                    | Mv |

|                                   |             | V <sub>CCIO</sub> =3.3V,HYST=Small            | -             | 250 | -                    | Mv |

|                                   | 4           | V <sub>CCIO</sub> =2.5V,HYST=Large            | -             | 400 | -                    | Mv |

| $V_{HYST}$                        | 施密特触发器      | V <sub>CCIO</sub> =2.5V,HYST=Small            | -             | 200 | -                    | Mv |

| <b>V</b> HYS1                     | 输入磁滞        | V <sub>CCIO</sub> =1.8V,HYST=Large            | -             | 350 | -                    | Mv |

|                                   | AHAY        | V <sub>CCIO</sub> =1.8V,HYST=Small            | -             | 170 | -                    | Mv |

|                                   |             | V <sub>CCIO</sub> =1.5V,HYST=Large            | -             | 380 | -                    | Mv |

| 7/                                |             | V <sub>CCIO</sub> =1.5V,HYST=Small            | -             | 190 | -                    | Mv |

## 3.1.7 I/O 管脚电容

表 3-7 ELF 器件管脚电容

| Symbol            | 参数       | QFP | FBGA | 单位 |

|-------------------|----------|-----|------|----|

| Сіотв             | 上下管脚输入电容 | 7   | 6    | Pf |

| C <sub>IOLR</sub> | 左右管脚输入电容 | 8   | 7    | Pf |

## 3.1.8 差分 I/O 电学特性

表 3-8 推荐差分操作条件

| 参数                                | 描述     | 测试条件                   | 最小   | 典型  | 最大   | 单位 |

|-----------------------------------|--------|------------------------|------|-----|------|----|

| V <sub>IP</sub> , V <sub>IN</sub> | 输入电平   | V <sub>CCIO</sub> =2.5 | 0    | -   | 2.4  | V  |

| V <sub>ID</sub>                   | 输入差分摆幅 |                        | 100  | 350 | 800  | Mv |

| V <sub>ICM</sub>                  | 输入共模电压 | V <sub>CCIO</sub> =2.5 | 0.05 | -   | 2.35 | V  |

| $I_{\mathrm{IN}}$                 | 输入电流   | 上电过程                   | -    | -   | ±15  | Ua |

## 3.1.9 单端 I/O 直流电学特性

表 3-9 ELF 器件单端 I/O 标准规格

| 标准                  | V <sub>IL</sub> (V)                                             |                           | V <sub>IH</sub> (V)    |                             | V <sub>OL</sub> 最大      | V <sub>OH</sub> 最小      | I <sub>OL</sub>           | I <sub>OH</sub>                |

|---------------------|-----------------------------------------------------------------|---------------------------|------------------------|-----------------------------|-------------------------|-------------------------|---------------------------|--------------------------------|

| 初/庄                 | 最小                                                              | 最大                        | 最小                     | 最大                          | (V)                     | (V)                     | (mA)                      | (mA)                           |

| LVTTL33<br>LVCMOS33 | -0.3                                                            | 0.8                       | 1.9                    | Vccio+0.3                   | 0.4                     | V <sub>CCIO</sub> – 0.4 | 4<br>8<br>12<br>16<br>0.1 | -4<br>-8<br>-12<br>-16<br>-0.1 |

|                     |                                                                 |                           |                        |                             | 0.2                     | V <sub>CCIO</sub> – 0.2 |                           |                                |

| LVCMOS25            | -0.3                                                            | 0.7                       | 1.7                    | Vccio+0.3                   | 0.4                     | V <sub>CCIO</sub> – 0.4 | 4<br>8<br>10              | -4<br>-8<br>-10                |

| LVCIVIOS25          | -0.5                                                            | -0.3                      | 1.7                    | VCCIO+0.3                   |                         |                         | 12                        | -12                            |

|                     |                                                                 |                           |                        | 12                          | 0.2                     | V <sub>CCIO</sub> – 0.2 | 0.1                       | -0.1                           |

| LVCMOS18            | -0.3                                                            | 0.35*V <sub>CCIO</sub>    | 0.65*V <sub>CCIO</sub> | Vccio+0.3                   | 0.4                     | V <sub>CCIO</sub> – 0.4 | 4<br>6<br>8               | -4<br>-6<br>-8                 |

|                     | V                                                               | 1                         |                        |                             | 0.2                     | V <sub>CCIO</sub> – 0.2 | 0.1                       | -0.1                           |

| LVCMOS15            | -0.3                                                            | 0.35*V <sub>CCIO</sub>    | 0.65*V <sub>CCIO</sub> | Vccio+0.3                   | 0.4                     | V <sub>CCIO</sub> – 0.4 | 3                         | -3<br>-6                       |

|                     |                                                                 | ( Y                       |                        | 0.2                         | V <sub>CCIO</sub> – 0.2 | 0.1                     | -0.1                      |                                |

| 1/                  | LVCMOS12 -0.3 0.35*V <sub>CCIO</sub> 0.65*V <sub>CCIO</sub> VCC |                           | 0.4                    | 0.4 V <sub>CCIO</sub> – 0.4 | 2                       | -2                      |                           |                                |

| LVCMOS12            |                                                                 | 0.65*V <sub>CCIO</sub> VC | Vccio+0.3              |                             |                         | 4                       | -4                        |                                |

|                     |                                                                 |                           |                        |                             | 0.2                     | V <sub>CCIO</sub> – 0.2 | 0.1                       | -0.1                           |

| PCI33               | -0.3                                                            | 0.3*V <sub>CCIO</sub>     | 0. 5*V <sub>CCIO</sub> | Vccio+0.3                   | 0.1*V <sub>CCIO</sub>   | 0.9*V <sub>CCIO</sub>   | 1.5                       | -0.5                           |

| PCIX33              | -0.3                                                            | 0.35*V <sub>CCIO</sub>    | 0. 5*V <sub>CCIO</sub> | Vccio+0.3                   | 0.1*V <sub>CCIO</sub>   | 0.9*V <sub>CCIO</sub>   | 1.5                       | -0.5                           |

## 3.2 交流电气特性

本章节提供 ELF 核心和周边模块的性能参数,时序参数及其典型值是常规的设计重要参数,也是器件的基本性能参数。这些参数反映了器件在最差条件下的实际性能。

## 3.2.1 时钟性能

表 3-10 推荐的时钟操作频率

| 器件          |     | 性能  |     | 单位  |

|-------------|-----|-----|-----|-----|

| AA I I      | 3   | 4   | 5   |     |

| ELF-300/650 | 300 | 250 | 200 | MHz |

#### 3.2.2 I/O 接口性能

表 3-11 I/O 接口性能

| 输入/输出标准   | 描述                             | 最大  | 单位  |

|-----------|--------------------------------|-----|-----|

| 最大输入频率    |                                | •   | •   |

| LVPECL33  | LVPECL, Emulated, VCCIO = 3.0V | 150 | MHz |

| LVDS25    | LVDS, VCCIO = 2.5V             | 300 | MHz |

| LVTTL33   | LVTTL, VCCIO = 3.3V            | 150 | MHz |

| LVCMOS33  | LVCMOS, VCCIO = 3.3V           | 150 | MHz |

| LVCMOS25  | LVCMOS, VCCIO = 2.5V           | 150 | MHz |

| LVCMOS18  | LVCMOS, VCCIO = 1.8V           | 120 | MHz |

| LVCMOS15  | LVCMOS, VCCIO = 1.5V           | 100 | MHz |

| LVCMOS12  | LVCMOS, VCCIO = 1.2V           | 70  | MHz |

| PCI33     |                                | 66  | MHz |

| 最大输出频率    |                                | •   |     |

| LVPECL33E | LVPECL, Emulated, VCCIO = 3.0V | 150 | MHz |

| LVTTL33   | LVTTL, VCCIO = 3.3V            | 150 | MHz |

| LVCMOS33  | LVCMOS, VCCIO = 3.3V           | 150 | MHz |

| LVCMOS25  | LVCMOS, VCCIO = 2.5V           | 150 | MHz |

| LVCMOS18  | LVCMOS, VCCIO = 1.8V           | 125 | MHz |

| LVCMOS15  | LVCMOS, VCCIO = 1.5V           | 100 | MHz |

| LVCMOS12  | LVCMOS, VCCIO = 1.2V           | 70  | MHz |

| PCI33     |                                | 66  | MHz |

## 3.2.3 配置模块和 JTAG 规格

## 表 3-12 ELF 器件下载模式规格

| 下载模式             | 最小  | 典型 | 最大 | 单位  |

|------------------|-----|----|----|-----|

| 主模式串行 SPI (MSPI) | 2.5 | -  | 20 | MHz |

| JTAG             | -   | 10 | -  | MHz |

## 表 3-13 ELF 器件 JTAG 时序规格

| 符号                    | 参数                 | 最小 | 最大 | 单位 |

|-----------------------|--------------------|----|----|----|

| t <sub>JCP</sub>      | TCK 周期             | 40 | _  | ns |

| t <sub>JCH</sub>      | TCK 高电平时间          | 20 | -  | ns |

| t <sub>JCL</sub>      | TCK 低电平时间          | 20 | -  | ns |

| t <sub>JPSU_TDI</sub> | TDI 建立时间           | 1  | -  | ns |

| t <sub>JPSU_TMS</sub> | TMS 建立时间           | 3  | -  | ns |

| t <sub>JPH</sub>      | JTAG 端口保持时间        | 10 | -  | ns |

| t <sub>JPCO</sub>     | JTAG 端口时钟到输出延时     | -  | 15 | ns |

| t <sub>JPZX</sub>     | JTAG 端口有效输出到高阻转换时间 | -  | 15 | ns |

| t <sub>JPXZ</sub>     | 抓取寄存器建立时间          | -  | 15 | ns |

| tussu                 | 抓取寄存器保持时间          | 5  | -  | ns |

| t <sub>JSH</sub>      | 更新寄存器建立时间          | 10 | -  | ns |

| t <sub>JSCO</sub>     | 更新寄存器时钟到输出延时       | -  | 25 | ns |

| t <sub>JSZX</sub>     | 更新寄存器高阻到有效输出       | -  | 25 | ns |

| t <sub>JSXZ</sub>     | 更新寄存器有效输出到高阻       | -  | 25 | ns |

# 4.1 引脚定义和规则

表 4-1 引脚定义规则

| 引脚名称               | 方向   | 描述                                            |

|--------------------|------|-----------------------------------------------|

| 普通 I/O             |      |                                               |

| IO,[DIFFIO_][E     | I/O  | [Edge] 表示管脚所在的边。包括 L/R/T/B                    |

| dge][Num]          |      | [Num] 表示 I/O 在所在边的编号                          |

| [p/n]              |      | [p/n] 表示 I/O 差分极性                             |

| NC                 | -    | 无连接。                                          |

| GND                | -    | 电源地。建议所有的电源地接在一起。                             |

| V <sub>CCIOx</sub> | -    | I/O 组电源。建议同一 I/O 组所有的电源接在一起。                  |

| V <sub>CCEXT</sub> | -    | 核心逻辑电源。                                       |

| 配置复用引脚             |      |                                               |

| TCK                | 输入   | TCK 输入边界扫描时钟。                                 |

| TDI                | 输入   | 边界扫描数据输入。                                     |

| TDO                | 输出   | 边界扫描数据输出。                                     |

| TMS                | 输入   | 边界扫描模式选择。                                     |

| JTAGEN             | 输入   | JTAG 权限控制脚,如果 JTAG 脚设为复用:                     |

|                    | 1837 | JTAGEN=1, JTAG 脚激活 , JTAGEN=0, JTAG 脚作为普通 IO。 |

| PROGRAMN           | 输入   | 全局复位输入,低有效。                                   |

| DONE               | 双向   | 专用配置状态引脚,在配置完成后会输出高,源端开漏。                     |

| INITN              | 双向   | 专用配置状态引脚,输出高表示准备好配置,源端开漏。                     |

| SCLK               | 输出   | MSPI 下载模式时钟输出。                                |

| SPICSN             | 输出   | MSPI 下载模式片选。                                  |

| MISO               | 输入   | MSPI 下载模式 CPLD 数据输入,Flash 数据输出。               |

| MOSI               | 输出   | MSPI 下载模式 CPLD 数据输出,Flash 数据输入。               |

# 4.2 电源电压管脚

|          | Power  | EF1A300           | EF1A650           | EF1L300                   | EF1L650                 |  |  |

|----------|--------|-------------------|-------------------|---------------------------|-------------------------|--|--|

|          | VCCEXT | 13,63             | 13,39,63,88       | 35,90                     | 35,90                   |  |  |

|          | VCCIO0 | NA                | NA                | 60,74,92                  | 80,92                   |  |  |

| 100 TQFP | VCCIO1 | 9,31,45           | 9,31,45           | 10,24,41                  | 60,74                   |  |  |

| 100 TQFP | VCCIO2 | 59,80,94          | 59,80,94          | NA                        | 29,41                   |  |  |

|          | VCCIO3 | NA                | NA                | NA                        | 10,24                   |  |  |

|          | VSSIO  | 10,32,46,60,79,93 | 10,32,46,60,79,93 | 12,25,42,62,75,93         | 12,25,30,42,62,75,81,93 |  |  |

|          | GND    | 11,65             | 11,37,65,90       | 40,84                     | 40,84                   |  |  |

|          | Power  | EF1/              | A650              | /                         | F1L650                  |  |  |

|          | VCCEXT | 19,56,9           | 90,126            | 21,52,93,129              |                         |  |  |

|          | VCCIO0 | N                 | A                 | 117135                    |                         |  |  |

| 144 TQFP | VCCIO1 | 9,25,             | 46,64             | 82,98                     |                         |  |  |

| 144 (Q)  | VCCIO2 | 821003            | 116136            | 38,63                     |                         |  |  |

|          | VCCIO3 | N                 | A                 | 10,26                     |                         |  |  |

|          | VSSIO  | 10,26,47,65,8     | 33,99,115,135     | 11,27,37,64,83,99,118,136 |                         |  |  |

|          | GND    | 17,54,            | 92,128            | 16,5                      | 16,59,88,123            |  |  |

# 4.3 EL1L300、EL1F650 引脚说明

### **4.3.1** LQFP100

| 编号 | BANK | 引脚说明      |     | 编号 | BANK | 引脚说明        |

|----|------|-----------|-----|----|------|-------------|

| 1  | 3    | Ю         |     | 31 | 2    | IO,TDO      |

| 2  | 3    | Ю         |     | 32 | 2    | IO,SCLK     |

| 3  | 3    | Ю         |     | 33 | 2    | IO,TDI      |

| 4  | 3    | Ю         |     | 34 | 2    | IO,MOSI     |

| 5  | 3    | Ю         |     | 35 | 2    | VCCEXT      |

| 6  | 3    | Ю         |     | 36 | 2    | IO,GCLK5    |

| 7  | 3    | Ю         |     | 37 | 2    | IO          |

| 8  | 3    | Ю         |     | 38 | 2    | IO,GCLK4    |

| 9  | 3    | Ю         |     | 39 | 2    | IO          |

| 10 | 3    | VCCIO3    |     | 40 | 2    | GND         |

| 11 | 3    | Ю         |     | 41 | 2    | VCCIO2      |

| 12 | 3    | VSSIO     |     | 42 | 2    | VSSIO       |

| 13 | 3    | Ю         | 7/5 | 43 | 2    | IO          |

| 14 | 3    | IO        |     | 44 | 2    | IO,PROGRAMN |

| 15 | 3    | IO,GCLK7  |     | 45 | 2    | IO,SCL      |

| 16 | 3    | 10        |     | 46 | 2    | IO,SDA      |

| 17 | 3    | 10        |     | 47 | 2    | IO,INITN    |

| 18 | 3    | IO        |     | 48 | 2    | IO,PWRDWN   |

| 19 | 3    | IO        |     | 49 | 2    | IO          |

| 20 | 3    | IO        |     | 50 | 2    | IO,DONE     |

| 21 | 3    | IO        |     | 51 | 1    | IO,LVDSR0N  |

| 22 | 3    | IO        |     | 52 | 1    | IO,LVDSR0P  |

| 23 | 3    | Ю         |     | 53 | 1    | IO,LVDSR1N  |

| 24 | 3    | VCCIO3    |     | 54 | 1    | IO,LVDSR1P  |

| 25 | 3    | VSSIO     |     | 55 | 1    | IO,LVDSR2N  |

| 26 | 2    | IO,TMS    |     | 56 | 1    | IO,LVDSR2P  |

| 27 | 2    | Ю         |     | 57 | 1    | IO,LVDSR3N  |

| 28 | 2    | IO,TCK    |     | 58 | 1    | IO,LVDSR3P  |

| 29 | 2    | IO,MISO   |     | 59 | 1    | IO,LVDSR4N  |

| 30 | 2    | IO,SPICSN |     | 60 | 1    | VCCIO1      |

| 编号 | BANK | 引脚说明               | 编号        | BANK | 引脚说明   |

|----|------|--------------------|-----------|------|--------|

| 61 | 1    | IO,LVDSR4P         | 91        | 0    | Ю      |

| 62 | 1    | VSSIO              | 92        | 0    | VCCIO0 |

| 63 | 1    | IO,LVDSR5N         | 93        | 0    | VSSIO  |

| 64 | 1    | IO,LVDSR5P         | 94        | 0    | Ю      |

| 65 | 1    | IO,GCLKP_2,LVDSR6N | 95        | 0    | 10     |

| 66 | 1    | IO,GCLKP_3,LVDSR6P | 96        | 0    | 10     |

| 67 | 1    | IO,LVDSR7N         | 97        | 0    | IO     |

| 68 | 1    | IO,LVDSR7P         | 98        | 0    | 10     |

| 69 | 1    | IO,LVDSR8N         | 99        | 0    | 10     |

| 70 | 1    | IO,LVDSR8P         | 100       | 0    | 10     |

| 71 | 1    | IO,LVDSR9N         |           | //>  |        |

| 72 | 1    | IO,LVDSR9P         |           | XX   |        |

| 73 | 1    | IO,LVDSR10N        | 7         | VX   |        |

| 74 | 1    | VCCIO1             | <br>X     |      |        |

| 75 | 1    | VSSIO              |           |      |        |

| 76 | 1    | IO,LVDSR10P        | $\lambda$ |      |        |

| 77 | 0    | 10                 | 4         |      |        |

| 78 | 0    | Ю                  |           |      |        |

| 79 | 0    | Ю                  |           |      |        |

| 80 | 0    | IO                 |           |      |        |

| 81 | 0    | IO                 |           |      |        |

| 82 | 0    | 10                 |           |      |        |

| 83 | 0    | IO                 |           |      |        |

| 84 | 0    | GND                |           |      |        |

| 85 | 0    | IO                 |           |      |        |

| 86 | 0    | Ю                  |           |      |        |

| 87 | 0    | Ю                  |           |      |        |

| 88 | 0    | Ю                  |           |      |        |

| 89 | 0    | Ю                  |           |      |        |

| 90 | 0    | VCCEXT             |           |      |        |

|    |      |                    |           |      |        |

|    | ĺ    |                    |           |      |        |

### **4.3.2** LQFP144

| 引脚 | Ю    | 引脚说明     |       | 引脚 | Ю    | 引脚说明      |

|----|------|----------|-------|----|------|-----------|

| 编号 | BANK |          |       | 编号 | BANK |           |

| 1  | 3    | Ю        |       | 31 | 3    | Ю         |

| 2  | 3    | Ю        |       | 32 | 3    | Ю         |

| 3  | 3    | Ю        |       | 33 | 3    | IO        |

| 4  | 3    | Ю        |       | 34 | 3    | 10        |

| 5  | 3    | Ю        |       | 35 | 3    | IO        |

| 6  | 3    | Ю        |       | 36 | 3    | IO        |

| 7  | 3    | Ю        |       | 37 | 2    | VSSIO     |

| 8  | 3    | Ю        |       | 38 | 2    | VCCIO2    |

| 9  | 3    | Ю        |       | 39 | 2    | IO,TMS    |

| 10 | 3    | VCCIO3   |       | 40 | - 2  | Ю         |

| 11 | 3    | VSSIO    |       | 41 | 2    | Ю         |

| 12 | 3    | Ю        |       | 42 | - 2  | IO,TCK    |

| 13 | 3    | Ю        |       | 43 | 2    | IO,MOSI   |

| 14 | 3    | IO       |       | 44 | 2    | IO,SPICSN |

| 15 | 3    | IO       | ` ' ' | 45 | 2    | Ю         |

| 16 | 3    | GND      |       | 46 | 2    | Ю         |

| 17 | 3    | IO       |       | 47 | 2    | IO,TDO    |

| 18 | 3    | IO,GCLK7 |       | 48 | 2    | IO        |

| 19 | 3    | IO       |       | 49 | 2    | IO,SCLK   |

| 20 | 3    | IO,GCLK6 |       | 50 | 2    | IO,MOSI   |

| 21 | 3    | VCCEXT   |       | 51 | 2    | IO,TDI    |

| 22 | 3    | 10       |       | 52 | 2    | VCCEXT    |

| 23 | 3    | IO       |       | 53 | 2    | Ю         |

| 24 | 3    | 10       |       | 54 | 2    | Ю         |

| 25 | 3    | Ю        |       | 55 | 2    | IO,GCLK5  |

| 26 | 3    | VCCIO3   |       | 56 | 2    | Ю         |

| 27 | 3    | VSSIO    |       | 57 | 2    | Ю         |

| 28 | 3    | Ю        |       | 58 | 2    | IO,GCLK4  |

| 29 | 3    | Ю        |       | 59 | 2    | GND       |

| 30 | 3    | Ю        |       | 60 | 2    | Ю         |

| 引脚 | Ю    | 引脚说明             |          | 引脚  | Ю    | 引脚说明             |

|----|------|------------------|----------|-----|------|------------------|

| 编号 | BANK |                  |          | 编号  | BANK |                  |

| 61 | 2    | Ю                |          | 91  | 1    | IO,GCLK3,LVDSR7P |

| 62 | 2    | Ю                |          | 92  | 1    | IO,LVDSR8N       |

| 63 | 2    | VCCIO2           |          | 93  | 1    | VCCEXT           |

| 64 | 2    | VSSIO            |          | 94  | 1    | IO,LVDSR8P       |

| 65 | 2    | Ю                |          | 95  | 1    | IO,LVDSR9N       |

| 66 | 2    | IO,PROGRAMN      |          | 96  | 1    | IO,LVDSR9P       |

| 67 | 2    | IO,SCL           |          | 97  | 1    | IO,LVDSR10N      |

| 68 | 2    | IO,SDA           |          | 98  | 1    | VCCIO1           |

| 69 | 2    | IO,INIT          |          | 99  | 1    | VSSIO            |

| 70 | 2    | IO,PWRDWN        |          | 100 | 1    | IO,LVDSR10P      |

| 71 | 2    | Ю                |          | 101 | 1    | IO,LVDSR11N      |

| 72 | 2    | IO,DONE          |          | 102 | 1    | IO,LVDSR11P      |

| 73 | 1    | IO,LVDSR0N       |          | 103 | 1    | IO,LVDSR12N      |

| 74 | 1    | IO,LVDSR0P       |          | 104 | 1    | IO,LVDSR12P      |

| 75 | 1    | IO,LVDSR1N       | 7/5      | 105 | 1    | IO,LVDSR13N      |

| 76 | 1    | IO,LVDSR1P       | (1)      | 106 | 1    | IO,LVDSR13P      |

| 77 | 1    | IO,LVDSR2N       |          | 107 | 1    | IO,LVDSR14N      |

| 78 | 1    | IO,LVDSR2P       |          | 108 | 1    | IO,LVDSR14P      |

| 79 | 1    | IO,LVDSR3N       | <b>)</b> | 109 | 0    | Ю                |

| 80 | 1    | IO,LVDSR3P       |          | 110 | 0    | Ю                |

| 81 | 1    | IO,LVDSR4N       |          | 111 | 0    | Ю                |

| 82 | 1 .  | VCCIO1           |          | 112 | 0    | Ю                |

| 83 | 1    | VSSIO            |          | 113 | 0    | Ю                |

| 84 | 1    | IO,LVDSR4P       |          | 114 | 0    | Ю                |

| 85 | 1    | IO,LVDSR5N       |          | 115 | 0    | Ю                |

| 86 | 1    | IO,LVDSR5P       |          | 116 | 0    | Ю                |

| 87 | 1    | IO,LVDSR6N       |          | 117 | 0    | VCCIO0           |

| 88 | 1    | GND              |          | 118 | 0    | VSSIO            |

| 89 | 1    | IO,LVDSR6P       |          | 119 | 0    | Ю                |

| 90 | 1    | IO,GCLK2,LVDSR7N |          | 120 | 0    | Ю                |

|    |      |                  |          |     |      |                  |

| 引脚  | Ю    | 引脚说明      | <br>引脚 | BANK | 引脚说明   |

|-----|------|-----------|--------|------|--------|

| 编号  | BANK |           | 编号     |      |        |

| 121 | 0    | Ю         | 133    | 0    | Ю      |

| 122 | 0    | Ю         | 134    | 0    | Ю      |

| 123 | 0    | GND       | 135    | 0    | VCCIO0 |

| 124 | 0    | IO,GCLK1  | 136    | 0    | VSSIO  |

| 125 | 0    | Ю         | 137    | 0    | IO     |

| 126 | 0    | Ю         | 138    | 0    | IO     |

| 127 | 0    | IO,GCLK0  | 139    | 0    | IO     |

| 128 | 0    | IO,JTAGEN | 140    | 0    | 10     |

| 129 | 0    | VCCEXT    | 141    | 0    | IO     |

| 130 | 0    | Ю         | 142    | 0    | IO     |

| 131 | 0    | Ю         | 143    | 0    | 10     |

| 132 | 0    | Ю         | 144    | 0    | Ю      |

# 4.4 EL1A300、EL1A650 引脚说明

### **4.4.1** LQFP100

| 编号 | BANK | 引脚说明      |     | 编号 | BANK | 引脚说明        |

|----|------|-----------|-----|----|------|-------------|

| 1  | 3    | IO        |     | 31 | 2    | VCCIO2      |

| 2  | 3    | Ю         |     | 32 | 2    | VSSIO       |

| 3  | 3    | Ю         |     | 33 | 2    | IO,SCLK     |

| 4  | 3    | Ю         |     | 34 | 2    | Ю           |

| 5  | 3    | Ю         |     | 35 | 2    | IO,MOSI     |

| 6  | 3    | Ю         |     | 36 | 2    | IO          |

| 7  | 3    | Ю         |     | 37 | 2    | IO,GCLK5    |

| 8  | 3    | Ю         |     | 38 | 2    | Ю           |

| 9  | 3    | VCCIO3    |     | 39 | 2    | IO,GCLK4    |

| 10 | 3    | VSSIO     |     | 40 | 2    | Ю           |

| 11 | 3    | GND       |     | 41 | 2    | IO          |

| 12 | 3    | IO,GCLK7  |     | 42 | 2    | Ю           |

| 13 | 3    | VCCEXT    | 7K  | 43 | 2    | Ю           |

| 14 | 3    | IO,GCLK6  |     | 44 | 2    | Ю           |

| 15 | 3    | 10        |     | 45 | 2    | VCCIO2      |

| 16 | 3    | 10        |     | 46 | 2    | VSSIO       |

| 17 | 3    | IO        | ) ' | 47 | 2    | IO,SCL      |

| 18 | 3    | 10        |     | 48 | 2    | IO,PROGRAMN |

| 19 | 3    | IO        |     | 49 | 2    | IO,SDA      |

| 20 | 3    | IO        |     | 50 | 2    | IO,PWRDWN   |

| 21 | 3    | IO        |     | 51 | 2    | IO,INITN    |

| 22 | 3    | IO,TMS    |     | 52 | 2    | IO,DONE     |

| 23 | 3    | IO,TDI    |     | 53 | 1    | IO,LVDSR0N  |

| 24 | 3    | IO,TCK    |     | 54 | 1    | IO,LVDSR0P  |

| 25 | 3    | IO,TDO    |     | 55 | 1    | IO,LVDSR1N  |

| 26 | 2    | Ю         |     | 56 | 1    | IO,LVDSR1P  |

| 27 | 2    | Ю         |     | 57 | 1    | IO,LVDSR2N  |

| 28 | 2    | IO,SPICSN |     | 58 | 1    | IO,LVDSR2P  |

| 29 | 2    | IO,MISO   |     | 59 | 1    | VCCIO1      |

| 30 | 2    | Ю         |     | 60 | 1    | VSSIO       |

| 编号 | BANK | 引脚说明       | 编号    | BANK | 引脚说明   |

|----|------|------------|-------|------|--------|

| 61 | 1    | Ю          | 91    | 0    | Ю      |

| 62 | 1    | Ю          | 92    | 0    | Ю      |

| 63 | 1    | VCCEXT     | 93    | 0    | VSSIO  |

| 64 | 1    | Ю          | 94    | 0    | VCCIO0 |

| 65 | 1    | GND        | 95    | 0    | 10     |

| 66 | 1    | IO,LVDSR3N | 96    | 0    | 10     |

| 67 | 1    | IO,LVDSR3P | 97    | 0    | IO     |

| 68 | 1    | IO,LVDSR4N | 98    | 0    | 10     |

| 69 | 1    | IO,LVDSR4P | 99    | 0    | 10     |

| 70 | 1    | IO,LVDSR5N | 100   | 0    | 10     |

| 71 | 1    | IO,LVDSR5P |       |      |        |

| 72 | 1    | IO,LVDSR6N |       | XX   | _      |

| 73 | 1    | IO,LVDSR6P | 7     | VK   |        |

| 74 | 1    | IO,LVDSR7N | <br>X |      |        |

| 75 | 1    | IO,LVDSR7P |       |      |        |

| 76 | 0    | Ю          | x.T   |      |        |

| 77 | 0    | Ю          | 1     |      |        |

| 78 | 0    | Ю          |       |      |        |

| 79 | 0    | VSSIO      |       |      |        |

| 80 | 0    | VCCIO0     |       |      |        |

| 81 | 0    | IO         |       |      |        |

| 82 | 0    | 10         |       |      |        |

| 83 | 0    | IO         |       |      |        |

| 84 | 0    | IO         |       |      |        |

| 85 | 0    | IO,GCLK1   |       |      |        |

| 86 | 0    | IO,GCLK0   |       |      |        |

| 87 | 0    | Ю          |       |      |        |

| 88 | 0    | Ю          |       |      |        |

| 89 | 0    | IO,JTAGEN  |       |      |        |

| 90 | 0    | Ю          |       |      |        |

|    |      |            |       |      |        |

|    | ı    |            | L     |      |        |

### **4.4.2** LQFP144

| 引脚 | Ю    | 引脚说明     |           | 引脚 | Ю    | 引脚说明      |

|----|------|----------|-----------|----|------|-----------|

| 编号 | BANK |          |           | 编号 | BANK |           |

| 1  | 3    | Ю        |           | 31 | 3    | Ю         |

| 2  | 3    | Ю        |           | 32 | 3    | Ю         |

| 3  | 3    | Ю        |           | 33 | 3    | IO,TMS    |

| 4  | 3    | Ю        |           | 34 | 3    | IO,TDI    |

| 5  | 3    | Ю        |           | 35 | 3    | IO,TCK    |

| 6  | 3    | Ю        |           | 36 | 3    | IO,TDO    |

| 7  | 3    | Ю        |           | 37 | 2    | IO        |

| 8  | 3    | Ю        |           | 38 | 2    | IO        |

| 9  | 3    | VCCIO3   |           | 39 | 2    | IO        |

| 10 | 3    | VSSIO    |           | 40 | 2    | Ю         |

| 11 | 3    | Ю        |           | 41 | 2    | Ю         |

| 12 | 3    | Ю        |           | 42 | - 2  | IO,MISO   |

| 13 | 3    | Ю        |           | 43 | 2    | IO,SPICSN |

| 14 | 3    | Ю        |           | 44 | 2    | Ю         |

| 15 | 3    | 10       | \ \ \ / / | 45 | 2    | Ю         |

| 16 | 3    | Ю        |           | 46 | 2    | VCCIO2    |

| 17 | 3    | GND      |           | 47 | 2    | VSSIO     |

| 18 | 3    | IO,GCLK7 |           | 48 | 2    | IO        |

| 19 | 3    | VCCEXT   |           | 49 | 2    | IO,SCLK   |

| 20 | 3    | IO,GCLK6 |           | 50 | 2    | Ю         |

| 21 | 3    | IO       |           | 51 | 2    | IO,MOSI   |

| 22 | 3    | 10       |           | 52 | 2    | IO        |

| 23 | 3    | IO       |           | 53 | 2    | IO,GCLKP5 |

| 24 | 3    | 10       |           | 54 | 2    | VSSIO     |

| 25 | 3    | VCCIO3   |           | 55 | 2    | Ю         |

| 26 | 3    | VSSIO    |           | 56 | 2    | VCCEXT    |

| 27 | 3    | Ю        |           | 57 | 2    | IO,GCLK4  |

| 28 | 3    | Ю        |           | 58 | 2    | Ю         |

| 29 | 3    | Ю        |           | 59 | 2    | Ю         |

| 30 | 3    | Ю        |           | 60 | 2    | Ю         |

42

| 引脚 | Ю    | 引脚说明             | 引脚  | BANK | 引脚说明             |

|----|------|------------------|-----|------|------------------|

| 编号 | BANK |                  | 编号  |      |                  |

| 61 | 2    | Ю                | 91  | 1    | IO,GCLK3,LVDSR7P |

| 62 | 2    | Ю                | 92  | 1    | GND              |

| 63 | 2    | Ю                | 93  | 1    | IO,LVDSR8N       |

| 64 | 2    | VCCIO2           | 94  | 1    | IO,LVDSR8P       |

| 65 | 2    | VSSIO            | 95  | 1    | IO,LVDSR9N       |

| 66 | 2    | IO,PROGRAMN      | 96  | 1    | IO,LVDSR9P       |

| 67 | 2    | IO,SCL           | 97  | 1    | IO,LVDSR10N      |

| 68 | 2    | IO,SDA           | 98  | 1    | IO,LVDSR10P      |

| 69 | 2    | IO,INITN         | 99  | 1    | VSSIO            |

| 70 | 2    | IO,PWRDWN        | 100 | 1    | VCCIO1           |

| 71 | 2    | Ю                | 101 | 1    | IO,LVDSR11N      |

| 72 | 2    | IO,DONE          | 102 | 1    | IO,LVDSR11P      |

| 73 | 1    | IO,LVDSR0N       | 103 | 1    | IO,LVDSR12N      |

| 74 | 1    | IO,LVDSR0P       | 104 | 1    | IO,LVDSR12P      |

| 75 | 1    | IO,LVDSR1N       | 105 | 1    | IO,LVDSR13N      |

| 76 | 1    | IO,LVDSR1P       | 106 | 1    | IO,LVDSR13P      |

| 77 | 1    | IO,LVDSR2N       | 107 | 1    | IO,LVDSR14N      |

| 78 | 1    | IO,LVDSR2P       | 108 | 1    | IO,LVDSR14P      |

| 79 | 1    | IO,LVDSR3N       | 109 | 0    | IO               |

| 80 | 1    | IO,LVDSR3P       | 110 | 0    | IO               |

| 81 | 1    | IO,LVDSR4N       | 111 | 0    | IO               |

| 82 | 1 .  | VCCIO1           | 112 | 0    | IO               |

| 83 | 1    | VSSIO            | 113 | 0    | IO               |

| 84 | 1    | IO,LVDSR4P       | 114 | 0    | Ю                |

| 85 | 1    | IO,LVDSR5N       | 115 | 0    | VSSIO            |

| 86 | 1    | IO,LVDSR5P       | 116 | 0    | VCCIO0           |

| 87 | 1    | IO,LVDSR6N       | 117 | 0    | Ю                |

| 88 | 1    | IO,LVDSR6P       | 118 | 0    | Ю                |

| 89 | 1    | IO,GCLK2,LVDSR7N | 119 | 0    | Ю                |

| 90 | 1    | NC               | 120 | 0    | Ю                |

|    |      |                  |     |      |                  |

| 引脚  | Ю    | 引脚说明      | <br>引脚 | BANK | 引脚说明   |

|-----|------|-----------|--------|------|--------|

| 编号  | BANK |           | 编号     |      |        |

| 121 | 0    | Ю         | 133    | 0    | IO     |

| 122 | 0    | Ю         | 134    | 0    | Ю      |

| 123 | 0    | IO,GCLK1  | 135    | 0    | VSSIO  |

| 124 | 0    | IO,GCLK0  | 136    | 0    | VCCIO0 |

| 125 | 0    | Ю         | 137    | 0    | 10     |

| 126 | 0    | VCCEXT    | 138    | 0    | IO     |

| 127 | 0    | I         | 139    | 0    | IO     |

| 128 | 0    | Ю         | 140    | 0    | 10     |

| 129 | 0    | IO,JTAGEN | 141    | 0    | 10     |

| 130 | 0    | Ю         | 142    | 0    | Ю      |

| 131 | 0    | Ю         | 143    | 0    | Ю      |

| 132 | 0    | Ю         | 144    | 0    | Ю      |

### **4.4.3** QFP44

| 编号 | BANK | 引脚说明        |             | 编号 | BANK | 引脚说明     |

|----|------|-------------|-------------|----|------|----------|

| 1  | -    | IO,TDI      |             | 31 | -    | Ю        |

| 2  | -    | Ю           |             | 32 | -    | IO,TDO   |

| 3  | -    | Ю           |             | 33 | -    | Ю        |

| 4  | -    | VSSIO       |             | 34 | -    | IO       |

| 5  | -    | Ю           |             | 35 | -    | 10       |

| 6  | -    | Ю           |             | 36 | -    | GND      |

| 7  | -    | IO,TMS      |             | 37 | -    | IO,GCLK7 |

| 8  | -    | IO,GCLK4    |             | 38 | -    | IO       |

| 9  | -    | VCCIO       |             | 39 |      | IO       |

| 10 | -    | IO,PROGRAMN |             | 40 |      | IO,GCLK6 |

| 11 | -    | GND         |             | 41 |      | VCCEXT   |

| 12 | -    | Ю           |             | 42 | 7-   | 10       |

| 13 | -    | Ю           | < 1.        | 43 | -    | Ю        |

| 14 | -    | Ю           | <b>-</b> X- | 44 | -    | Ю        |

| 15 | -    | Ю           | - / / >     | 4  |      |          |

| 16 | -    | GND         | 入           |    |      |          |

| 17 | -    | VCCEXT      |             | 7  |      |          |

| 18 | -    | IO          |             |    |      |          |

| 19 | -    | 10          |             |    |      |          |

| 20 | -    | IO          |             |    |      |          |

| 21 | -    | 10          |             |    |      |          |

| 22 | -    | IO          |             |    |      |          |

| 23 | -/   | IO          |             |    |      |          |

| 24 | //   | VSSIO       |             |    |      |          |

| 25 | XX   | 10          |             |    |      |          |

| 26 | 7 7  | IO,TCK      |             |    |      |          |

| 27 | -/   | IO,GCLK1    |             |    |      |          |

| 28 | -    | Ю           |             |    |      |          |

| 29 | -    | VCCIO       |             |    |      |          |

| 30 | -    | GND         |             |    |      |          |

### 4.5 封装信息

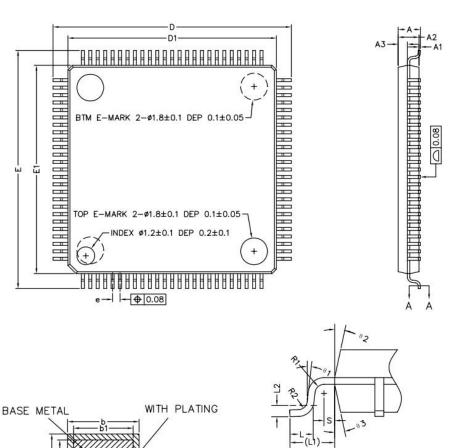

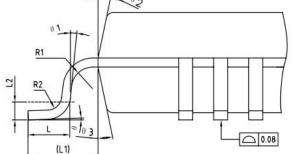

#### 4.5.1 LQFP100 封装规格

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN     | NOM              | MAX              |

|--------|---------|------------------|------------------|

| Α      | 8-8     | -                | 1.60             |

| A1     | 0.05    | e-s              | 0.15             |

| A2     | 1.35    | 1.40             | 1.45             |

| A3     | 0.59    | 0.64             | 0.69             |

| b      | 0.17    | a—a              | 0.27             |

| b1     | 0.17    | 0.20             | 0.23             |

| С      | 0.13    | -                | 0.18             |

| c1     | 0.12    | 0.127            | 0.134            |

| D      | 15.80   | 16.00            | 16.20            |

| D1     | 13.90   | 14.00            | 14.10            |

| E      | 15.80   | 16.00            | 16.20            |

| E1     | 13.90   | 14.00            | 14.10            |

| е      | 0.40    | 0.50             | 0.60             |

| L      | 0.45    | 0.60             | 0.75             |

| L1     | 1.00REF |                  |                  |

| L2     | 0.25BSC |                  |                  |

| R1     | 0.08    | 8 <del>775</del> | X <del>II.</del> |

| R2     | 0.08    | <u></u>          | 0.20             |

| S      | 0.20    | _                | _                |

| θ      | 0.      | 3.5°             | 7.               |

| θ 1    | 0,      | _                | 1=               |

| θ 2    | 11*     | 12°              | 13°              |

| θ 3    | 11°     | 12°              | 13°              |

#### NOTES:

ALL DIMENSIONS REFER TO JEDEC STANDARD MS-026 BED DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

SECTION A-A

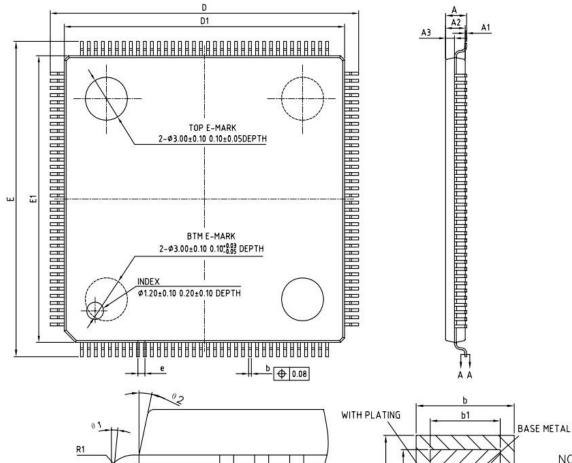

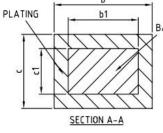

#### 4.5.2 LQFP144 封装规格

# COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN     | NOM     | MAX             |

|--------|---------|---------|-----------------|

| Α      |         | _       | 1.60            |

| A1     | 0.05    | -       | 0.15            |

| A2     | 1.35    | 1.40    | 1.45            |

| A3     | 0.59    | 0.64    | 0.69            |

| b      | 0.17    | _       | 0.27            |

| b1     | 0.17    | 0.20    | 0.23            |

| С      | 0.127   | -       | 0.18            |

| c1     | 0.119   | 0.127   | 0.135           |

| D      | 21.80   | 22.00   | 22.20           |

| D1     | 19.90   | 20.00   | 20.10           |

| E      | 21.80   | 22.00   | 22.20           |

| E1     | 19.90   | 20.00   | 20.10           |

| е      | 0.40    | 0.50    | 0.60            |

| L      | 0.45    | 0.60    | 0.75            |

| L1     |         | 1.00REF |                 |

| L2     | 0.25BSC |         |                 |

| R1     | 0.08    | _       | _               |

| R2     | 0.08    | - TO    | 3 <del>5.</del> |

| θ      | 0.      | -       | 7*              |

| θ1     | 0.      | =       | _               |

| θ 2    | 11'     | 12°     | 13*             |

| θ 3    | 11"     | 12*     | 13°             |

NOTES:

ALL DIMENSIONS REFER TO JEDEC STANDARD MS-026 BFB DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

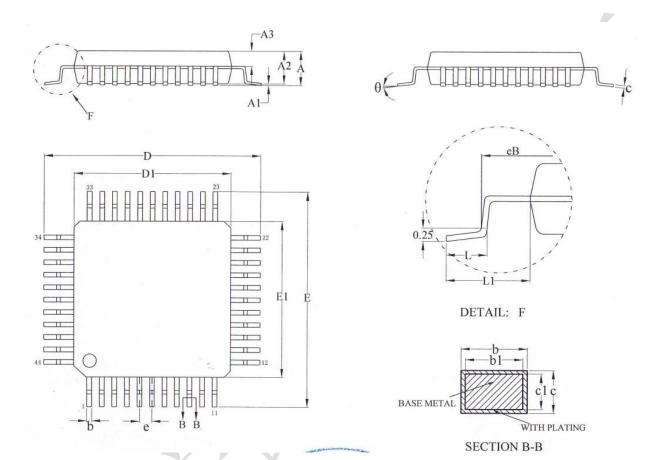

### 4.5.3 QFP44 封装规格

| SYMBOL | MILLIMETER |       |       |  |

|--------|------------|-------|-------|--|

| STMBOL | MIN        | NOM   | MAX   |  |

| A      | _          |       | 2.35  |  |

| A1     | 0.05       | _     | 0.15  |  |

| A2     | 2.05       | 2.10  | 2.15  |  |

| A3     | 0.95       | 1.00  | 1.05  |  |

| b      | 0.28       | _     | 0.36  |  |

| b1     | 0.27       | 0.30  | 0.33  |  |

| c      | 0.15       |       | 0.19  |  |

| c1     | 0.14       | 0.15  | 0.16  |  |

| D      | 13.00      | 13.20 | 13.40 |  |

| D1     | 9.90       | 10.00 | 10.10 |  |

| Е      | 13.00      | 13.20 | 13.40 |  |

| E1     | 9.90       | 10.00 | 10.10 |  |

| eB     | 11.59      | _     | 11.89 |  |

| e      | 0.80BSC    |       |       |  |

| L      | 0.78       | _     | 0.98  |  |

| L1     | 1.60REF    |       |       |  |

| θ      | 0          | _     | プ     |  |

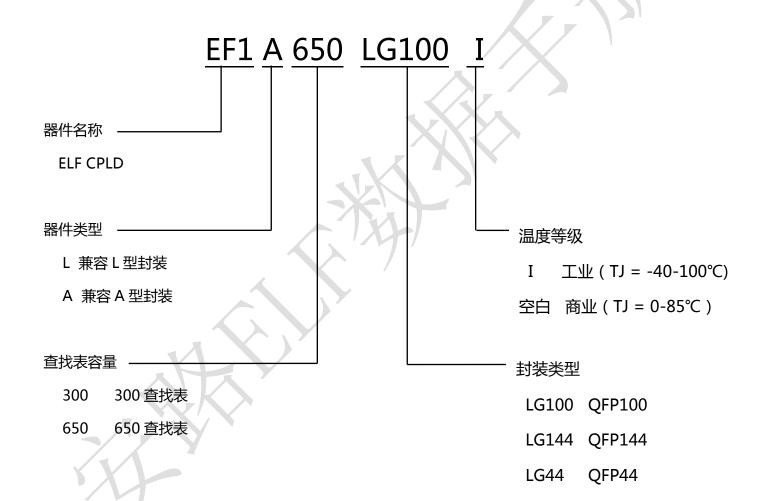

## 5 订购信息

表 5-1 为器件号缩写

| 器件名称 | 器件类型 | 查找表容量   | 封装类型  | 温度等级 |

|------|------|---------|-------|------|

| EF   | L    | 650/300 | LG100 | I    |

DS002 (v1.8) 2018

数据手册

# 6 **版本信息**

| 日期         | 版本  | 修订记录             |

|------------|-----|------------------|

| 02/08/2016 | 1.0 | 首次发布中文版          |

| 05/20/2016 | 1.1 | 补充 100 pin 封装    |

| 06/26/2017 | 1.4 | 修正配置部分错误         |

| 27/11/2017 | 1.5 | 增加 PQFP44 封装     |

| 7/12/2017  | 1.6 | 增加 BANK1 LVDS 输入 |

| 22/1/2018  | 1.7 | 增加 OSC 内部振荡器说明   |

| 2/2/2018   | 1.8 | TQFP 封装改成 LQFP   |