# ADS1013, ADS1014, ADS1015

ZHCSHA6E -MAY 2009-REVISED JANUARY 2018

# 具有内部基准、振荡器和可编程比较器且兼容 I<sup>2</sup>C 的ADS101x超小型低功 耗 3.3kSPS 12 位 ADC

# 1 特性

- 超小型 X2QFN 封装:

2mm × 1.5mm × 0.4mm

- 12 位无噪声分辨率

- 宽电源电压: 2.0V 至 5.5V

- 低流耗: 150μA

(连续转换模式)

- 可编程数据速率: 128SPS 至 3.3kSPS

- 单周期稳定

- 内部低漂移电压基准

- 内部振荡器

- I2C接口: 四个可通过引脚选择的地址

- 四个单端输入或两个差分输入 (ADS1015)

- 可编程比较器(ADS1014 和 ADS1015)

- 工作温度范围:

-40°C 至 +125°C

# 2 应用

- 便携式仪表

- 电池电压和电流监控

- 温度测量系统

- 消费类电子产品

- 工厂自动化和过程控制

# 3 说明

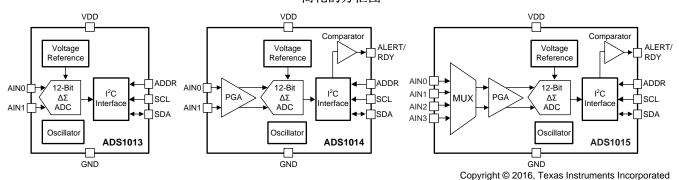

ADS1013、ADS1014 和 ADS1015 器件 (ADS101x) 是兼容 I<sup>2</sup>C 的 12 位高精度低功耗模数转换器 (ADC),采用超小型无引线 X2QFN-10 封装和 VSSOP-10 封装。ADS101x 器件采用了低漂移电压基准和振荡器。ADS1014 和 ADS1015 还采用可编程增益放大器 (PGA) 和数字比较器。这些 特性以及较宽的工作电源电压范围使得 ADS101x 非常合适功率受限和空间受限的传感器测量 应用。

ADS101x 可在数据速率高达每秒 3300 个样本 (SPS) 的情况下执行转换。PGA 可提供从 ±256mV 到 ±6.144V 的输入范围,从而实现精准的大小信号测量。ADS1015 采用 一个输入多路复用器 (MUX),可实现两次差动输入测量或四次单端输入测量。在 ADS1014 和 ADS1015 中可使用数字比较器进行欠压和过压检测。

ADS101x 既可工作于连续转换模式下,也可工作于单冲模式下。在单冲模式下,这些器件可在一次转换后自动断电: 因此显著降低了空闲期间的功耗。

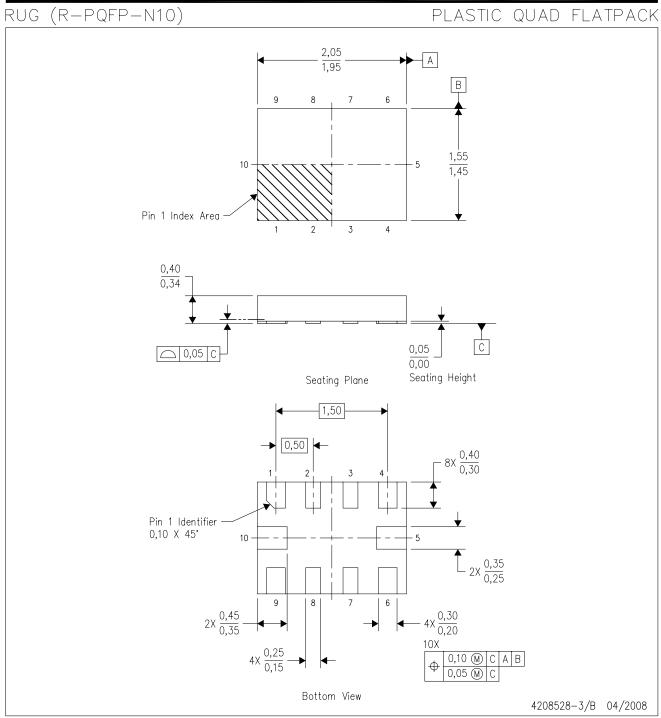

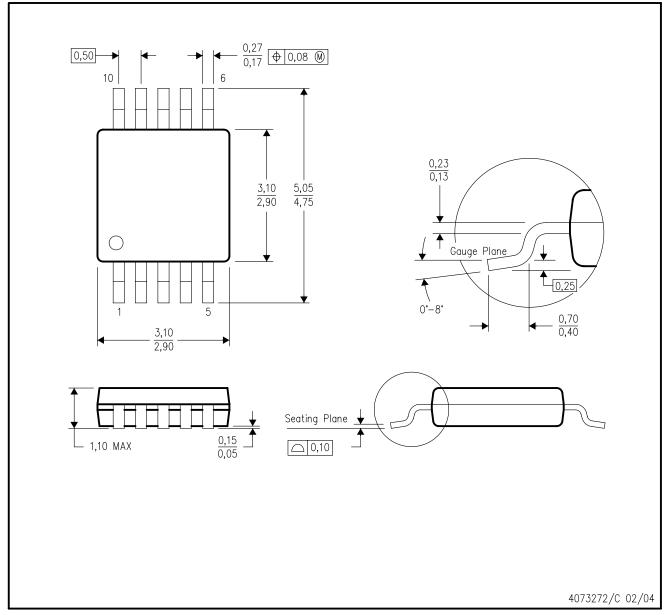

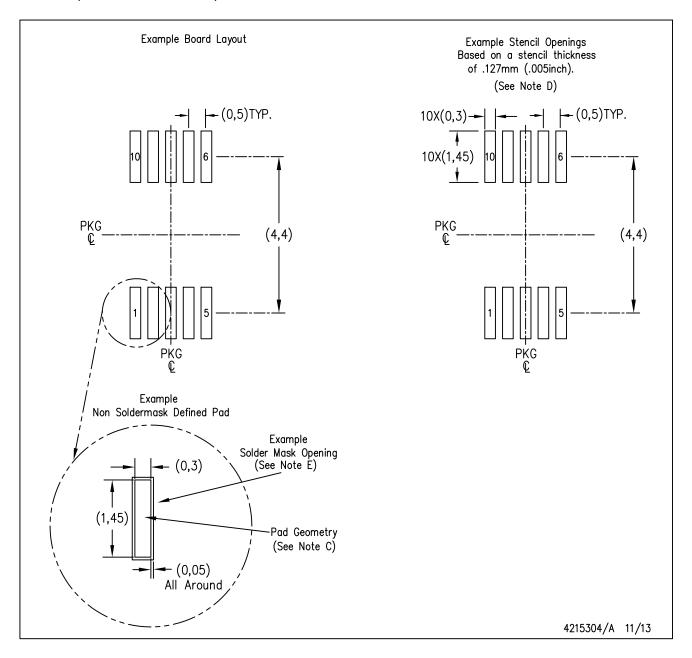

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM) |

|-------------|------------|-----------------|

| ADS101x     | X2QFN (10) | 1.50mm x 2.00mm |

| ADSTOTX     | VSSOP (10) | 3.00mm × 3.00mm |

(1) 要了解所有可用封装,请参见数据表末尾的封装选项附录。

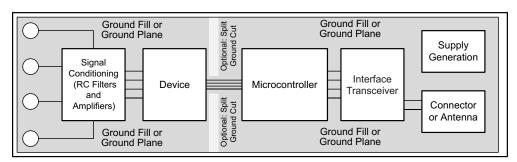

#### 简化的方框图

| 1 | 特性 1                                      |     | 8.6 Register Map                                     | . 22 |

|---|-------------------------------------------|-----|------------------------------------------------------|------|

| 2 | 应用                                        |     | Application and Implementation                       |      |

| 3 | <br>说明                                    |     | 9.1 Application Information                          |      |

| 4 | Revision History2                         |     | 9.2 Typical Application                              | . 31 |

| 5 | Device Comparison Table 4                 | 4.0 | Power Supply Recommendations                         | 35   |

| 6 | Pin Configuration and Functions4          |     | 10.1 Power-Supply Sequencing                         | . 35 |

| 7 | Specifications                            |     | 10.2 Power-Supply Decoupling                         | . 35 |

| • | 7.1 Absolute Maximum Ratings              | 11  | Layout                                               | 36   |

|   | 7.2 ESD Ratings                           |     | 11.1 Layout Guidelines                               | . 36 |

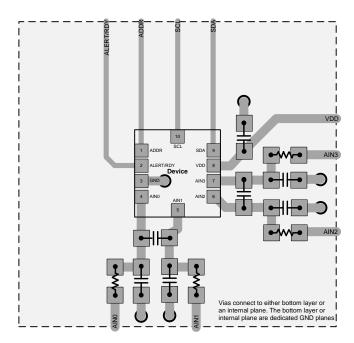

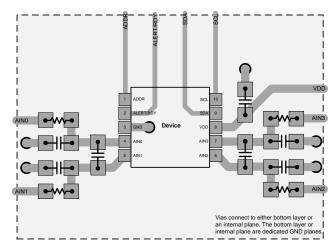

|   | 7.3 Recommended Operating Conditions      |     | 11.2 Layout Example                                  | . 37 |

|   | 7.4 Thermal Information                   | 42  | 器件和文档支持                                              | 38   |

|   | 7.5 Electrical Characteristics            |     | 12.1 Documentation Support                           | . 38 |

|   | 7.6 Timing Requirements: I <sup>2</sup> C |     | 12.2 相关链接                                            | . 38 |

|   | 7.7 Typical Characteristics               |     | 12.3 Receiving Notification of Documentation Updates | 38   |

| 8 | Detailed Description9                     |     | 12.4 Community Resources                             | . 38 |

| • | 8.1 Overview                              |     | 12.5 商标                                              | . 38 |

|   | 8.2 Functional Block Diagrams             |     | 12.6 静电放电警告                                          | . 38 |

|   | 8.3 Feature Description                   |     | 12.7 Glossary                                        |      |

|   | 8.4 Device Functional Modes               | 42  | 机械、封装和可订购信息                                          | . 38 |

|   | 8.5 Programming                           | •   |                                                      |      |

# 4 Revision History

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Revision D (December 2016) to Revision E

Page

| • | Changed Digital input voltage max value from VDD + 0.3 V to 5.5 V in Absolute Maximum Ratings table      | 5  |

|---|----------------------------------------------------------------------------------------------------------|----|

| • | Changed V <sub>DIG</sub> max value from VDD to 5.5 V in <i>Recommended Operating Conditions</i> table    | 5  |

| • | Added "over temperature" to Offset drift parameter for clarity                                           | 6  |

| • | Added Long-term offset drift parameter in Electrical Characteristics table                               | 6  |

| • | Added "over temperature" to Gain drift parameter for clarity                                             | 6  |

| • | Added Long-term gain drift parameter in Electrical Characteristics table                                 | 6  |

| • | Changed V <sub>IH</sub> parameter max value from VDD to 5.5 V in <i>Electrical Characteristics</i> table | 6  |

| • | Added Output Data Rate and Conversion Time section for clarity                                           | 12 |

| • | Changed Figure 13, ALERT Pin Timing Diagram for clarity                                                  | 14 |

| • | Changed Figure 24, Typical Connections of the ADS1015 for clarity                                        | 26 |

| • | Changed resistor values in Figure 28, Basic Hardware Configuration, from 10 Ω to 10 kΩ                   | 30 |

# Changes from Revision C (October 2009) to Revision D

**Page**

| • | 已添加 增加了器件信息、ESD 额定值、建议运行条件和热性能信息表以及参数测量信息、详细 说明、应用和实施、<br>电源建议、布局、器件和文档支持部分                          | . 1 |

|---|------------------------------------------------------------------------------------------------------|-----|

| • | 已更改 更改了标题和说明、特性和应用部分,以便辨别                                                                            |     |

| • | 己删除 从说明部分删除了温度范围文字并移到特性部分                                                                            | . 1 |

| • | Changed Product Family table title to Device Comparison Table and deleted Package Designator column  | . 4 |

| • | Changed Pin Functions table for clarity                                                              | . 4 |

| • | Changed Power-supply voltage max value from 5.5 V to 7 V in Absolute Maximum Ratings table           | . 5 |

| • | Changed Analog input voltage from -0.3 V to GND - 0.3 V in Absolute Maximum Ratings table            | . 5 |

| • | Changed Digital input voltage min value from -0.5 V to GND - 0.3 V in Absolute Maximum Ratings table | . 5 |

| • | Changed Digital input voltage max value from 5.5 V to VDD + 0.3 V in Absolute Maximum Ratings table  | . 5 |

|   |                                                                                                      |     |

#### www.ti.com.cn

| •  | Deleted Analog input current rows in Absolute Maximum Ratings table                                                                                                                                                                                                    | 5              |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •  | Added Input current row in Absolute Maximum Ratings table                                                                                                                                                                                                              | 5              |

| •  | Added Operating temperature range of -40°C to +125°C back into Absolute Maximum Ratings table                                                                                                                                                                          | 5              |

| •  | Added minimum specification of -40°C for T <sub>J</sub> in <i>Absolute Maximum Ratings</i> table                                                                                                                                                                       | 5              |

| •  | Changed Electrical Characteristics table conditions line for clarity                                                                                                                                                                                                   | 6              |

| •  | Changed all instances of "FS" to "FSR"                                                                                                                                                                                                                                 | 6              |

| •  | Deleted FSR from Electrical Characteristics and moved to Recommended Operating Conditions table                                                                                                                                                                        | 6              |

| •  | Added values from Table 2 to Differential input impedance parameter in Electrical Characteristics                                                                                                                                                                      | 6              |

| •  | Deleted Output noise parameter from Electrical Characteristics                                                                                                                                                                                                         |                |

| •  | Changed Offset error empty min value to -0.5, and max value from ±0.5 to 0.5 for clarity in Electrical Characteristics table                                                                                                                                           |                |

| •  | Changed V <sub>IH</sub> parameter max value from 5.5 V to VDD in <i>Electrical Characteristics</i> table                                                                                                                                                               | 6              |

| •  | Changed V <sub>IL</sub> parameter min value from GND – 0.5 V to GND in <i>Electrical Characteristics</i> table                                                                                                                                                         |                |

| •  | Changed <i>Input leakage current</i> parameters from two rows to one row, changed test conditions from $V_{IH} = 5.5V$ and $V_{IL} = GND$ to $GND < V_{DIG} < VDD$ , and changed min value from 10 $\mu$ A to $-10$ $\mu$ A in <i>Electrical Characteristics</i> table | 6              |

| •  | Deleted Power-supply voltage parameter from Electrical Characteristics and moved to Recommended Operating Conditions table                                                                                                                                             | 6              |

| •  | Deleted Specified temperature parameter from Electrical Characteristics and moved to Recommended Operating Conditions table                                                                                                                                            | 6              |

| •  | Deleted Storage temperature parameter from Electrical Characteristics to Absolute Maximum Ratings table                                                                                                                                                                | 6              |

| •  | Deleted Operating temperature parameter from Temperature section of Electrical Characteristics table                                                                                                                                                                   | 6              |

| •  | Changed text in note 1 of <i>Electrical Characteristics</i> table from "In no event should more than VDD + 0.3 V be applied to this device" to "No more than VDD + 0.3 V must be applied to the analog inputs of the device. See Table 1 for more information."        | 6              |

| •  | Added condition statement in <i>Timing Requirements: PC</i>                                                                                                                                                                                                            | <mark>7</mark> |

| •  | Added note 1 to Timing Requirements table                                                                                                                                                                                                                              | <mark>7</mark> |

| •  | Deleted Figure 7, Noise Plot                                                                                                                                                                                                                                           | 8              |

| •  | Changed Figure 8; deleted "Gain = 2/3, 1, 2, 4, 8, or 16" from figure                                                                                                                                                                                                  | 9              |

| •  | Added Functional Block Diagrams for ADS1014 and ADS1013                                                                                                                                                                                                                | 9              |

| •  | Changed Analog Inputs section to provide LSB size information instead of PGA setting                                                                                                                                                                                   | 11             |

| •  | Changed Full-Scale Input section title to Full-Scale Range (FSR) and LSB Size, and updated section for clarity                                                                                                                                                         | 12             |

| •  | Added Voltage Reference and Oscillator sections                                                                                                                                                                                                                        | 12             |

| •  | Changed Comparator section title to Digital Comparator, and updated section for clarity.                                                                                                                                                                               | 12             |

| •  | Changed Conversion Ready Pin section for clarity                                                                                                                                                                                                                       | 14             |

| •  | Changed Register Map section for clarity                                                                                                                                                                                                                               | 22             |

| •  | Changed Application Information section for clarity                                                                                                                                                                                                                    | 26             |

| •  | Added Input Protection section                                                                                                                                                                                                                                         | 27             |

| •  | Added Unused Inputs and Outputs section                                                                                                                                                                                                                                | 27             |

| •  | Changed Aliasing section title to Analog Input Filtering and updated section for clarity                                                                                                                                                                               | 28             |

| •  | Added Typical Application section                                                                                                                                                                                                                                      | 31             |

| Cł | nanges from Revision B (September 2009) to Revision C                                                                                                                                                                                                                  | Page           |

| •  | 已删除 从特性部分删除了工作温度项目符号                                                                                                                                                                                                                                                   | 1              |

| •  | Deleted Operating temperature range parameter from Absolute Maximum Ratings table                                                                                                                                                                                      |                |

| •  | Deleted Operating temperature parameter from Temperature subsection of Electrical Characteristics table                                                                                                                                                                |                |

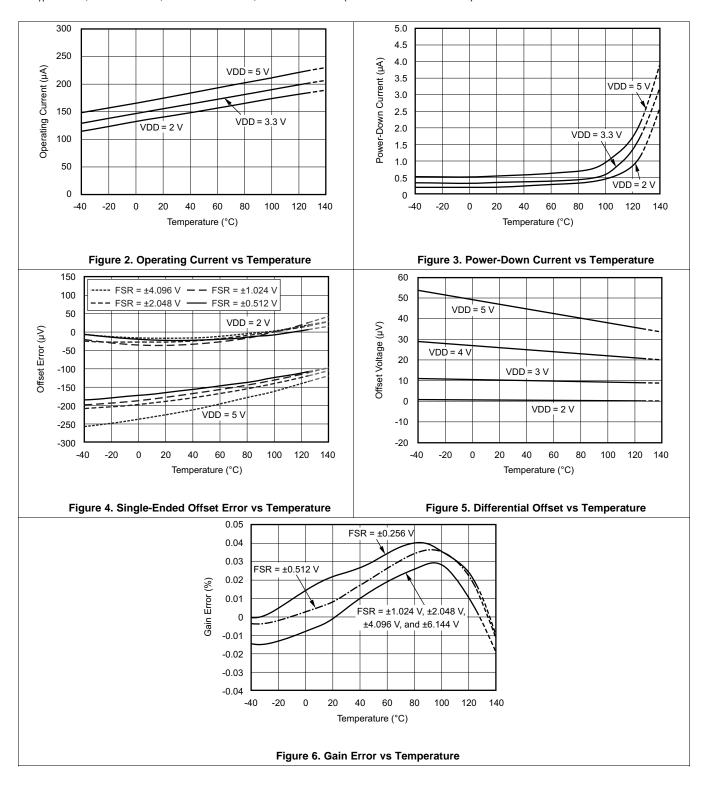

| •  | Changed Figure 2 to reflect maximum operating temperature                                                                                                                                                                                                              |                |

| •  | Changed Figure 3 to reflect maximum operating temperature                                                                                                                                                                                                              |                |

|    |                                                                                                                                                                                                                                                                        |                |

# ADS1013, ADS1014, ADS1015

| ZHCSHA6E - N | 11 V 2000 | DEVICED    | IANIIIADV | 2010 |

|--------------|-----------|------------|-----------|------|

| ZロしるロADE ー!  | VIATZUUS- | -KEVIOED : | JANUART   | 2010 |

www.ti.com.cn

| • | Changed Figure 4 to reflect maximum operating temperature | 8 |

|---|-----------------------------------------------------------|---|

| • | Changed Figure 5 to reflect maximum operating temperature | 8 |

| • | Changed Figure 6 to reflect maximum operating temperature | 8 |

# 5 Device Comparison Table

| DEVICE  | RESOLUTION<br>(Bits) | MAXIMUM SAMPLE<br>RATE<br>(SPS) | INPUT CHANNELS<br>Differential<br>(Single-Ended) | PGA | INTERFACE        | SPECIAL<br>FEATURES |

|---------|----------------------|---------------------------------|--------------------------------------------------|-----|------------------|---------------------|

| ADS1015 | 12                   | 3300                            | 2 (4)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1014 | 12                   | 3300                            | 1 (1)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1013 | 12                   | 3300                            | 1 (1)                                            | No  | I <sup>2</sup> C | None                |

| ADS1115 | 16                   | 860                             | 2 (4)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1114 | 16                   | 860                             | 1 (1)                                            | Yes | I <sup>2</sup> C | Comparator          |

| ADS1113 | 16                   | 860                             | 1(1)                                             | No  | I <sup>2</sup> C | None                |

| ADS1018 | 12                   | 3300                            | 2 (4)                                            | Yes | SPI              | Temperature sensor  |

| ADS1118 | 16                   | 860                             | 2 (4)                                            | Yes | SPI              | Temperature sensor  |

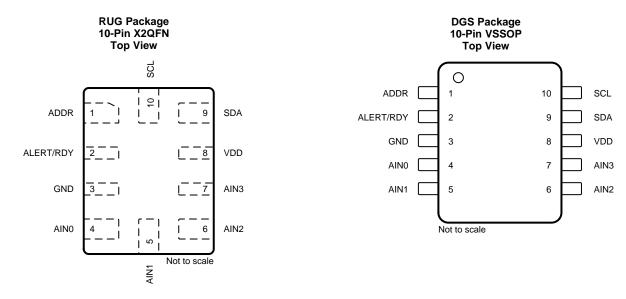

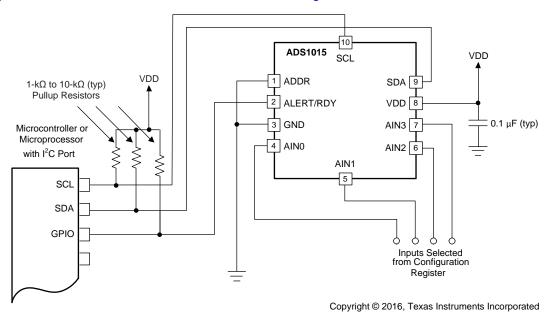

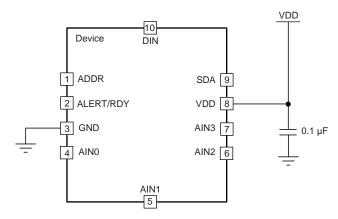

# 6 Pin Configuration and Functions

#### **Pin Functions**

|           | PI      | IN <sup>(1)</sup> |         |                |                                                                           |  |

|-----------|---------|-------------------|---------|----------------|---------------------------------------------------------------------------|--|

| NAME      | ADS1013 | ADS1014           | ADS1015 | TYPE           | DESCRIPTION                                                               |  |

| ADDR      | 1       | 1                 | 1       | Digital input  | I <sup>2</sup> C slave address select                                     |  |

| AIN0      | 4       | 4                 | 4       | Analog input   | Analog input 0                                                            |  |

| AIN1      | 5       | 5                 | 5       | Analog input   | Analog input 1                                                            |  |

| AIN2      | _       | _                 | 6       | Analog input   | Analog input 2 (ADS1015 only)                                             |  |

| AIN3      | _       | _                 | 7       | Analog input   | Analog input 3 (ADS1015 only)                                             |  |

| ALERT/RDY | _       | 2                 | 2       | Digital output | Comparator output or conversion ready (ADS1014 and ADS1015 only)          |  |

| GND       | 3       | 3                 | 3       | Analog         | Ground                                                                    |  |

| NC        | 2, 6, 7 | 6, 7              | _       | _              | Not connected                                                             |  |

| SCL       | 10      | 10                | 10      | Digital input  | Serial clock input. Clocks data on SDA                                    |  |

| SDA       | 9       | 9                 | 9       | Digital I/O    | Serial data. Transmits and receives data                                  |  |

| VDD       | 8       | 8                 | 8       | Analog         | Power supply. Connect a 0.1-μF, power-supply decoupling capacitor to GND. |  |

<sup>(1)</sup> See the *Unused Inputs and Outputs* section for unused pin connections.

# 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                           |                                   | MIN       | MAX       | UNIT |

|---------------------------|-----------------------------------|-----------|-----------|------|

| Power-supply voltage      | VDD to GND                        | -0.3      | 7         | V    |

| Analog input voltage      | AINO, AIN1, AIN2, AIN3            | GND - 0.3 | VDD + 0.3 | V    |

| Digital input voltage     | SDA, SCL, ADDR, ALERT/RDY         | GND - 0.3 | 5.5       | V    |

| Input current, continuous | Any pin except power supply pins  | -10       | 10        | mA   |

|                           | Operating ambient, T <sub>A</sub> | -40       | 125       |      |

| Temperature               | Junction, T <sub>J</sub>          | -40       | 150       | °C   |

|                           | Storage, T <sub>stg</sub>         | -60       | 150       |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                                            |                                                                     |       | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------------------|-------|-------|------|

| V <sub>(Fob)</sub> Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/    |      |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V     |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

|                     |                                                                                                   | MIN    | NOM MAX | UNIT |

|---------------------|---------------------------------------------------------------------------------------------------|--------|---------|------|

| POWER               | SUPPLY                                                                                            |        | ·       |      |

|                     | Power supply (VDD to GND)                                                                         | 2      | 5.5     | V    |

| ANALO               | G INPUTS <sup>(1)</sup>                                                                           |        | 1       |      |

| FSR                 | Full-scale input voltage range (2) (V <sub>IN</sub> = V <sub>(AINP)</sub> - V <sub>(AINN)</sub> ) | ±0.256 | ±6.144  | V    |

| V <sub>(AINx)</sub> | Absolute input voltage                                                                            | GND    | VDD     | V    |

| DIGITA              | INPUTS                                                                                            |        |         |      |

| $V_{DIG}$           | Digital input voltage                                                                             | GND    | 5.5     | V    |

| TEMPE               | RATURE                                                                                            |        |         |      |

| T <sub>A</sub>      | Operating ambient temperature                                                                     | -40    | 125     | °C   |

- (1) AINP and AINN denote the selected positive and negative inputs. AINx denotes one of the four available analog inputs.

- (2) This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V must be applied to the analog inputs of the device. See Table 1 more information.

# 7.4 Thermal Information

|                      |                                              | ADS         |             |      |

|----------------------|----------------------------------------------|-------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP) | RUG (X2QFN) | UNIT |

|                      |                                              | 10 PINS     | 10 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 182.7       | 245.2       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 67.2        | 69.3        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 103.8       | 172.0       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 10.2        | 8.2         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 102.1       | 170.8       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A         | N/A         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

At VDD = 3.3 V, data rate = 128 SPS, and full-scale input-voltage range (FSR) =  $\pm 2.048$  V (unless otherwise noted). Maximum and minimum specifications apply from  $T_A = -40^{\circ}$ C to  $\pm 125^{\circ}$ C. Typical specifications are at  $T_A = 25^{\circ}$ C.

|                 | PARAMETER                              | TEST CO                           | ONDITIONS                     | MIN            | TYP          | MAX       | UNIT     |

|-----------------|----------------------------------------|-----------------------------------|-------------------------------|----------------|--------------|-----------|----------|

| ANAL            | OG INPUT                               |                                   |                               |                |              |           |          |

|                 |                                        | FSR = ±6.144 V <sup>(1)</sup>     | )                             |                | 10           |           |          |

|                 | Occurred to the district to the second | FSR = ±4.096 V <sup>(1)</sup>     | , FSR = ±2.048 V              |                | 6            |           | 140      |

|                 | Common-mode input impedance            | FSR = ±1.024 V                    |                               |                | 3            |           | MΩ       |

|                 |                                        | FSR = ±0.512 V, F                 | FSR = ±0.256 V                |                | 100          |           |          |

|                 |                                        | FSR = ±6.144 V <sup>(1)</sup>     |                               |                | 22           |           |          |

|                 |                                        | FSR = ±4.096 V <sup>(1)</sup>     |                               |                | 15           |           |          |

|                 | Differential input impedance           | FSR = ±2.048 V                    |                               |                | 4.9          |           | MΩ       |

|                 |                                        | FSR = ±1.024 V                    |                               |                | 2.4          |           |          |

|                 |                                        | FSR = ±0.512 V, ±                 | ±0.256 V                      |                | 710          |           | kΩ       |

| SYSTE           | M PERFORMANCE                          | 1                                 |                               | I              |              |           |          |

|                 | Resolution (no missing codes)          |                                   |                               | 12             |              |           | Bits     |

| DR              | Data rate                              |                                   |                               | 128, 250, 490, | 920, 1600, 2 | 400, 3300 | SPS      |

|                 | Data rate variation                    | All data rates                    |                               | -10%           |              | 10%       |          |

| INL             | Integral nonlinearity                  | DR = 128 SPS, FS                  | SR = ±2.048 V <sup>(2)</sup>  |                |              | 0.5       | LSB      |

|                 | Official community                     | FSR = ±2.048 V, 0                 | differential inputs           | -0.5           | 0            | 0.5       | 1.00     |

|                 | Offset error                           | FSR = ±2.048 V, s                 | single-ended inputs           |                | ±0.25        |           | LSB      |

|                 | Offset drift over temperature          | FSR = ±2.048 V                    |                               |                | 0.005        |           | LSB/°C   |

|                 | Long-term offset drift                 | FSR = ±2.048 V, 7 hrs             | Γ <sub>A</sub> = 125°C, 1000  |                | ±1           |           | LSB      |

|                 | Offset channel match                   | Match between an                  | y two inputs                  |                | 0.25         |           | LSB      |

|                 | Gain error <sup>(3)</sup>              | FSR = ±2.048 V, 7                 | Γ <sub>A</sub> = 25°C         |                | 0.05%        | 0.25%     |          |

|                 |                                        | FSR = ±0.256 V                    |                               |                | 7            |           |          |

|                 | Gain drift over temperature (3)        | FSR = ±2.048 V                    |                               |                | 5            | 40        | ppm/°C   |

|                 |                                        | $FSR = \pm 6.144 \text{ V}^{(1)}$ | FSR = ±6.144 V <sup>(1)</sup> |                | 5            |           |          |

|                 | Long-term gain drift                   | FSR = ±2.048 V, 7 hrs             | Γ <sub>A</sub> = 125°C, 1000  |                | ±0.05        |           | %        |

|                 | Gain match <sup>(3)</sup>              | Match between an                  | y two gains                   |                | 0.02%        | 0.1%      |          |

|                 | Gain channel match                     | Match between an                  | y two inputs                  |                | 0.05%        | 0.1%      |          |

| DIGITA          | AL INPUT/OUTPUT                        |                                   |                               | 1              |              |           |          |

| V <sub>IH</sub> | High-level input voltage               |                                   |                               | 0.7 VDD        |              | VDD       | V        |

| V <sub>IL</sub> | Low-level input voltage                |                                   |                               | GND            |              | 0.3 VDD   | V        |

| V <sub>OL</sub> | Low-level output voltage               | I <sub>OL</sub> = 3 mA            |                               | GND            | 0.15         | 0.4       | V        |

|                 | Input leakage current                  | GND < V <sub>DIG</sub> < VD       | D                             | -10            |              | 10        | μΑ       |

| POWE            | R-SUPPLY                               |                                   |                               |                |              |           |          |

|                 |                                        | D                                 | T <sub>A</sub> = 25°C         |                | 0.5          | 2         |          |

|                 | Complex compact                        | Power-down                        |                               |                |              | 5         | ]<br>,., |

| $I_{VDD}$       | Supply current                         | Operating T <sub>A</sub> = 25°C   |                               |                | 150          | 200       | μA       |

|                 |                                        |                                   |                               |                |              | 300       |          |

|                 |                                        | VDD = 5.0 V                       |                               |                | 0.9          |           |          |

| $P_D$           | Power dissipation                      | VDD = 3.3 V                       |                               |                | 0.5          |           | mW       |

|                 |                                        | VDD = 2.0 V                       |                               |                | 0.3          |           |          |

<sup>(1)</sup> This parameter expresses the full-scale range of the ADC scaling. No more than VDD + 0.3 V must be applied to the analog inputs of the device. See Table 1 more information.

<sup>2)</sup> Best-fit INL; covers 99% of full-scale.

<sup>(3)</sup> Includes all errors from onboard PGA and voltage reference.

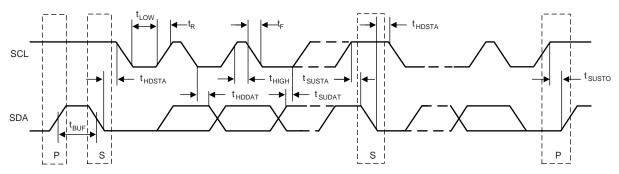

# 7.6 Timing Requirements: I<sup>2</sup>C

over operating ambient temperature range and VDD = 2.0 V to 5.5 V (unless otherwise noted)

|                    |                                                                                               | FAST MOI | FAST MODE |      | MODE |      |

|--------------------|-----------------------------------------------------------------------------------------------|----------|-----------|------|------|------|

|                    |                                                                                               | MIN      | MAX       | MIN  | MAX  | UNIT |

| f <sub>SCL</sub>   | SCL Clock Frequency                                                                           | 0.01     | 0.4       | 0.01 | 3.4  | MHz  |

| t <sub>BUF</sub>   | Bus free time between START and STOP condition                                                | 600      |           | 160  |      | ns   |

| t <sub>HDSTA</sub> | Hold time after repeated START condition.<br>After this period, the first clock is generated. | 600      |           | 160  |      | ns   |

| t <sub>SUSTA</sub> | Setup time for a repeated START condition                                                     | 600      |           | 160  |      | ns   |

| t <sub>SUSTO</sub> | Setup time for STOP condition                                                                 | 600      |           | 160  |      | ns   |

| t <sub>HDDAT</sub> | Data hold time                                                                                | 0        |           | 0    |      | ns   |

| t <sub>SUDAT</sub> | Data setup time                                                                               | 100      |           | 10   |      | ns   |

| $t_{LOW}$          | Low period of the SCL clock pin                                                               | 1300     |           | 160  |      | ns   |

| t <sub>HIGH</sub>  | High period for the SCL clock pin                                                             | 600      |           | 60   |      | ns   |

| t <sub>F</sub>     | Rise time for both SDA and SCL signals <sup>(1)</sup>                                         |          | 300       |      | 160  | ns   |

| t <sub>R</sub>     | Fall time for both SDA and SCL signals <sup>(1)</sup>                                         |          | 300       |      | 160  | ns   |

(1) For high-speed mode maximum values, the capacitive load on the bus line must not exceed 400 pF.

Figure 1. I<sup>2</sup>C Interface Timing

# 7.7 Typical Characteristics

at T<sub>A</sub> = 25°C, VDD = 3.3 V, FSR = ±2.048 V, DR = 128 SPS (unless otherwise noted)

# 8 Detailed Description

#### 8.1 Overview

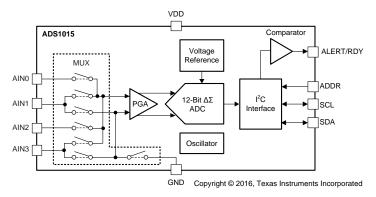

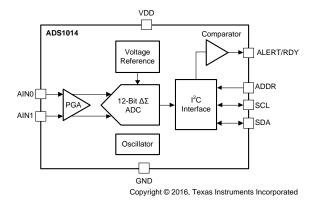

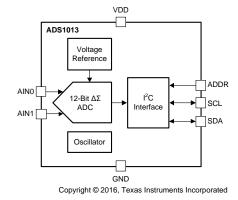

The ADS101x are very small, low-power, noise-free, 12-bit, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters (ADCs). The ADS101x consist of a  $\Delta\Sigma$  ADC core with an internal voltage reference, a clock oscillator and an I<sup>2</sup>C interface. The ADS1014 and ADS1015 also integrate a programmable gain amplifier (PGA) and a programmable digital comparator. Figure 7, Figure 8, and Figure 9 show the functional block diagrams of ADS1015, ADS1014, and ADS1013, respectively.

The ADS101x ADC core measures a differential signal,  $V_{IN}$ , that is the difference of  $V_{(AINP)}$  and  $V_{(AINN)}$ . The converter core consists of a differential, switched-capacitor  $\Delta\Sigma$  modulator followed by a digital filter. This architecture results in a very strong attenuation of any common-mode signals. Input signals are compared to the internal voltage reference. The digital filter receives a high-speed bitstream from the modulator and outputs a code proportional to the input voltage.

The ADS101x have two available conversion modes: single-shot and continuous-conversion. In single-shot mode, the ADC performs one conversion of the input signal upon request, stores the conversion value to an internal conversion register, and then enters a power-down state. This mode is intended to provide significant power savings in systems that only require periodic conversions or when there are long idle periods between conversions. In continuous-conversion mode, the ADC automatically begins a conversion of the input signal as soon as the previous conversion is completed. The rate of continuous conversion is equal to the programmed data rate. Data can be read at any time and always reflect the most recent completed conversion.

## 8.2 Functional Block Diagrams

Figure 7. ADS1015 Block Diagram

Figure 8. ADS1014 Block Diagram

Figure 9. ADS1013 Block Diagram

#### 8.3 Feature Description

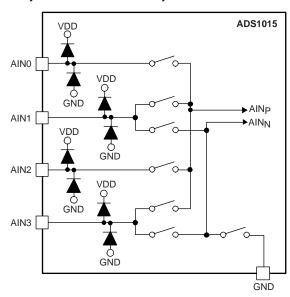

# 8.3.1 Multiplexer

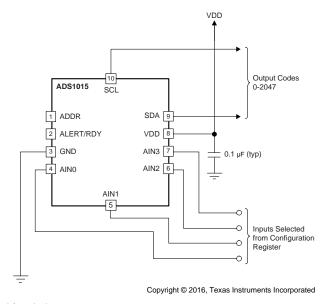

The ADS1015 contains an input multiplexer (MUX), as shown in Figure 10. Either four single-ended or two differential signals can be measured. Additionally, AINO and AIN1 may be measured differentially to AIN3. The multiplexer is configured by bits MUX[2:0] in the Config register. When single-ended signals are measured, the negative input of the ADC is internally connected to GND by a switch within the multiplexer.

Copyright © 2016, Texas Instruments Incorporated

Figure 10. Input Multiplexer

The ADS1013 and ADS1014 do not have an input multiplexer and can measure either one differential signal or one single-ended signal. For single-ended measurements, connect the AIN1 pin to GND externally. In subsequent sections of this data sheet, AIN<sub>P</sub> refers to AIN0 and AIN<sub>N</sub> refers to AIN1 for the ADS1013 and ADS1014.

Electrostatic discharge (ESD) diodes connected to VDD and GND protect the ADS101x analog inputs. Keep the absolute voltage of any input within the range shown in Equation 1 to prevent the ESD diodes from turning on.

$$GND - 0.3 \text{ V} < V_{(AINX)} < VDD + 0.3 \text{ V}$$

(1)

If the voltages on the input pins can potentially violate these conditions, use external Schottky diodes and series resistors to limit the input current to safe values (see the *Absolute Maximum Ratings* table).

# **Feature Description (continued)**

#### 8.3.2 Analog Inputs

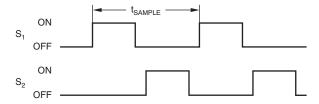

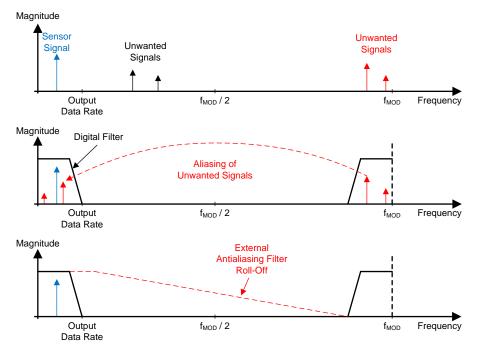

The ADS101x use a switched-capacitor input stage where capacitors are continuously charged and then discharged to measure the voltage between AIN<sub>P</sub> and AIN<sub>N</sub>. The frequency at which the input signal is sampled is called the sampling frequency or the modulator frequency ( $f_{MOD}$ ). The ADS101x has a 1-MHz internal oscillator that is further divided by a factor of 4 to generate  $f_{MOD}$  at 250 kHz. The capacitors used in this input stage are small, and to external circuitry, the average loading appears resistive. Figure 11 shows this structure. The capacitor values set the resistance and switching rate. Figure 12 shows the timing for the switches in Figure 11. During the sampling phase, switches  $S_1$  are closed. This event charges  $C_{A1}$  to  $V_{(AINP)}$ ,  $C_{A2}$  to  $V_{(AINN)}$ , and  $C_B$  to  $(V_{(AINP)} - V_{(AINN)})$ . During the discharge phase,  $S_1$  is first opened and then  $S_2$  is closed. Both  $C_{A1}$  and  $C_{A2}$  then discharge to approximately 0.7 V and  $C_B$  discharges to 0 V. This charging draws a very small transient current from the source driving the ADS101x analog inputs. The average value of this current can be used to calculate the effective impedance ( $Z_{eff}$ ), where  $Z_{eff} = V_{IN} / I_{AVERAGE}$ .

Figure 11. Simplified Analog Input Circuit

Figure 12. S<sub>1</sub> and S<sub>2</sub> Switch Timing

The common-mode input impedance is measured by applying a common-mode signal to the shorted  $AIN_P$  and  $AIN_N$  inputs and measuring the average current consumed by each pin. The common-mode input impedance changes depending on the full-scale range, but is approximately 6 M $\Omega$  for the default full-scale range. In Figure 11, the common-mode input impedance is  $Z_{CM}$ .

The differential input impedance is measured by applying a differential signal to  $AIN_P$  and  $AIN_N$  inputs where one input is held at 0.7 V. The current that flows through the pin connected to 0.7 V is the differential current and scales with the full-scale range. In Figure 11, the differential input impedance is  $Z_{DIFF}$ .

Make sure to consider the typical value of the input impedance. Unless the input source has a low impedance, the ADS101x input impedance may affect the measurement accuracy. For sources with high-output impedance, buffering may be necessary. Active buffers introduce noise, and also introduce offset and gain errors. Consider all of these factors in high-accuracy applications.

The clock oscillator frequency drifts slightly with temperature; therefore, the input impedances also drift. For most applications, this input impedance drift is negligible, and can be ignored.

# **Feature Description (continued)**

#### 8.3.3 Full-Scale Range (FSR) and LSB Size

A programmable gain amplifier (PGA) is implemented before the  $\Delta\Sigma$  ADC of the ADS1014 and ADS1015. The full-scale range is configured by bits PGA[2:0] in the Config register and can be set to  $\pm 6.144$  V,  $\pm 4.096$  V,  $\pm 2.048$  V,  $\pm 1.024$  V,  $\pm 0.512$  V,  $\pm 0.256$  V. Table 1 shows the FSR together with the corresponding LSB size. Equation 2 shows how to calculate the LSB size from the selected full-scale range.

$LSB = FSR / 2^{12}$  (2)

Table 1. Full-Scale Range and Corresponding LSB Size

| FSR                     | LSB SIZE |

|-------------------------|----------|

| ±6.144 V <sup>(1)</sup> | 3 mV     |

| ±4.096 V <sup>(1)</sup> | 2 mV     |

| ±2.048 V                | 1 mV     |

| ±1.024 V                | 0.5 mV   |

| ±0.512 V                | 0.25 mV  |

| ±0.256 V                | 0.125 mV |

<sup>(1)</sup> This parameter expresses the full-scale range of the ADC scaling. Do not apply more than VDD + 0.3 V to the analog inputs of the device

The FSR of the ADS1013 is fixed at ±2.048 V.

Analog input voltages must never exceed the analog input voltage limits given in the *Absolute Maximum Ratings*. If a VDD supply voltage greater than 4 V is used, the  $\pm 6.144$  V full-scale range allows input voltages to extend up to the supply. Although in this case (or whenever the supply voltage is less than the full-scale range, a full-scale ADC output code cannot be obtained. For example, with VDD = 3.3 V and FSR =  $\pm 4.096$  V, only signals up to  $V_{IN} = \pm 3.3$  V can be measured. The code range that represents voltages  $|V_{IN}| > 3.3$  V is not used in this case.

#### 8.3.4 Voltage Reference

The ADS101x have an integrated voltage reference. An external reference cannot be used with these devices. Errors associated with the initial voltage reference accuracy and the reference drift with temperature are included in the gain error and gain drift specifications in the *Electrical Characteristics* table.

#### 8.3.5 Oscillator

The ADS101x have an integrated oscillator running at 1 MHz. No external clock can be applied to operate these devices. The internal oscillator drifts over temperature and time. The output data rate scales proportionally with the oscillator frequency.

#### 8.3.6 Output Data Rate and Conversion Time

The ADS101x offer programmable output data rates. Use the DR[2:0] bits in the Config register to select output data rates of 128 SPS, 250 SPS, 490 SPS, 920 SPS, 1600 SPS, 2400 SPS, or 3300 SPS.

Conversions in the ADS101x settle within a single cycle; thus, the conversion time is equal to 1 / DR.

#### 8.3.7 Digital Comparator (ADS1014 and ADS1015 Only)

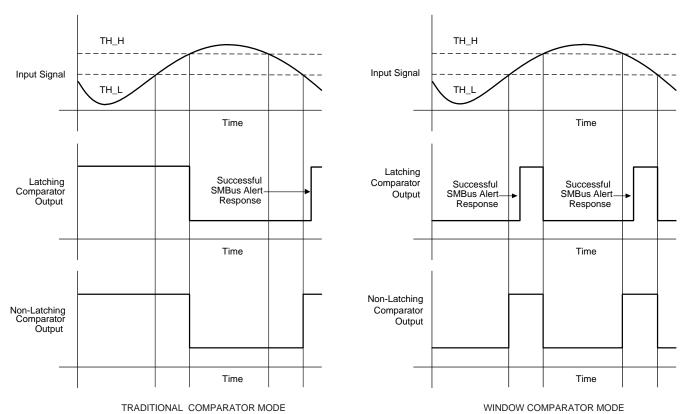

The ADS1015 and ADS1014 feature a programmable digital comparator that can issue an alert on the ALERT/RDY pin. The COMP\_MODE bit in the Config register configures the comparator as either a traditional comparator or a window comparator. In traditional comparator mode, the ALERT/RDY pin asserts (active low by default) when conversion data exceeds the limit set in the high-threshold register (Hi\_thresh). The comparator then deasserts only when the conversion data falls below the limit set in the low-threshold register (Lo\_thresh). In window comparator mode, the ALERT/RDY pin asserts when the conversion data exceed the Hi\_thresh register or fall below the Lo thresh register value.

In either window or traditional comparator mode, the comparator can be configured to latch after being asserted by the COMP\_LAT bit in the Config register. This setting causes the assertion to remain even if the input signal is not beyond the bounds of the threshold registers. This latched assertion can only be cleared by issuing an SMBus alert response or by reading the Conversion register. The ALERT/RDY pin can be configured as active high or active low by the COMP\_POL bit in the Config register. Operational diagrams for both the comparator modes are shown in Figure 13.

The comparator can also be configured to activate the ALERT/RDY pin only after a set number of successive readings exceed the threshold values set in the threshold registers (Hi\_thresh and Lo\_thresh). The COMP\_QUE[1:0] bits in the Config register configures the comparator to wait for one, two, or four readings beyond the threshold before activating the ALERT/RDY pin. The COMP\_QUE[1:0] bits can also disable the comparator function, and put the ALERT/RDY pin into a high state.

#### 8.3.8 Conversion Ready Pin (ADS1014 and ADS1015 Only)

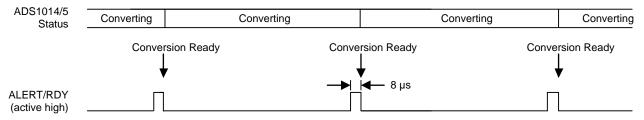

The ALERT/RDY pin can also be configured as a conversion ready pin. Set the most-significant bit of the Hi\_thresh register to 1 and the most-significant bit of Lo\_thresh register to 0 to enable the pin as a conversion ready pin. The COMP\_POL bit continues to function as expected. Set the COMP\_QUE[1:0] bits to any 2-bit value other than 11 to keep the ALERT/RDY pin enabled, and allow the conversion ready signal to appear at the ALERT/RDY pin output. The COMP\_MODE and COMP\_LAT bits no longer control any function. When configured as a conversion ready pin, ALERT/RDY continues to require a pullup resistor. The ADS101x provide an approximately 8-µs conversion ready pulse on the ALERT/RDY pin at the end of each conversion in continuous-conversion mode, as shown in Figure 14. In single-shot mode, the ALERT/RDY pin asserts low at the end of a conversion if the COMP\_POL bit is set to 0.

Figure 13. ALERT Pin Timing Diagram

Figure 14. Conversion Ready Pulse in Continuous-Conversion Mode

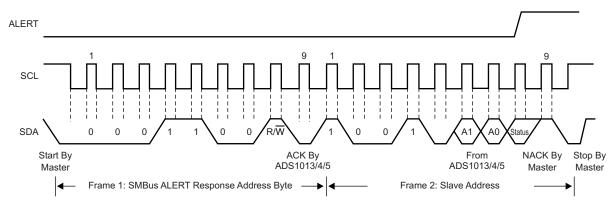

#### 8.3.9 SMbus Alert Response

In latching comparator mode (COMP\_LAT = 1), the ALERT/RDY pin asserts when the comparator detects a conversion that exceeds the upper or lower threshold value. This assertion is latched and can be cleared only by reading conversion data, or by issuing a successful SMBus alert response and reading the asserting device I<sup>2</sup>C address. If conversion data exceed the upper or lower threshold values after being cleared, the pin reasserts. This assertion does not affect conversions that are already in progress. The ALERT/RDY pin is an open-drain output. This architecture allows several devices to share the same interface bus. When disabled, the pin holds a high state so that the pin does not interfere with other devices on the same bus line.

When the master senses that the ALERT/RDY pin has latched, the master issues an SMBus alert command (00011001) to the I²C bus. Any ADS1014 and ADS1015 data converters on the I²C bus with the ALERT/RDY pins asserted respond to the command with the slave address. If more than one ADS101x on the I²C bus assert the latched ALERT/RDY pin, arbitration during the address response portion of the SMBus alert determines which device clears assertion. The device with the lowest I²C address always wins arbitration. If a device loses arbitration, the device does not clear the comparator output pin assertion. The master then repeats the SMBus alert response until all devices have the respective assertions cleared. In window comparator mode, the SMBus alert status bit indicates a 1 if signals exceed the high threshold, and a 0 if signals exceed the low threshold.

#### 8.4 Device Functional Modes

#### 8.4.1 Reset and Power-Up

The ADS101x reset on power-up and set all the bits in the Config register to the respective default settings. The ADS101x enter a power-down state after completion of the reset process. The device interface and digital blocks are active, but no data conversions are performed. The initial power-down state of the ADS101x relieves systems with tight power-supply requirements from encountering a surge during power-up.

The ADS101x respond to the I<sup>2</sup>C general-call reset command. When the ADS101x receive a general-call reset command (06h), an internal reset is performed as if the device is powered-up.

#### 8.4.2 Operating Modes

The ADS101x operate in one of two modes: continuous-conversion or single-shot. The MODE bit in the Config register selects the respective operating mode.

#### 8.4.2.1 Single-Shot Mode

When the MODE bit in the Config register is set to 1, the ADS101x enter a power-down state, and operate in single-shot mode. This power-down state is the default state for the ADS101x when power is first applied. Although powered down, the devices still respond to commands. The ADS101x remain in this power-down state until a 1 is written to the operational status (OS) bit in the Config register. When the OS bit is asserted, the device powers up in approximately 25  $\mu$ s, resets the OS bit to 0, and starts a single conversion. When conversion data are ready for retrieval, the device powers down again. Writing a 1 to the OS bit while a conversion is ongoing has no effect. To switch to continuous-conversion mode, write a 0 to the MODE bit in the Config register.

#### 8.4.2.2 Continuous-Conversion Mode

In continuous-conversion mode (MODE bit set to 0), the ADS101x perform conversions continuously. When a conversion is complete, the ADS101x place the result in the Conversion register and immediately begin another conversion. When writing new configuration settings, the currently ongoing conversion completes with the previous configuration settings. Thereafter, continuous conversions with the new configuration settings start. To switch to single-shot conversion mode, write a 1 to the MODE bit in the configuration register or reset the device.

#### 8.4.3 Duty Cycling For Low Power

The noise performance of a  $\Delta\Sigma$  ADC generally improves when lowering the output data rate because more samples of the internal modulator are averaged to yield one conversion result. In applications where power consumption is critical, the improved noise performance at low data rates may not be required. For these applications, the ADS101x support duty cycling that yield significant power savings by periodically requesting high data rate readings at an effectively lower data rate. For example, an ADS101x in power-down state with a data rate set to 3300 SPS can be operated by a microcontroller that instructs a single-shot conversion every 7.8 ms (128 SPS). A conversion at 3300 SPS only requires approximately 0.3 ms, so the ADS101x enter power-down state for the remaining 7.5 ms. In this configuration, the ADS101x consume approximately 1/25th the power that is otherwise consumed in continuous-conversion mode. The duty cycling rate is completely arbitrary and is defined by the master controller. The ADS101x offer lower data rates that do not implement duty cycling and also offer improved noise performance if required.

# 8.5 Programming

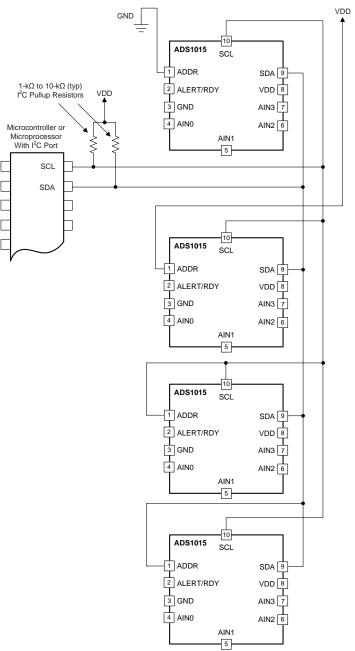

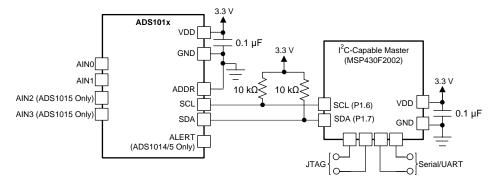

#### 8.5.1 I<sup>2</sup>C Interface

The ADS101x communicate through an I<sup>2</sup>C interface. I<sup>2</sup>C is a two-wire open-drain interface that supports multiple devices and masters on a single bus. Devices on the I<sup>2</sup>C bus only drive the bus lines low by connecting them to ground; the devices never drive the bus lines high. Instead, the bus wires are pulled high by pullup resistors, so the bus wires are always high when no device is driving them low. As a result of this configuration, two devices cannot conflict. If two devices drive the bus simultaneously, there is no driver contention.

Communication on the I<sup>2</sup>C bus always takes place between two devices, one acting as the master and the other as the slave. Both the master and slave can read and write, but the slave can only do so under the direction of the master. Some I<sup>2</sup>C devices can act as a master or slave, but the ADS101x can only act as a slave device.

An I<sup>2</sup>C bus consists of two lines: SDA and SCL. SDA carries data; SCL provides the clock. All data are transmitted across the I<sup>2</sup>C bus in groups of eight bits. To send a bit on the I<sup>2</sup>C bus, drive the SDA line to the appropriate level while SCL is low (a low on SDA indicates the bit is zero; a high indicates the bit is one). After the SDA line settles, the SCL line is brought high, then low. This pulse on SCL clocks the SDA bit into the receiver shift register. If the I<sup>2</sup>C bus is held idle for more than 25 ms, the bus times out.

The I<sup>2</sup>C bus is bidirectional; that is, the SDA line is used for both transmitting and receiving data. When the master reads from a slave, the slave drives the data line; when the master sends to a slave, the master drives the data line. The master always drives the clock line. The ADS101x cannot act as a master, and therefore can never drive SCL.

Most of the time the bus is idle; no communication occurs, and both lines are high. When communication takes place, the bus is active. Only a master device can start a communication and initiate a START condition on the bus. Normally, the data line is only allowed to change state while the clock line is low. If the data line changes state while the clock line is high, it is either a START condition or a STOP condition. A START condition occurs when the clock line is high, and the data line goes from high to low. A STOP condition occurs when the clock line is high, and the data line goes from low to high.

After the master issues a START condition, the master sends a byte that indicates with which slave device to communicate. This byte is called the *address byte*. Each device on an I<sup>2</sup>C bus has a unique 7-bit address to which it responds. The master sends an address in the address byte, together with a bit that indicates whether the master wishes to read from or write to the slave device.

Every byte (address and data) transmitted on the I<sup>2</sup>C bus is acknowledged with an *acknowledge* bit. When the master finishes sending a byte (eight data bits) to a slave, the master stops driving SDA and waits for the slave to acknowledge the byte. The slave acknowledges the byte by pulling SDA low. The master then sends a clock pulse to clock the acknowledge bit. Similarly, when the master completes reading a byte, the master pulls SDA low to acknowledge this completion to the slave. The master then sends a clock pulse to clock the bit. The master always drives the clock line.

If a device is not present on the bus, and the master attempts to address it, it receives a *not-acknowledge* because no device is present at that address to pull the line low. A not-acknowledge is performed by simply leaving SDA high during an acknowledge cycle.

When the master has finished communicating with a slave, it may issue a STOP condition. When a STOP condition is issued, the bus becomes idle again. The master may also issue another START condition. When a START condition is issued while the bus is active, it is called a repeated start condition.

The *Timing Requirements* section shows a timing diagram for the ADS101x I<sup>2</sup>C communication.

# **Programming (continued)**

#### 8.5.1.1 PC Address Selection

The ADS101x have one address pin, ADDR, that configures the I<sup>2</sup>C address of the device. This pin can be connected to GND, VDD, SDA, or SCL, allowing for four different addresses to be selected with one pin, as shown in Table 2. The state of address pin ADDR is sampled continuously. Use the GND, VDD and SCL addresses first. If SDA is used as the device address, hold the SDA line low for at least 100 ns after the SCL line goes low to make sure the device decodes the address correctly during I<sup>2</sup>C communication.

Table 2. ADDR Pin Connection and Corresponding Slave Address

| ADDR PIN CONNECTION | SLAVE ADDRESS |

|---------------------|---------------|

| GND                 | 1001000       |

| VDD                 | 1001001       |

| SDA                 | 1001010       |

| SCL                 | 1001011       |

#### 8.5.1.2 PC General Call

The ADS101x respond to the I<sup>2</sup>C general call address (0000000) if the eighth bit is 0. The devices acknowledge the general call address and respond to commands in the second byte. If the second byte is 00000110 (06h), the ADS101x reset the internal registers and enter a power-down state.

#### 8.5.1.3 PC Speed Modes

The I<sup>2</sup>C bus operates at one of three speeds. Standard mode allows a clock frequency of up to 100 kHz; fast mode permits a clock frequency of up to 400 kHz; and high-speed mode (also called Hs mode) allows a clock frequency of up to 3.4 MHz. The ADS101x are fully compatible with all three modes.

No special action is required to use the ADS101x in standard or fast mode, but high-speed mode must be activated. To activate high-speed mode, send a special address byte of 00001xxx following the START condition, where xxx are bits unique to the Hs-capable master. This byte is called the Hs master code, and is different from normal address bytes; the eighth bit does not indicate read/write status. The ADS101x do not acknowledge this byte; the I<sup>2</sup>C specification prohibits acknowledgment of the Hs master code. Upon receiving a master code, the ADS101x switch on Hs mode filters, and communicate at up to 3.4 MHz. The ADS101x switch out of Hs mode with the next STOP condition.

For more information on high-speed mode, consult the I<sup>2</sup>C specification.

#### 8.5.2 Slave Mode Operations

The ADS101x act as slave receivers or slave transmitters. The ADS101x cannot drive the SCL line as slave devices.

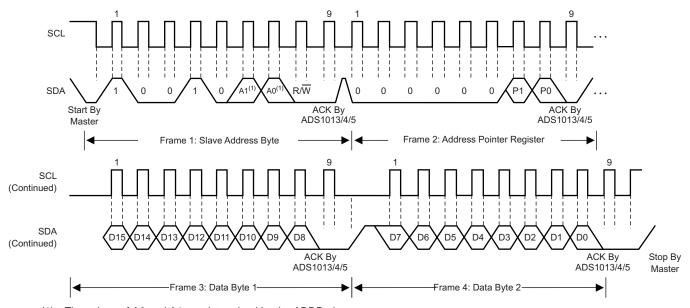

#### 8.5.2.1 Receive Mode

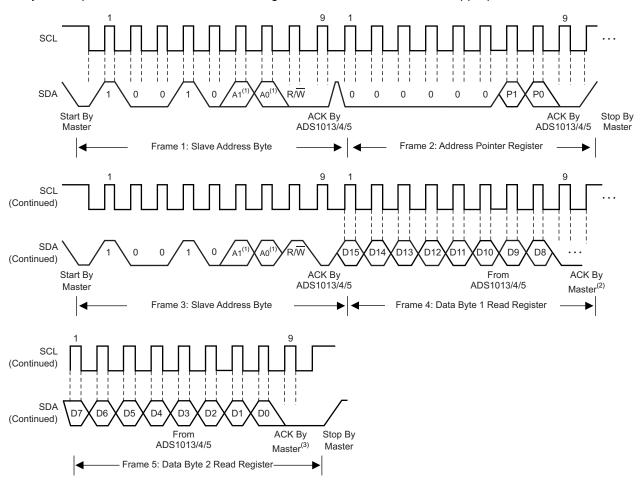

In slave receive mode, the first byte transmitted from the master to the slave consists of the 7-bit device address followed by a low R/W bit. The next byte transmitted by the master is the Address Pointer register. The ADS101x then acknowledge receipt of the Address Pointer register byte. The next two bytes are written to the address given by the register address pointer bits, P[1:0]. The ADS101x acknowledge each byte sent. Register bytes are sent with the most significant byte first, followed by the least significant byte.

#### 8.5.2.2 Transmit Mode

In slave transmit mode, the first byte transmitted by the master is the 7-bit slave address followed by the high R/W bit. This byte places the slave into transmit mode and indicates that the ADS101x are being read from. The next byte transmitted by the slave is the most significant byte of the register that is indicated by the register address pointer bits, P[1:0]. This byte is followed by an acknowledgment from the master. The remaining least significant byte is then sent by the slave and is followed by an acknowledgment from the master. The master may terminate transmission after any byte by not acknowledging or issuing a START or STOP condition.

#### 8.5.3 Writing To and Reading From the Registers

To access a specific register from the ADS101x, the master must first write an appropriate value to register address pointer bits P[1:0] in the Address Pointer register. The Address Pointer register is written to directly after the slave address byte, low  $R/\overline{W}$  bit, and a successful slave acknowledgment. After the Address Pointer register is written, the slave acknowledges, and the master issues a STOP or a repeated START condition.

When reading from the ADS101x, the previous value written to bits P[1:0] determines the register that is read. To change which register is read, a new value must be written to P[1:0]. To write a new value to P[1:0], the master issues a slave address byte with the R/W bit low, followed by the Address Pointer register byte. No additional data has to be transmitted, and a STOP condition can be issued by the master. The master can now issue a START condition and send the slave address byte with the R/W bit high to begin the read. Figure 22 details this sequence. If repeated reads from the same register are desired, there is no need to continually send the Address Pointer register, because the ADS101x store the value of P[1:0] until it is modified by a write operation. However, for every write operation, the Address Pointer register must be written with the appropriate values.

- (1) The values of A0 and A1 are determined by the ADDR pin.

- (2) Master can leave SDA high to terminate a single-byte read operation.

- (3) Master can leave SDA high to terminate a two-byte read operation.

Figure 15. Timing Diagram for Reading From ADS101x

(1) The values of A0 and A1 are determined by the ADDR pin.

Figure 16. Timing Diagram for Writing to ADS101x

(1) The values of A0 and A1 are determined by the ADDR pin.

Figure 17. Timing Diagram for SMBus Alert Response

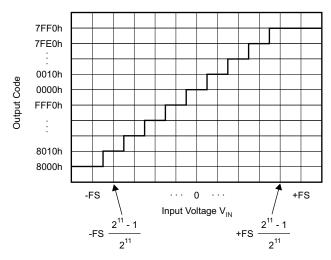

#### 8.5.4 Data Format

The ADS101x provide 12 bits of data in binary two's complement format that is left justified within the 16-bit data word. A positive full-scale (+FS) input produces an output code of 7FF0h and a negative full-scale (-FS) input produces an output code of 8000h. The output clips at these codes for signals that exceed full-scale. Table 3 summarizes the ideal output codes for different input signals. Figure 18 shows code transitions versus input voltage.

Table 3. Input Signal Versus Ideal Output Code

| INPUT SIGNAL V <sub>IN</sub> = (V <sub>AINP</sub> - V <sub>AINN</sub> ) | IDEAL OUTPUT CODE(1)(1) |

|-------------------------------------------------------------------------|-------------------------|

| ≥ +FS (2 <sup>11</sup> - 1)/2 <sup>11</sup>                             | 7FF0h                   |

| +FS/2 <sup>11</sup>                                                     | 0010h                   |

| 0                                                                       | 0000h                   |

| -FS/2 <sup>11</sup>                                                     | FFF0h                   |

| ≤ –FS                                                                   | 8000h                   |

(1) Excludes the effects of noise, INL, offset, and gain errors.

Figure 18. Code Transition Diagram

#### NOTE

Single-ended signal measurements, where  $V_{AINN} = 0 \text{ V}$  and  $V_{AINP} = 0 \text{ V}$  to +FS, only use the positive code range from 0000h to 7FF0h. However, because of device offset, the ADS101x can still output negative codes in case  $V_{AINP}$  is close to 0 V.

#### 8.6 Register Map

The ADS101x have four registers that are accessible through the I<sup>2</sup>C interface using the Address Pointer register. The Conversion register contains the result of the last conversion. The Config register is used to change the ADS101x operating modes and query the status of the device. The other two registers, Lo\_thresh and Hi\_thresh, set the threshold values used for the comparator function, and are not available in the ADS1013.

#### 8.6.1 Address Pointer Register (address = N/A) [reset = N/A]

All four registers are accessed by writing to the Address Pointer register; see Figure 15.

Figure 19. Address Pointer Register

| 7    | 6    | 5    | 4    | 3    | 2    | 1 0    |  |

|------|------|------|------|------|------|--------|--|

| 0    | 0    | 0    | 0    | 0    | 0    | P[1:0] |  |

| W-0h   |  |

LEGEND: R/W = Read/Write; R = Read only; W = Write only; -n = value after reset

#### **Table 4. Address Pointer Register Field Descriptions**

| Bit | Field    | Туре | Reset | Description                                                                                   |

|-----|----------|------|-------|-----------------------------------------------------------------------------------------------|

| 7:2 | Reserved | W    | 0h    | Always write 0h                                                                               |

| 1:0 | P[1:0]   | W    | 0h    | Register address pointer                                                                      |

|     |          |      |       | 00 : Conversion register 01 : Config register 10 : Lo_thresh register 11 : Hi_thresh register |

# 8.6.2 Conversion Register (P[1:0] = 0h) [reset = 0000h]

The 16-bit Conversion register contains the result of the last conversion in binary two's complement format. Following power-up, the Conversion register is cleared to 0, and remains 0 until the first conversion is completed.

Figure 20. Conversion Register

| 15   | 14   | 13   | 12   | 11       | 10   | 9    | 8    |

|------|------|------|------|----------|------|------|------|

| D11  | D10  | D9   | D8   | D7       | D6   | D5   | D4   |

| R-0h | R-0h | R-0h | R-0h | R-0h     | R-0h | R-0h | R-0h |

| 7    | 6    | 5    | 4    | 3        | 2    | 1    | 0    |

| D3   | D2   | D1   | D0   | Reserved |      |      |      |

| R-0h | R-0h | R-0h | R-0h | R-0h     | R-0h | R-0h | R-0h |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Table 5. Conversion Register Field Descriptions

| Bit  | Field    | Туре | Reset | Description              |

|------|----------|------|-------|--------------------------|

| 15:4 | D[11:0]  | R    | 000h  | 12-bit conversion result |

| 3:0  | Reserved | R    | 0h    | Always Reads back 0h     |

# 8.6.3 Config Register (P[1:0] = 1h) [reset = 8583h]

The 16-bit Config register is used to control the operating mode, input selection, data rate, full-scale range, and comparator modes.

Figure 21. Config Register

| 15            | 14                | 13     | 12     | 11       | 10       | 9      | 8        |

|---------------|-------------------|--------|--------|----------|----------|--------|----------|

| os            | MUX[2:0]          |        |        |          | PGA[2:0] |        | MODE     |

| R/W-1h        |                   | R/W-0h |        |          | R/W-2h   |        | R/W-1h   |

| 7             | 6 5               |        | 4      | 3        | 2        | 1      | 0        |

|               | DR[2:0] COMP_MODE |        |        | COMP_POL | COMP_LAT | COMP_0 | QUE[1:0] |

| R/W-4h R/W-0h |                   |        | R/W-0h | R/W-0h   | R/W-0h   | R/V    | /-3h     |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# **Table 6. Config Register Field Descriptions**

| Bit   | Field    | Type | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |          |      |       | Operational status or single-shot conversion start This bit determines the operational status of the device. OS can only be written when in power-down state and has no effect when a conversion is ongoing.                                                                                                                                                                                                                                                                                                                                                                           |

| 15    | os       | R/W  | 1h    | When writing: 0 : No effect 1 : Start a single conversion (when in power-down state) When reading: 0 : Device is currently performing a conversion 1 : Device is not currently performing a conversion                                                                                                                                                                                                                                                                                                                                                                                 |

|       |          |      |       | Input multiplexer configuration (ADS1015 only) These bits configure the input multiplexer. These bits serve no function on the ADS1013 and ADS1014.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14:12 | MUX[2:0] | R/W  | Oh    | $\begin{array}{l} 000: \text{AIN}_P = \text{AIN0 and AIN}_N = \text{AIN1 (default)} \\ 001: \text{AIN}_P = \text{AIN0 and AIN}_N = \text{AIN3} \\ 010: \text{AIN}_P = \text{AIN1 and AIN}_N = \text{AIN3} \\ 011: \text{AIN}_P = \text{AIN2 and AIN}_N = \text{AIN3} \\ 100: \text{AIN}_P = \text{AIN0 and AIN}_N = \text{GND} \\ 101: \text{AIN}_P = \text{AIN1 and AIN}_N = \text{GND} \\ 110: \text{AIN}_P = \text{AIN2 and AIN}_N = \text{GND} \\ 110: \text{AIN}_P = \text{AIN2 and AIN}_N = \text{GND} \\ 111: \text{AIN}_P = \text{AIN3 and AIN}_N = \text{GND} \\ \end{array}$ |

|       | PGA[2:0] | R/W  | 2h    | Programmable gain amplifier configuration These bits set the FSR of the programmable gain amplifier. These bits serve no function on the ADS1013.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11:9  |          |      |       | 000: FSR = ±6.144 V <sup>(1)</sup> 001: FSR = ±4.096 V <sup>(1)</sup> 010: FSR = ±2.048 V (default) 011: FSR = ±1.024 V 100: FSR = ±0.512 V 101: FSR = ±0.256 V 110: FSR = ±0.256 V                                                                                                                                                                                                                                                                                                                                                                                                    |

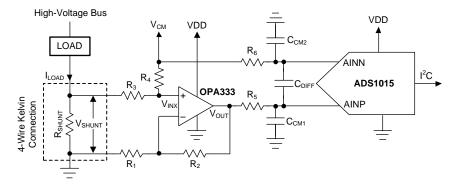

| 8     | MODE     | R/W  | 1h    | Device operating mode This bit controls the operating mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |