# UNISONIC TECHNOLOGIES CO., LTD

L8001 Preliminary CMOS IC

# FET BIAS CONTROLLER

#### DESCRIPTION

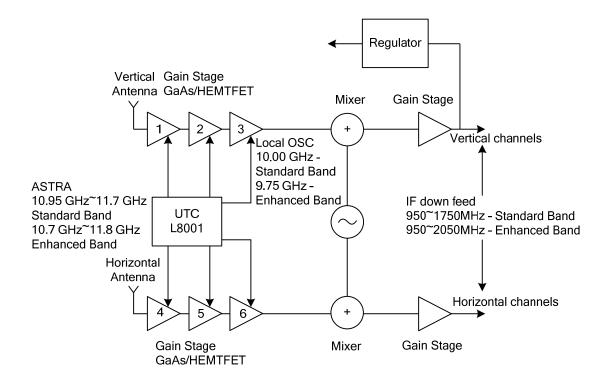

The UTC **L8001** is specially designed integrated circuit for satellite receiver front-end block. It provides stable drain and gate bias conditions for GaAs or HEMT FETs.

The UTC **L8001**, provide six FETs bias control respectively. By adjusting two external resistors, it can change the FET's bias current to optimize the satellite receiver front end block performances.

It generates the required negative voltage to bias the gate of GaAs FET, and internally provides protection circuit that can protect the FET devices during supply voltage transient. So it is very popular in satellite receiver front end block.

#### ■ FEATURES

- \* Built in FET device protection circuit

- \* Adjustable FET device operating current

- \* Stable bias control for GaAs and HEMT FETs

- \* Drive up to six FETs

- \* Wide supply voltage range

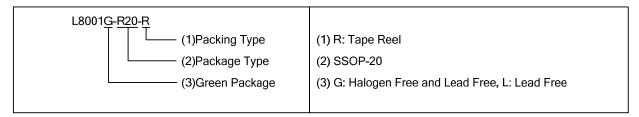

#### **■ ORDERING INFORMATION**

| Ordering     | Number       | Dookogo | Packing   |  |

|--------------|--------------|---------|-----------|--|

| Lead Free    | Halogen Free | Package |           |  |

| L8001L-R20-R | L8001G-R20-R | SSOP-20 | Tape Reel |  |

## **■** MARKING

www.unisonic.com.tw 1 of 6

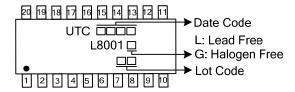

## ■ PIN CONFIGURATION

## **■ PIN DESCRIPTION**

| PIN NO. | PIN NAME        | DESCRIPTION                              |  |  |

|---------|-----------------|------------------------------------------|--|--|

| 1       | VD1             | 1 <sup>st</sup> Drain output voltage     |  |  |

| 2       | VG1             | 1 <sup>st</sup> Gate output voltage      |  |  |

| 3       | VD2             | 2 <sup>nd</sup> Drain output voltage     |  |  |

| 4       | VG2             | 2 <sup>nd</sup> Gate output voltage      |  |  |

| 5       | VG3             | 3 <sup>rd</sup> Gate output voltage      |  |  |

| 6       | VD3             | 3 <sup>rd</sup> Drain output voltage     |  |  |

| 7       | GND             | Ground                                   |  |  |

| 8       | NC              | No connect                               |  |  |

| 9       | CNB1            | OSC output                               |  |  |

| 10      | CNB2            | Rectifier Input                          |  |  |

| 11      | CSUB            | Negative voltage output                  |  |  |

| 12      | RCAL1           | VD1/VD2/VD3 current set resistor connect |  |  |

| 13      | RCAL2           | VD4/VD5/VD6 current set resistor connect |  |  |

| 14      | VG6             | 6 <sup>th</sup> Gate output voltage      |  |  |

| 15      | VD6             | 6 <sup>th</sup> Drain output voltage     |  |  |

| 16      | VG5             | 5 <sup>th</sup> Gate output voltage      |  |  |

| 17      | VD5             | 5 <sup>th</sup> Drain output voltage     |  |  |

| 18      | VG4             | 4 <sup>th</sup> Gate output voltage      |  |  |

| 19      | VD4             | 4 <sup>th</sup> Drain output voltage     |  |  |

| 20      | V <sub>CC</sub> | Supply voltage                           |  |  |

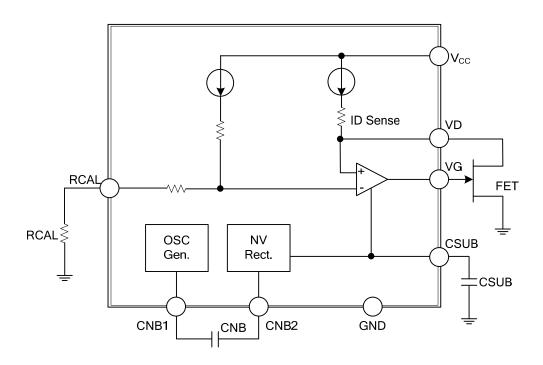

## **■ BLOCK DIAGRAM**

## ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                 | SYMBOL            | RATINGS   | UNIT |

|---------------------------|-------------------|-----------|------|

| Supply Voltage            | V <sub>CC</sub>   | -0.6 ~ 8  | V    |

| Supply Current            | Icc               | 100       | mA   |

| Maximum Drain Current     | I <sub>D</sub>    | 15        | mA   |

| Maximum CSUB Sink Current | I <sub>CSUB</sub> | -500      | uA   |

| Operating Temperature     | T <sub>OPR</sub>  | -40 ~ 80  | °C   |

| Storage Temperature       | T <sub>STG</sub>  | -50 ~ 150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

## **■ ELECTRICAL CHARACTERISTICS**

$(V_{\text{CC}}\text{=}3.3\text{V}, I_{\text{D}}\text{=}10\text{mA}, R_{\text{CAL1}}\text{=}8.2\text{K}\Omega, R_{\text{CAL2}}\text{=}8.2\text{K}\Omega, T_{\text{A}}\text{=}25^{\circ}\text{C}, unless otherwise stated})$

| PARAMETER                                 | SYMBOL          | TEST CONDITIONS                            | MIN  | TYP  | MAX  | UNIT     |

|-------------------------------------------|-----------------|--------------------------------------------|------|------|------|----------|

| Supply Voltage                            | $V_{CC}$        |                                            | 3.3  |      | 6    | V        |

| Supply Current                            | I <sub>CC</sub> | No FET                                     |      |      | 10   | mA       |

| Negative Voltage                          | $V_{SUB}$       | I <sub>SUB</sub> =0uA, V <sub>CC</sub> =6V | -3.0 | -2.5 | -1   | V        |

| Negative Voltage                          |                 | I <sub>SUB</sub> =-200uA                   |      |      | -1   | V        |

| Oscillator Freq.                          | $f_{O}$         |                                            | 200  | 350  | 800  | KHz      |

| Drain Current                             | $I_{D}$         |                                            | 8    | 10   | 12   | mA       |

| Drain Current Change with V <sub>CC</sub> | $\Delta I_{DV}$ | V <sub>CC</sub> =3.3~6V                    |      | 0.2  |      | %/V      |

| VD1/VD2/VD3/VD4/VD5/VD6 Drain             | ٨١              |                                            |      | 0.2  |      | m Λ      |

| Offset Current                            | $\Delta I_{DC}$ |                                            |      | 0.2  |      | mA       |

| Drain Current Change with Temp.           | $\Delta I_{DT}$ | T=-40~80°C                                 |      | 0.1  |      | %/°C     |

| Drain Voltage                             | $V_D$           | I <sub>D</sub> =10mA                       | 1.8  | 2    | 2.2  | V        |

| Drain Voltage Change with V <sub>CC</sub> | $\Delta V_{DV}$ | V <sub>CC</sub> =3.3~6V                    |      | 0.5  |      | %/V      |

| Drain Voltage Change                      | $\Delta V_{DT}$ | T=-40~80°C                                 |      | 50   |      | ppm      |

| Dynamic Gate Voltage Range                | $V_{G}$         | Csub without loading                       | -2.5 |      | 0.7  | V        |

| Drain Output Noise Voltage                | $V_{dn}$        | With drain bypass capacitor=10nF           |      |      | 0.05 | $V_{PP}$ |

| Gate Output Noise Voltage                 | $V_{GN}$        | With gate bypass capacitor=10nF            |      |      | 0.03 | $V_{PP}$ |

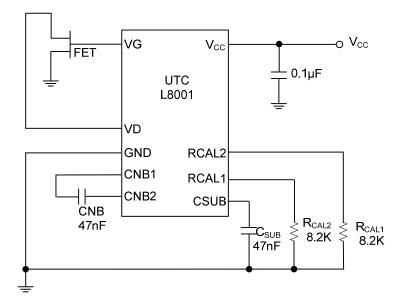

#### TYPICAL APPLICATION CIRCUIT

There are three major functions provided by L8001G: support negative voltage, bias control circuit, and FET protesting circuit.

The negative voltage is generated using internal oscillator. It only needs an ac coupled capacitor  $C_{NB}$  47nF and a negative voltage bypass capacitor  $C_{SUB}$  47nF.

The bias control circuit is used to establish a stable bias current for FETs. It's bias current can be adjusted by external resistor Rcal.Rcal1 resistor is used to set  $I_{D1}$ ,  $I_{D2}$ ,  $I_{D3}$  in L8001G. Rcal2 resistor is used to set  $I_{D4}$ ,  $I_{D5}$ ,  $I_{D6}$  in L8001G. if the same drain current is required for all FETs then pins Ical1 and Ical2 can be wired together and shunted to ground by a single resistor of half normal value.

The L8001G devices have been designed to protect the external FETs from adverse operating conditions. With a JFET connected to any bias circuit, the gate output voltage of the bias circuit can not exceed the range -2.5V to 0.7V, under any conditions including powerup and powerdown transients. Should the negative bias generator be shorted or overloaded so that the drain current of the external FETs can no longer be controlled, the drain supply to FETs is shut down to avoid damage to the FETs by excessive drain current. The following diagrams show the L8001G in typical LNB applications. Within each FET gain stage the numbering system indicates how the bias stages relate to the application circuits. This is important when RCAL values are used to set differing drain currents.

#### ■ TYPICAL APPLICATION CIRCUIT

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.